3, 4시리즈 제작

지난 포스트에 이어, NAND와 NOR 형제의 3, 4번째 시리즈를 제작한다. 이전 1번, 2번 포스트에서 진행한 과정과 동일하게 검증을 거쳤다.

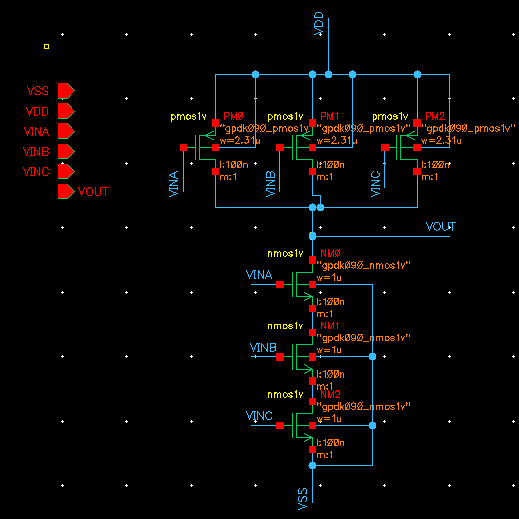

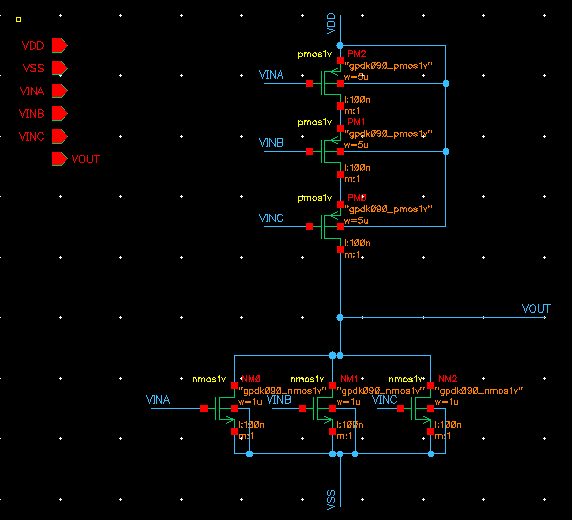

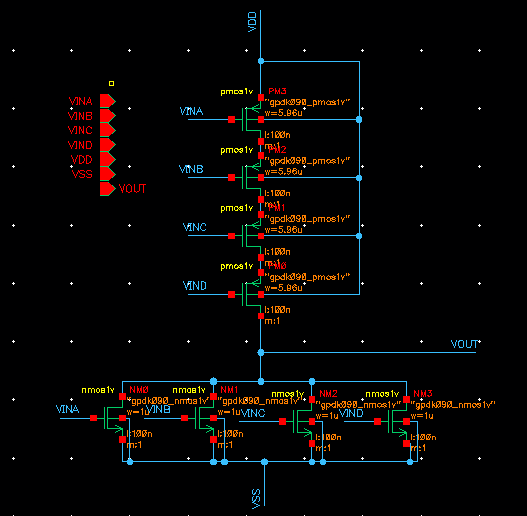

- schematic 파일을 생성하여 라이브러리에 추가한다. pMOS와 nMOS를 배치하고, nMOS의 Width(터미널의 너비)를 1µm로 기준삼아 pMOS의 값을 변수(WIDTH)로 두었다.

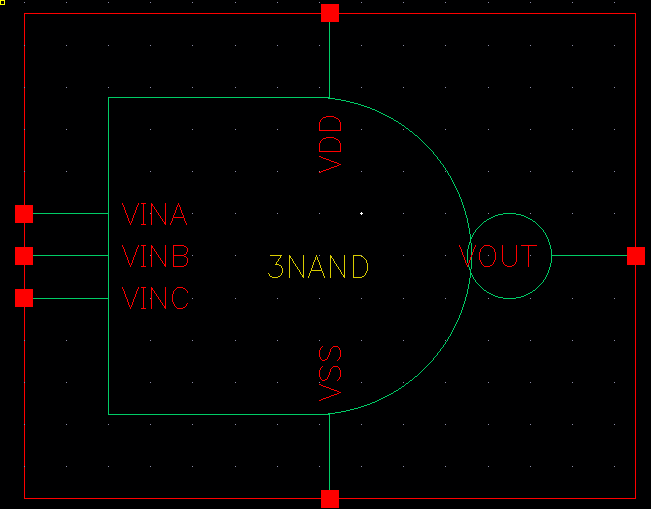

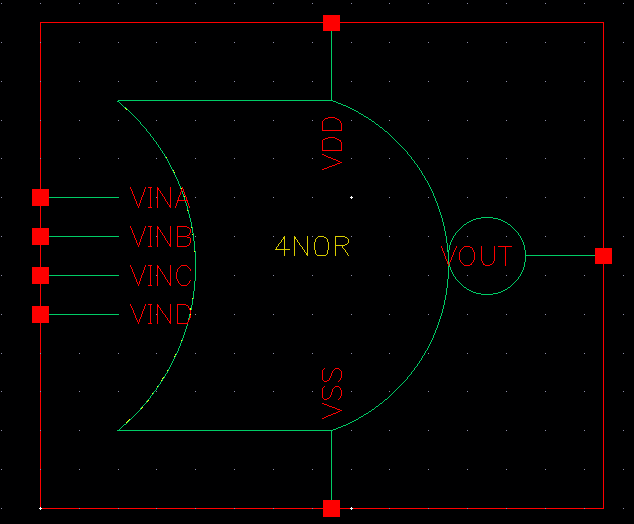

- Design Rule Check를 통해 schamatic의 문제를 모두 해결하고, cell view기능을 통해 symbol을 생성하여 게이트의 외장을 만든다.

- 두가지 파일을 모두 생성하여 라이브러리에 추가한 후, 새로 TEST 파일을 만든다. 이 파일은 직접 나의 라이브러리 아래에 생성한다. (schematic과 symbol 두 파일은 새로 생성한 NAND나 NOR 파일 밑에 작성된다.)

- TEST 파일에 symbol을 배치하고, 핀과 전원을 연결한 뒤 실험하여 pMOS의 값을 구한다.

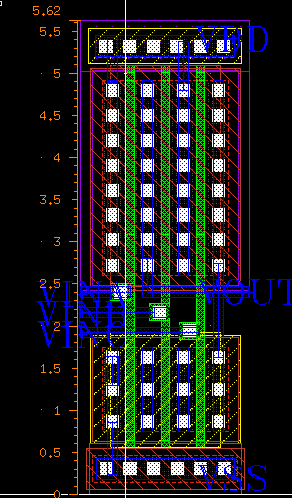

- 검증이 끝나면, schematic의 pMOS의 변수를 제거하고 구한 값을 대입한 후, layout 파일을 만든다.(주의할 점은 가장 최적화된, 즉 가장 낮은 높이를 가진 게이트를 만드는 것이 속도, 생산 단가를 낮추는 가장 중요한 점이라는 것을 명심하여야 한다.)

- layout의 모든 error를 제거하면, 게이트의 완성이 끝났다. 축하한다. 당신의 라이브러리에 실제 물성과 전기적 특성을 갖춘 게이트 파일이 추가되었다.

이러한 복잡한 과정을 대부분 1시간 안에 끝내야 한다. 툴을 배우면서 게이트를 완성하는 것은 재밌지만, 생각보다 고된 일이었다. 다음은 완성한 게이트들의 목록이다.

3시리즈

3NAND

-

3NAND schematic

-

3NAND symbol

-

3NAND layout

3NOR

-

3NOR schematic

-

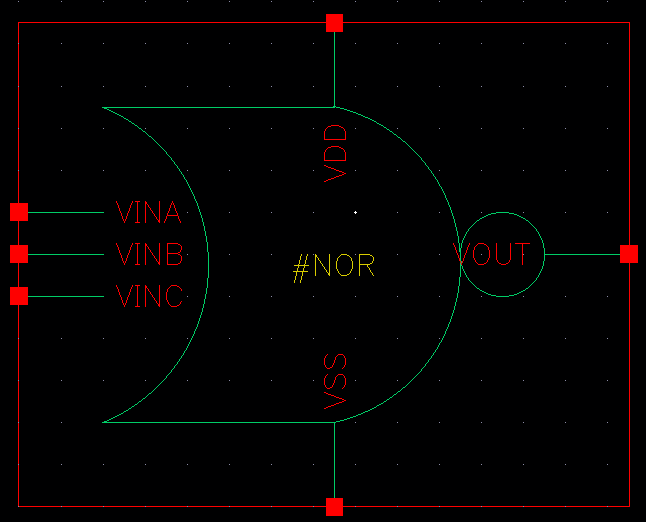

3NOR symbol

-

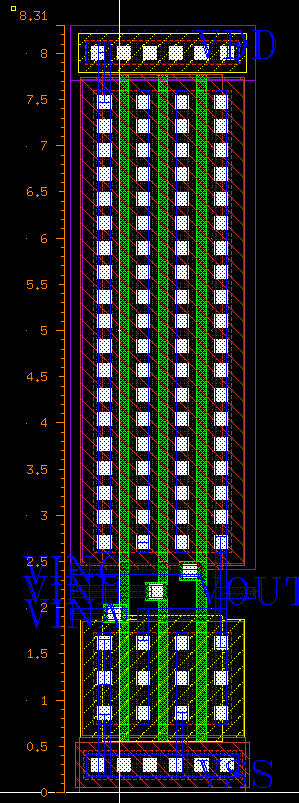

3NOR layout

4시리즈

4NAND

-

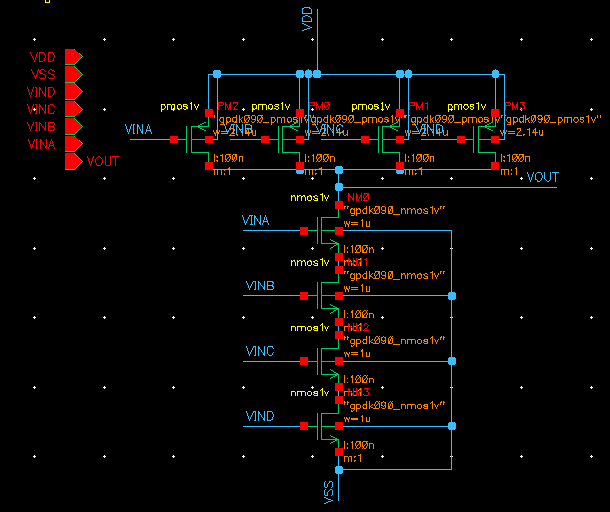

4NAND schematic

-

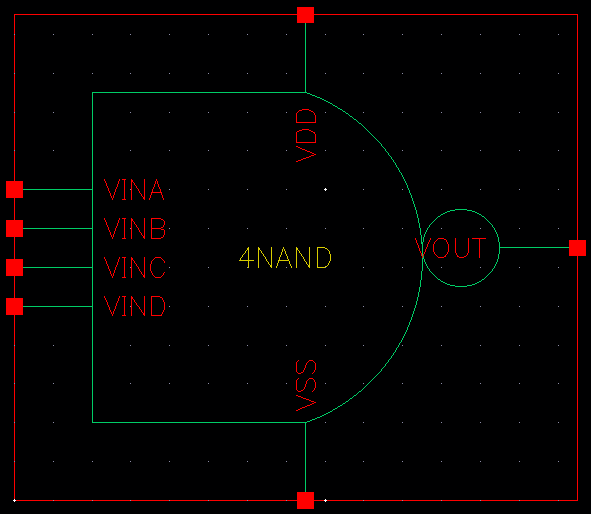

4NAND symbol

-

4NAND layout

4NOR

-

4NOR schematic

-

4NOR symbol

-

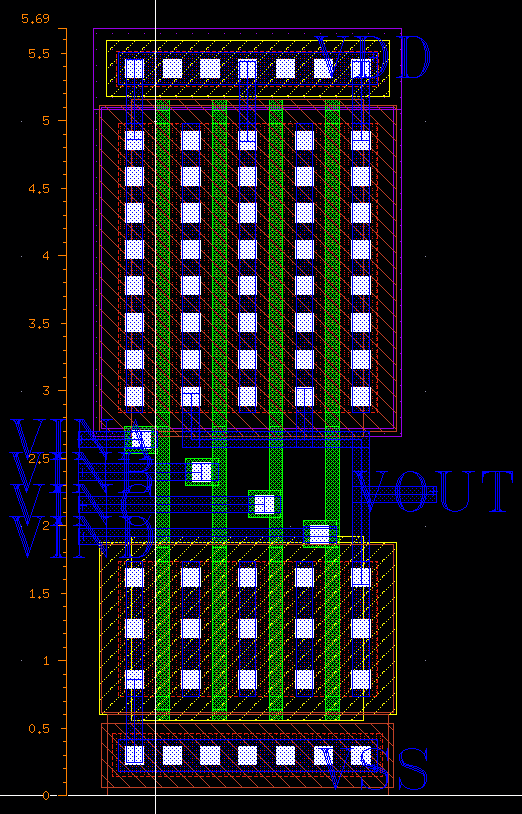

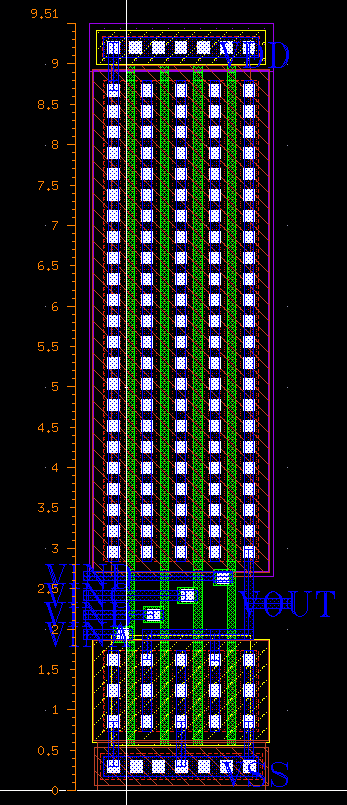

4NOR layout

이 표를 보시오

- length : 100nm //2시리즈까지 포함된 게이트의 베타값과 높이의 표

| 게이트의 종류 | WIDTH(beta) | gate's height | pMOSFET개수 |

|---|---|---|---|

| 2NAND | 2.53µm | 5.60µm | 2 |

| 3NAND | 2.31µm | 5.92µm | 3 |

| 4NAND | 2.14µm | 5.69µm | 4 |

| 2NOR | 3.97µm | 7.06µm | 2 |

| 3NOR | 5.00µm | 8.31µm | 3 |

| 4NOR | 5.96µm | 9.51µm | 4 |

- beta값은 nMOS W: pMOS W = 1 : beta

- height값은 Nwall + 1개의 pMOS W + 1개의 nMOS W + PSUB를 연결한 높이

표를 보면, 어떤 사실을 발견할 수 있지 않은가? pMOS의 숫자가 증가할수록, WIDTH가 증가하는 경향을 보이며, (높이)(MOSFET개수 -1) = TOTAL WIDTH이다. TW과 W(beta)의 차이점은 pMOSFET의 개수만큼 W(beta)를 곱하면 pMOS의 총 높이 TW이 되며, (nMOSFET의 개수)(1)이 nMOS의 TW가 된다.

또한 NAND는 입력 FET이 증가할수록 점점 beta값이 낮아지고, NOR은 점점 증가하는 것을 알 수 있다. 왜냐하면, nMOS와 pMOS는 각각 전달자가 electron과 hole인데, 이때 전압을 주면 pMOS의 상태와 nMOS의 상태는 반대를 이루게 된다.

4NAND와 4NOR의 예를 들어보면 4NAND는 pMOS가 병렬로 연결된 것을 알 수 있다. 이 경우, pMOS 중 하나라도 ON 된다면 4NAND는 output이 1이기 때문에, 전체 저항은 pMOS 하나의 저항과 같다. 이 수치를 R이라고 하자. 반대로, 4NOR은 직렬로 pMOS가 연결되어 있다. 이 경우, pMOS가 모조리 ON 되어야 output이 1을 출력한다. 따라서 전체저항 R은 부분저항 R/4로 나뉘게 된다. 다음의 아주 간략화된 공식을 참고해보자.

W/L = I = V/R

즉, 저항은 WiDTH에 반비례하므로 저항이 줄어들면 줄수록 WIDTH값이 표와 같이 늘어남을 알 수 있다.