Verilong HDL

하드웨어 기술언어인 HiLo와 C언어의 특징을 기반으로 개발된 Gateway Design Automatic사의 언어이다. 반도체 및 전자설계 산업에서 전자 시스템을 모델링하기 위한 대표적인 언어이다.

C언어와의 유사점이 그중 가장 특징적인데, 문법과 절차/순차적 실행은 동일하다. 또한 조건문과 연산자도 공유하기에 프로그래밍을 조금이라도 해 본 사용자는 베릴로그를 접하는 것이 어렵지 않을 것이다.

그러나, 중요한 차이점이 존재하는데, C언어를 필두로 한 프로그래밍 언어들은 병렬성/동시성을 가지지 않는다.

즉, 다른 줄의 구문을 동시에, 병렬적으로 동시 연산을 할 수 있다는 뜻이므로 주의하여야 한다.

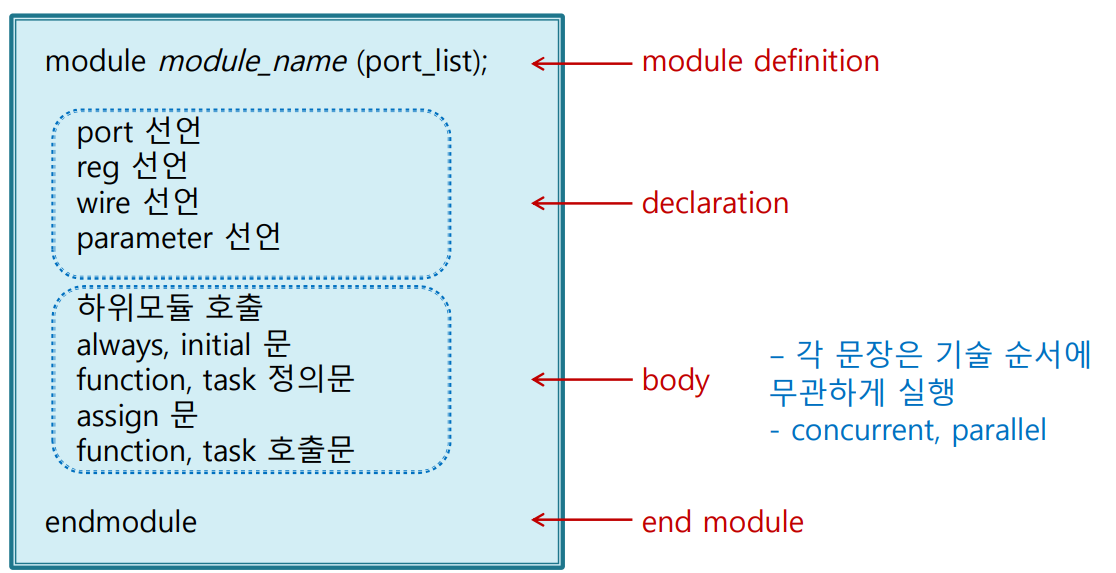

verilog 언어구조

verilog는 모듈구조로 설계되어 사용자가 만들어 놓은 모듈을 호출하여 사용할 수 있다. 이런 구조도 C++ 언어의 클래스 구조와 유사하다고 할 수 있다.

모듈의 구조는 크게 3부분으로 나눌 수 있다.

- 모듈의 base부인 모듈의 제목에는 변수를 추가로 써 주어야 한다. C언어의 함수 생성과도 일치하는 맥락이다.

- 두번째로 declaration 부분에는 변수의 형식을 포함하여 선언해주어야 한다.

- 마지막 body 부분에서는 하위모듈, 이미 정의되었거나 내가 정의했었던 정의문 등을 가져와서 연산하는 주요 기능 부분이다.

*주의할 점은 반드시 모듈의 끝에 end module을 사용하여 모듈의 종료를 선언해주어야 함

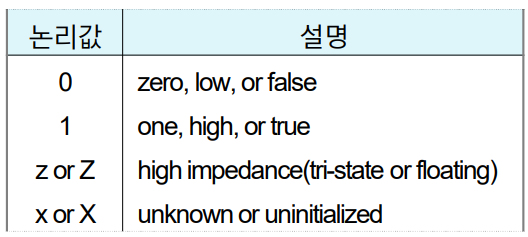

논리값

- 논리값 0 : 낮은 전위값, 디지털 비트 0, 또는 조건이 거짓을 의미한다.

- 논리값 1 : 높은 전위값, 디지털 비트 1, 또는 조건이 참을 의미한다.

- 논리값 Z : 높은 임피던스. Open Circuit 상태. NULL값이라고 비유할 수도 있지만 정확하지는 않다.

- 논리값 X : 알려지지 않거나, 정의되지 않은 상태. ERROR또는 모르겠음이라는 뜻.

정수 표현

정수를 표현하고자 할 때, verilog에서는 다음과 같은 형식을 지켜야 한다.

[size_constant]'<base_format> <number_value>

- [size_constant]' : 값의 비트 크기를 나타내는 상수

- <base_format> : base수를 나타내기 위한 문자.(d, D, h, H, o, O, b, B)를 사용 가능하며, signde를 나타내기 위해 s를 추가하여 사용 가능.

- <number_value> : <base_format>의 형식의 숫자

| 문자 | 진수 |

|---|---|

| d | 10 |

| h | 16 |

| o | 8 |

| b | 2 |

| sx | 부호가 있다는 표현. MSB가 부호의 역할을 함. |

| 없음 | 32 |

ex)8'd63 = 0011_1111

ex)5'h4F = 1_1111

*5비트 공간이므로 MSB가 5자리에 위치함. 6번 1 은 짤림.

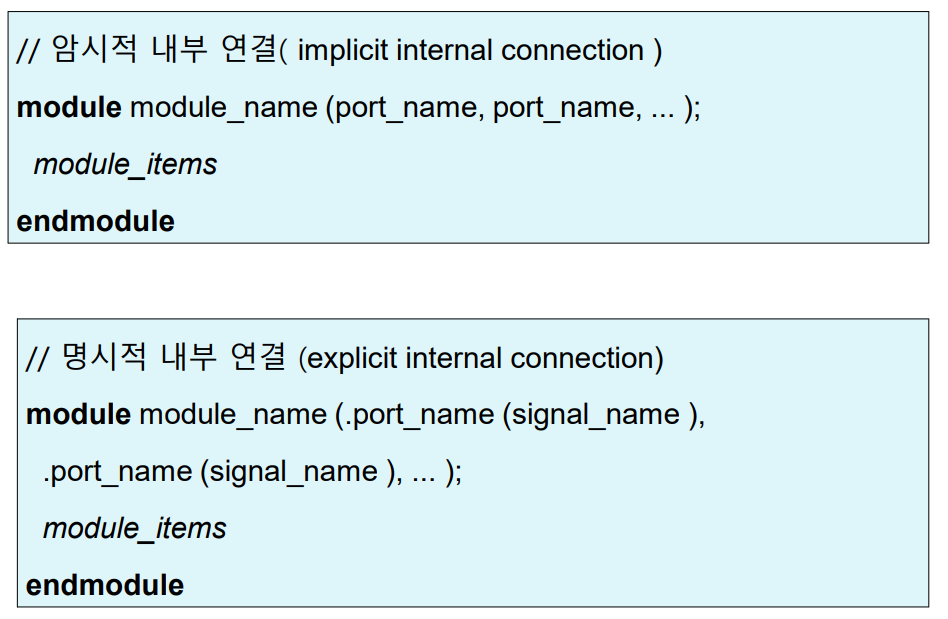

암시적? 명시적? 모듈 정의

이번 포스트를 작성하면서 가장 이해하기 난해했던 부분인데, 요약하자면 다음과 같다.

우리가 프로그램을 작성할 때, 상수를 입력하면 모듈 부분에서 컴퓨터가 암시적으로 모듈 네임 끝의 포트 네임을 보고 상수를 연관짓는다. 그러나 엄밀하게 상수와 포트를 연관짓고자 한다면 명시적으로 프로그램을 작성해야만 적확한 연결을 할 수 있다.

포트 선언

우리가 상수, 즉 포트를 선언하고자 할 때 다음과 같이 선언한다.

(port_direction) (data_type) (singed) ([port_size]) (port_name, port_name. ...);

- 포트의 방향(필수) : input, output, inout 3가지가 있다.

- data_type(선택적) : 실수형 불가, reg, wire, 등이 있음

- signed(선택적) : 부호있는 수를 나타냄

- port_size(선택적) : 포트의 크기 범위

- Port_name(필수) : 포트의 이름

ex) input a; //a라는 포트만 선언했음

ex) inout reg signed [3:0] a; // inout 레지스트리형 부호있는 4비트 a라는 포트 선언

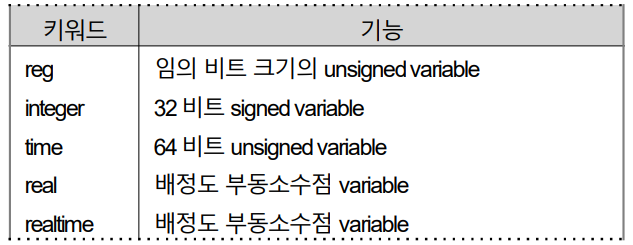

레지스터 형식의 변수

ex) reg signed [3:0] a[1:0]; // 부호있는 4비트 2개의 요소를 가지는 a배열 선언

NET 형식의 변수

ex) wire #(5,8,4) //small capacitance와 rise time, fall delay, decay를 가진 와이어

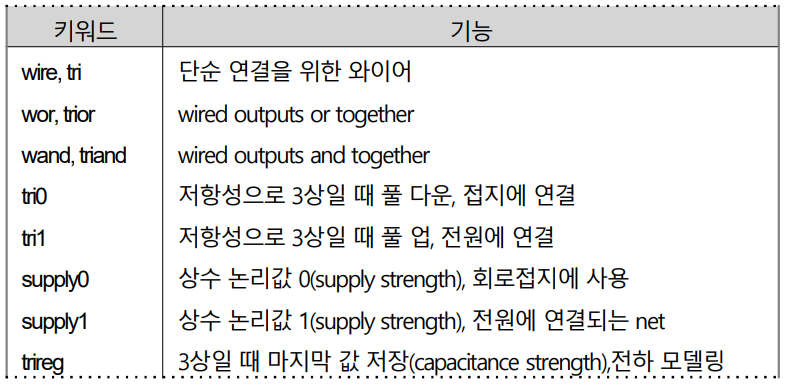

- 데이터 형 별 진리표

그 외의 데이터 형

벡터

date_type [MSB:LSB] name

ex)

배열

date_type name[size]

ex)

연산자

| 연산자의 종류 | 예시 | 기능 |

|---|---|---|

| 산술 연산자 | +, -, *, / | 사칙연산 |

| 이동 연산자 | <<, >> | 비트를 이동하여 연산 |

| 관계 연산자 | =<, => | 양 항을 비교하여 0, 1도출 |

| 등가 연산자 | ==, !== | 논리값을 비교함 |

| 비트단위 연산자 | ~, &, ^, ~^ | 논리 연산을 비트단위로 수행함 |

| 축소 연산자 | &, ~&, ^ | 단일 오퍼랜드에 1비트의 논리연산 수행 |

| 논리 연산자 | !, &&, | 논리 연산자 |

| 결합 연산자 | {},{{}} | 스칼라 또는 벡터의 구성요소를 결합하여 벡터 생성 |

| 조건 연산자 | K?n:m | K가 참이면 n, 거짓이면 m |

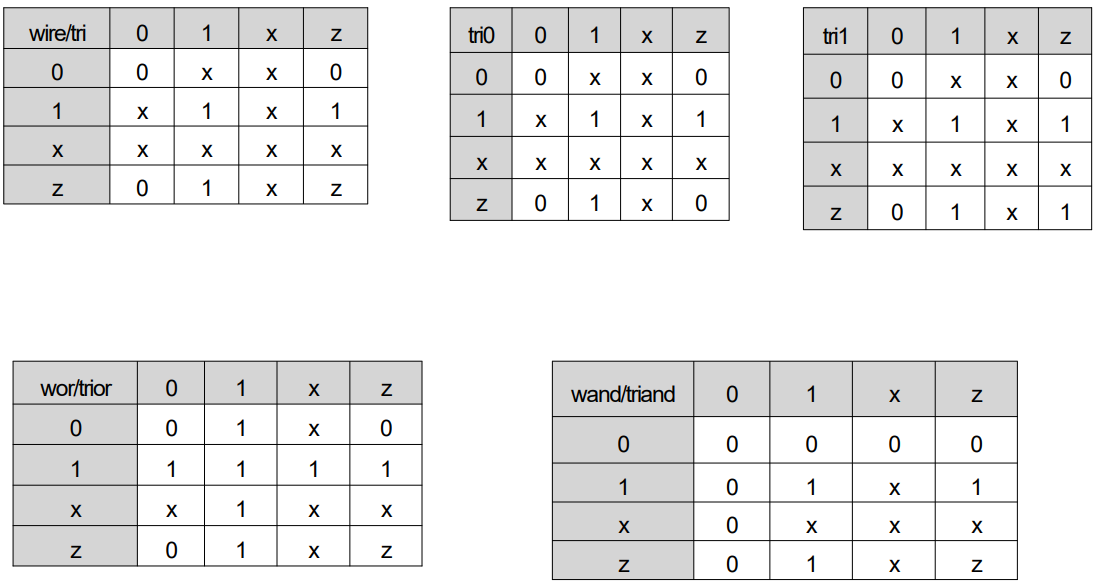

모듈 인스턴스

모듈 인스턴스란 구조적으로 모델링을 하는 과정이다. 모델에 하위 모듈이나 기업에서 제공하는 프리미티브 게이트를 포함하는 과정을 의미한다.

모듈의 포트 이름을 나열하는 곳에는 반드시 사용되는 포트의 이름의 순서를 잘 지켜야만 한다.

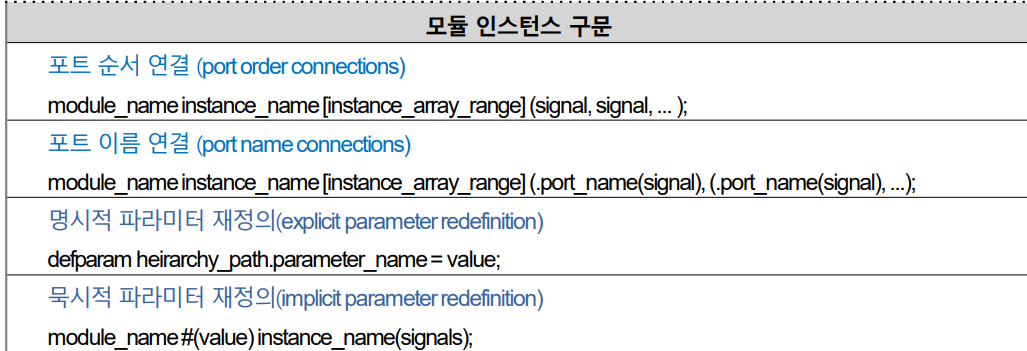

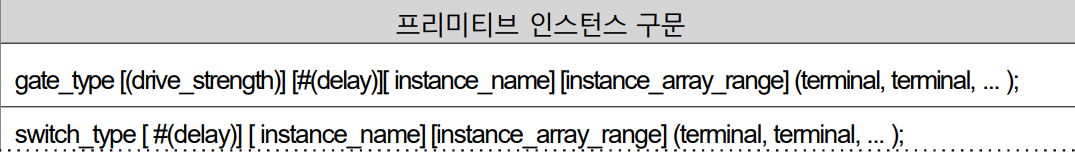

프리미티브 인스턴스

언급했었듯이 프리미티브 게이트, 인스턴스는 기업에서 제공하지만 verilog에서 자체적으로 지원하는 프리미티브 게이트들도 존재한다.

-

verilog의 프리미티브 게이트

-

프리미티브 게이트 사용하기

and, or, xor, buf는 input, output의 개수제한이 따로 없다. 그러나 bufif1, bufif0는 반드시 input, output이 1개씩, 컨트롤러가 1개이여야만 한다. 또한, 프리미티브 게이트는 반드시 사용에 연결 순서를 지켜야만 한다는 점도 주의점으로 꼽을 수 있다.

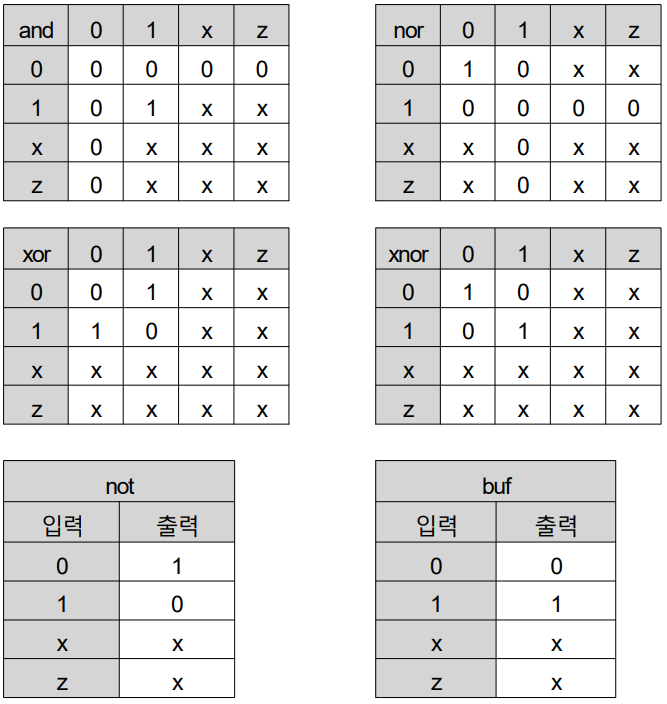

- verilog에서 지원하는 프리미티브 게이트들의 진리표

프리미티브 인스턴스의 지연시간 표현

신호의 전달 속도는 매질의 유전율의 루트에 반비례하므로, IC 내부의 소자들과 전선들의 재질이 모두 다르기 때문에 지연시간을 표기해 주어야만 한다.

ex) wire #(delay1, delay2, delay3) (out1, in1, in2)

system task와 함수

verilog에서 시뮬레이션을 사람이 구현하여 모니터에 띄우는 등의 프로그램 조작을 실행할 때 필요한 함수이다. 하위 모듈에 작성하고 기능하며, 모듈 끝단에서 모든 연산이 종료된 후 그 결과를 보이거나, 모듈 중단에서 랜덤 난수를 생성, 또는 시뮬레이션의 조작 등을 하기 위해 삽입된다.

ex) $time //현재 시뮬레이션 시간

ex) $random(seed) // 임의의 난수 생성