Review

- IF (Instruction fetch)

- ID (Instruction decode / register file read)

- EX (Execute / address calculation)

- MEM ( Memory access)

- WB (Write back)

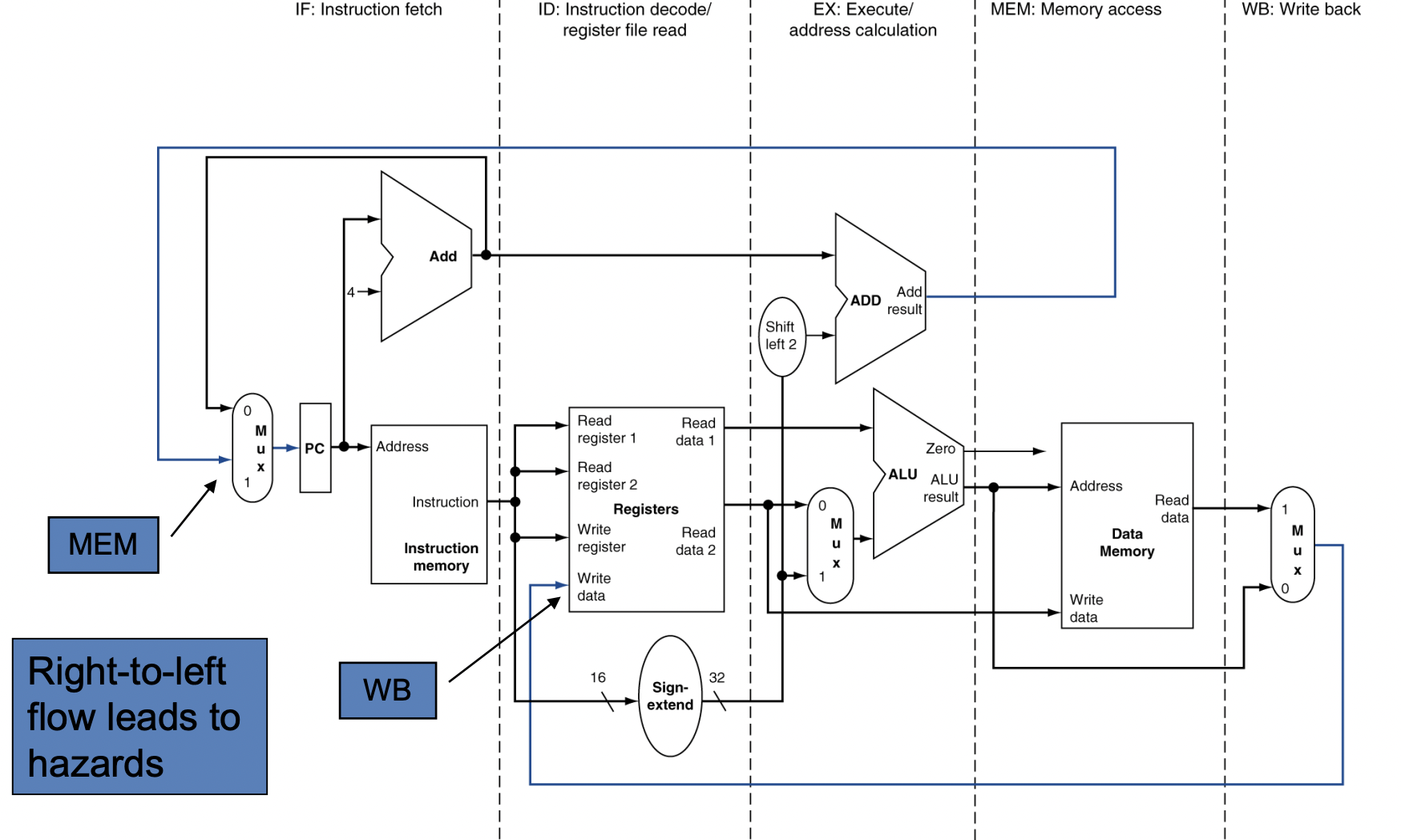

- 예외

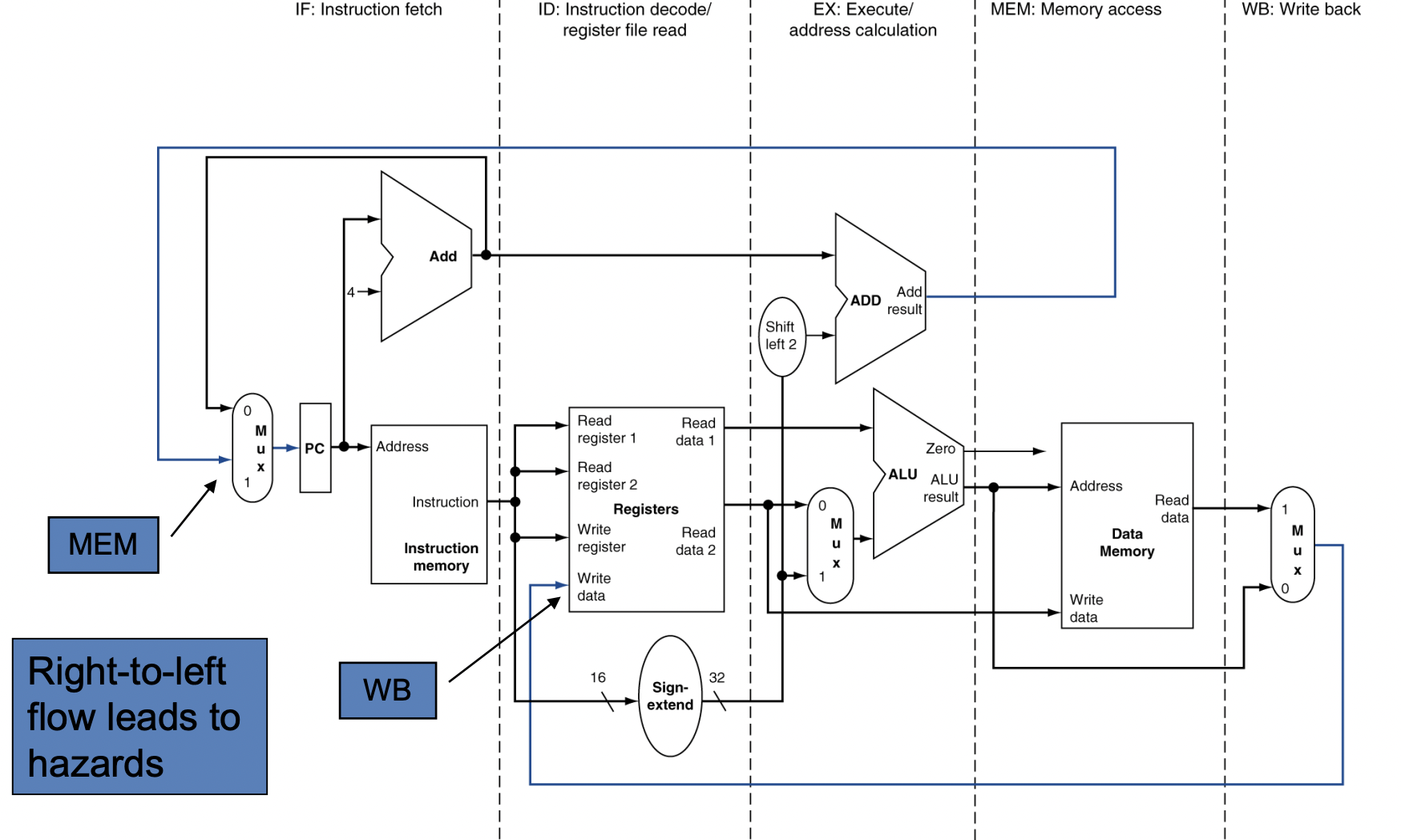

- WB (쓰기 단계)

: 결과를 datapath의 중앙에 있는 register file에 쓴다

-> Data Hazard로 이어질 수 있다

- MEM (PC의 다음 값 선정)

: 증가된 PC값과 MEM 단계의 branch 주소 중에서 고른다

-> Control Hazard로 이어질 수 있다

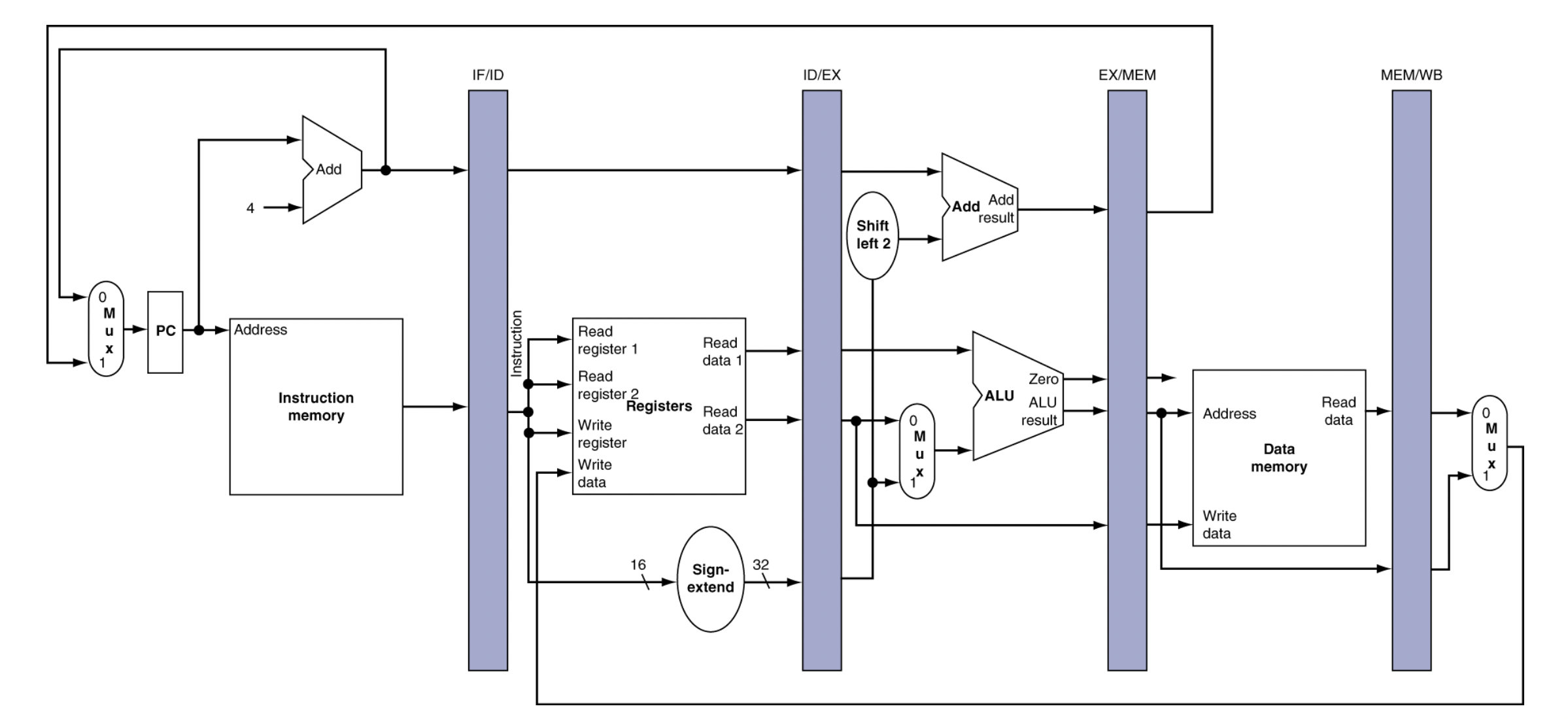

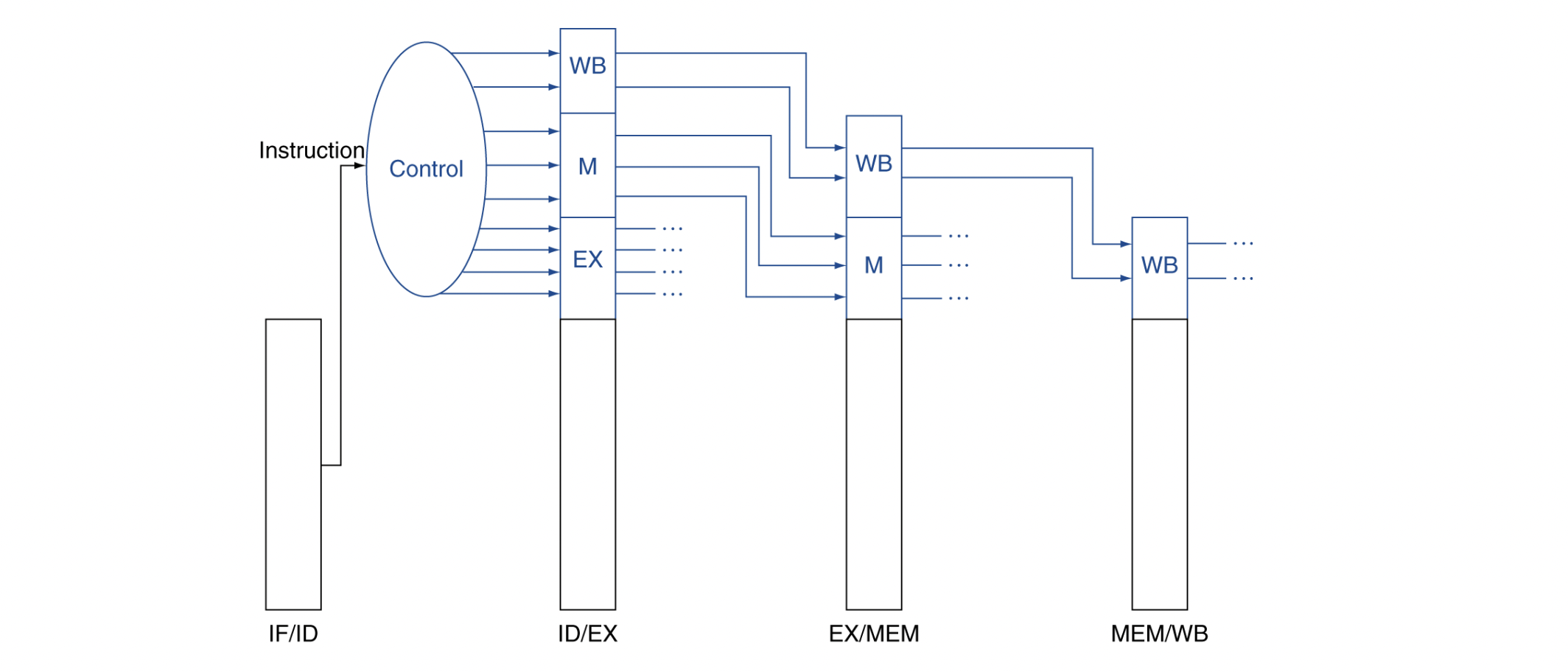

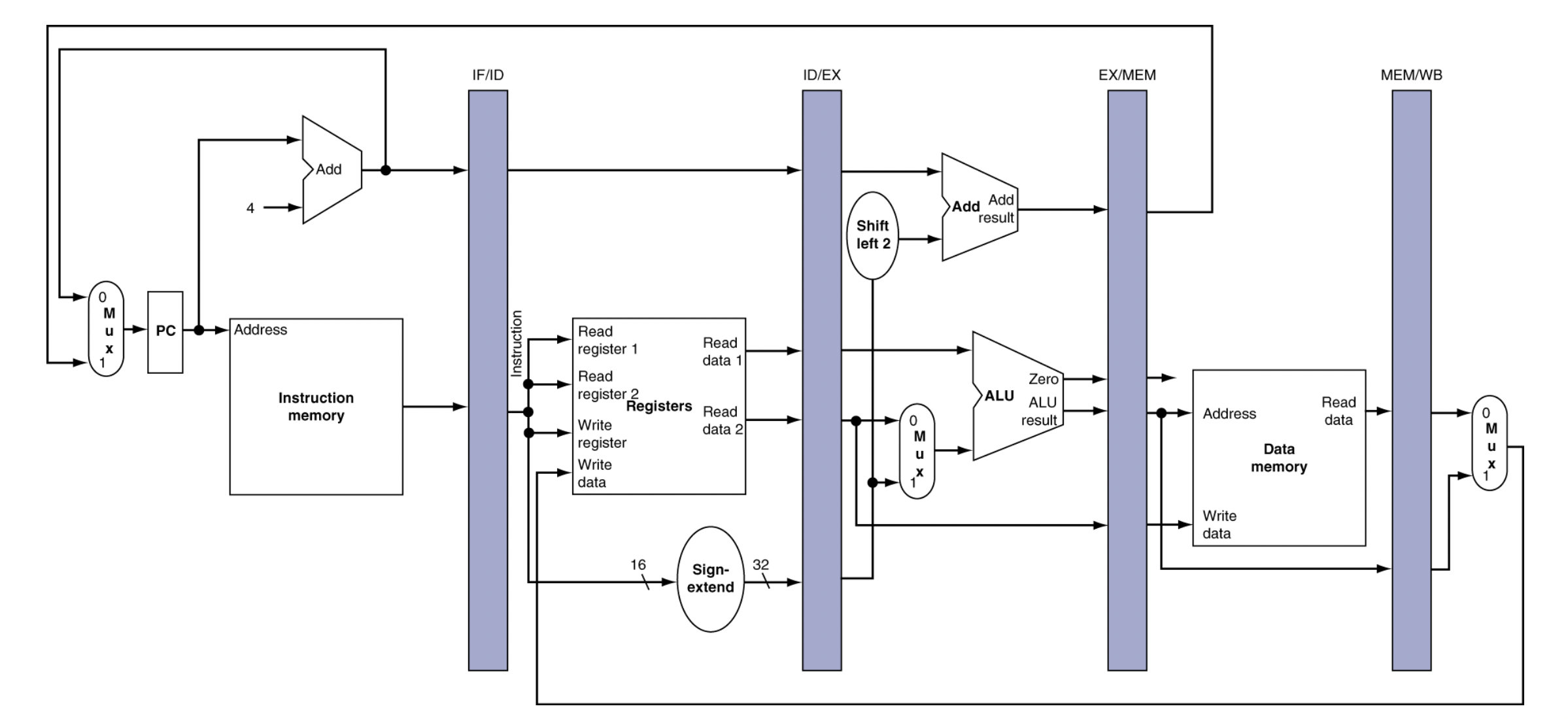

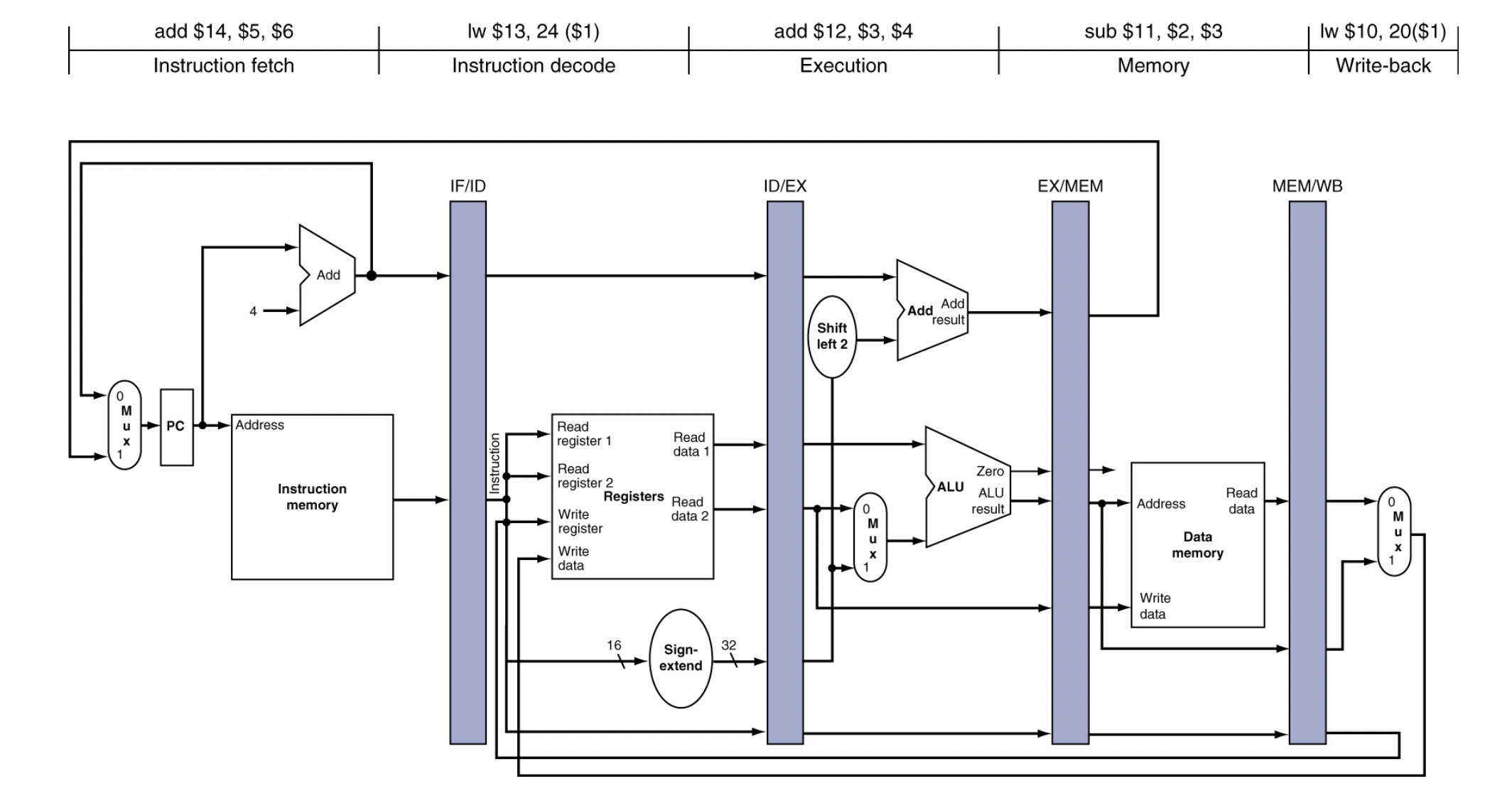

Pipeline register

- stage 사이에 register가 필요하다

- 이전 cycle에서 생산된 정보를 hold한다

Pipeline Operation

- Pipeline datapath를 통해 instruction의 cycle-by-cycle flow

- load와 store의 "single-clock-cycle" diagram을 보자

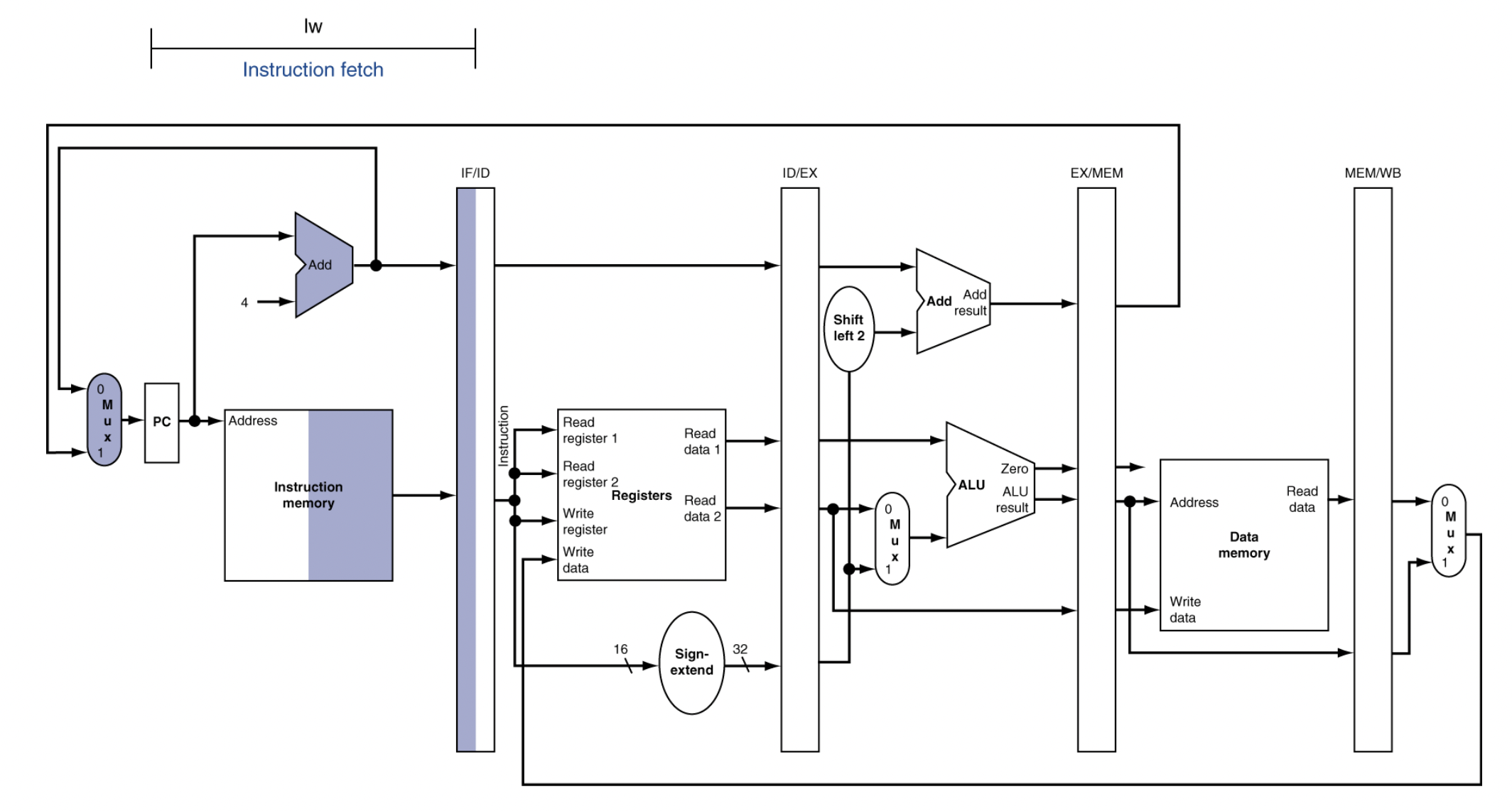

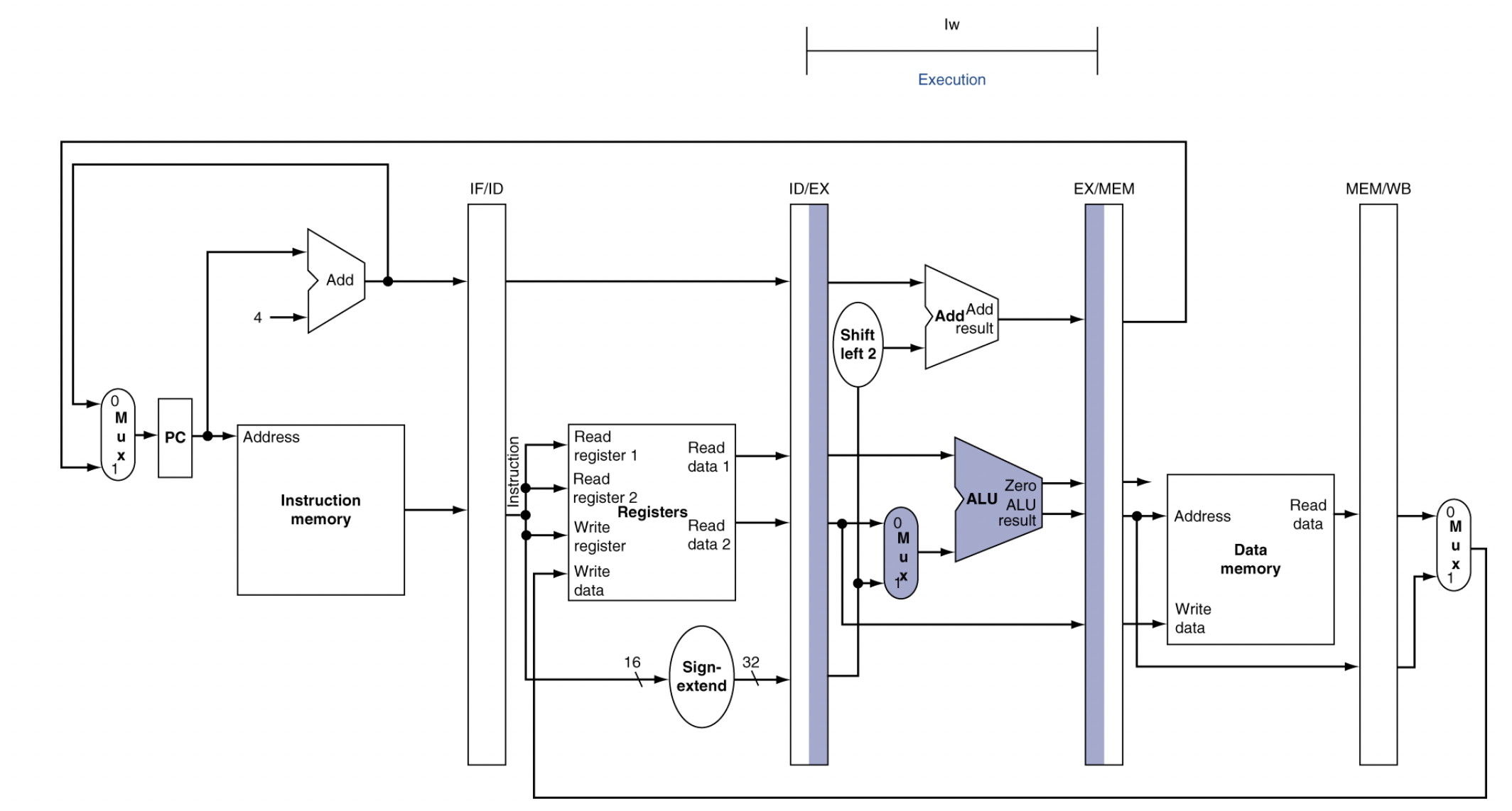

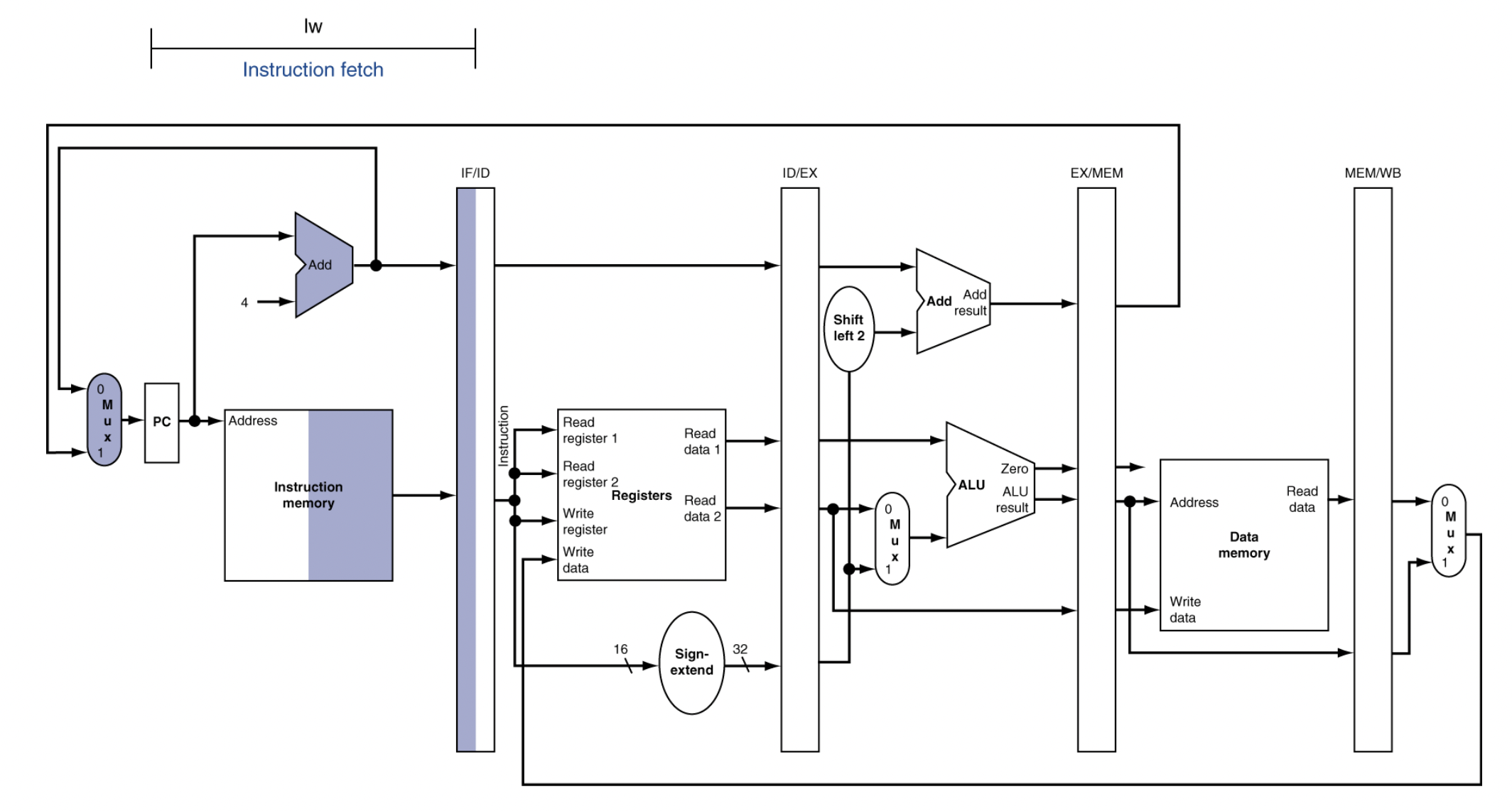

LOAD

IF

- instruction memory에서 읽어서 pipeline register에 저장한다

- (교재)

- PC에 있는 주소를 사용하여 메모리에서 명령어를 읽어오고 p-register에 저장한다

- PC 주소는 4만큼 증가되어 다시 PC에 저장된다 -> 다음 cycle에 이용 가능하다

- 이 증가한 주소는 후에 beq처럼 뒤에 필요한 경우를 위해 p-register에 저장된다

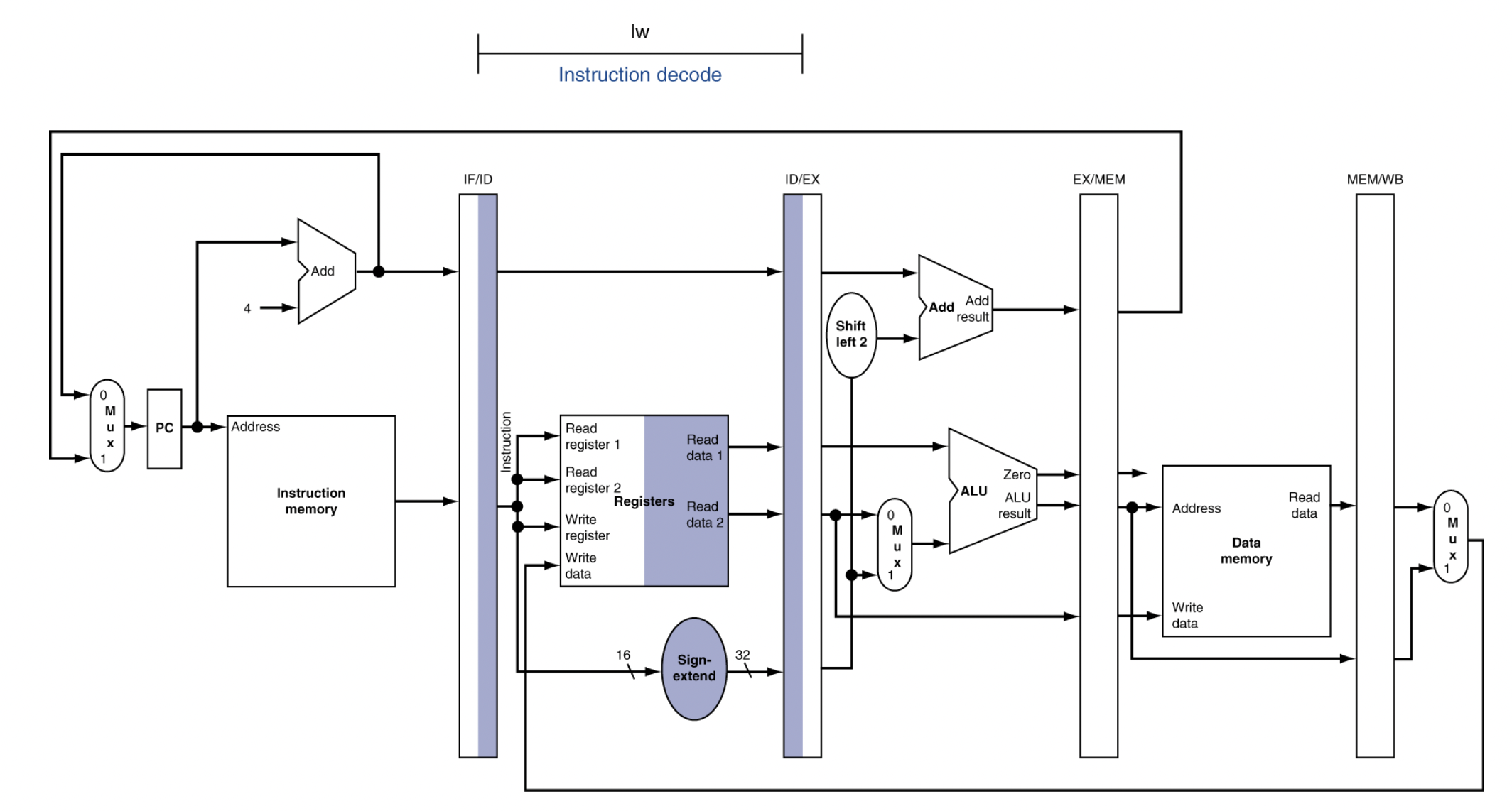

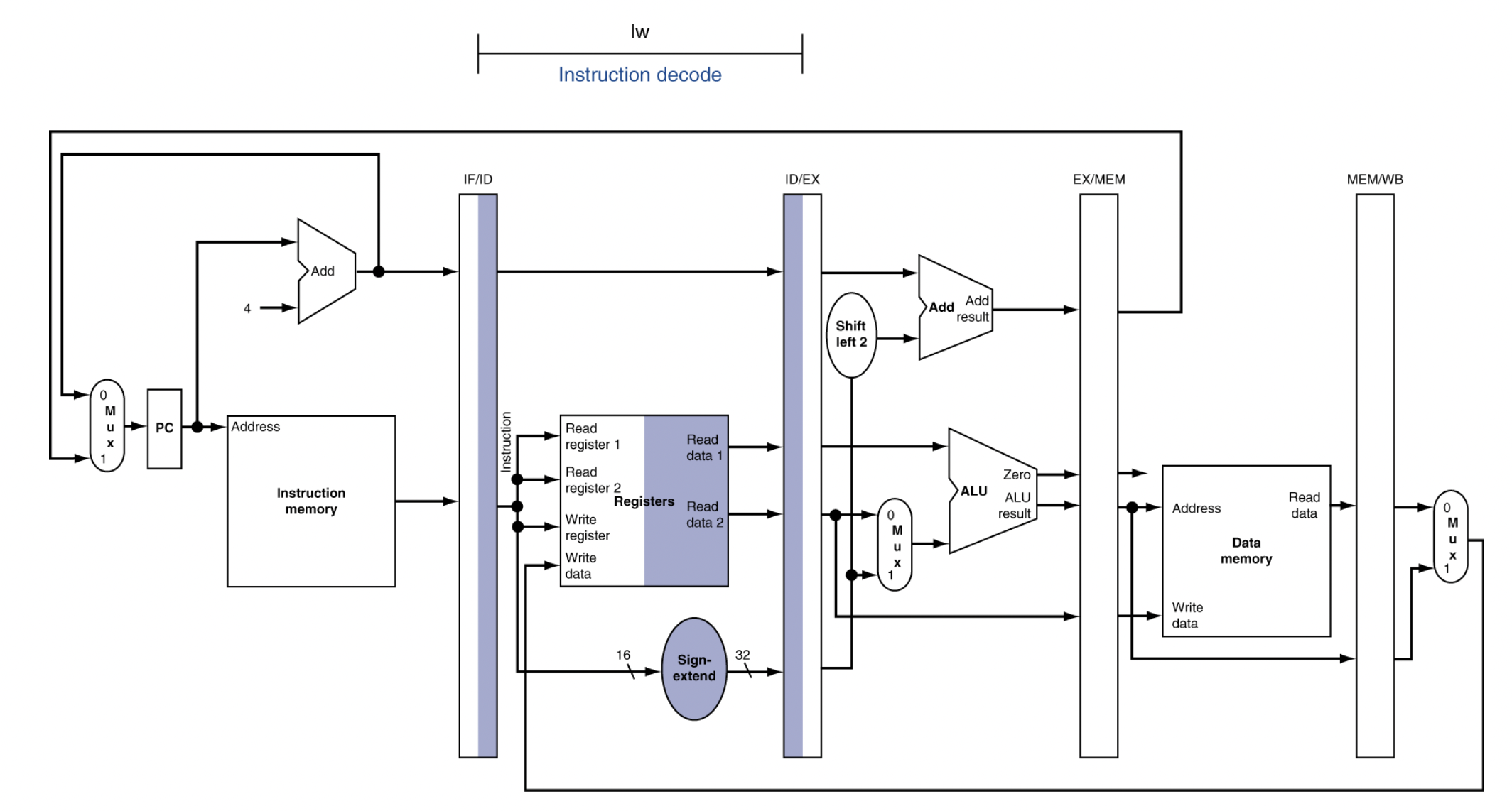

ID

- 이전 pipeline register가 input 역할을 한다

- 주의 : pipeline register is NOT 32-bit register

- register number, offset 등 다음 cycle에서 실행하기 위해 필요한 추가적인 정보들을 가지고 있다

- (교재)

- register 번호 두개와, 16-bit immediate field를 전달한다.

- 세 값 모두 증가한 PC값과 함께 p-register에 저장된다.

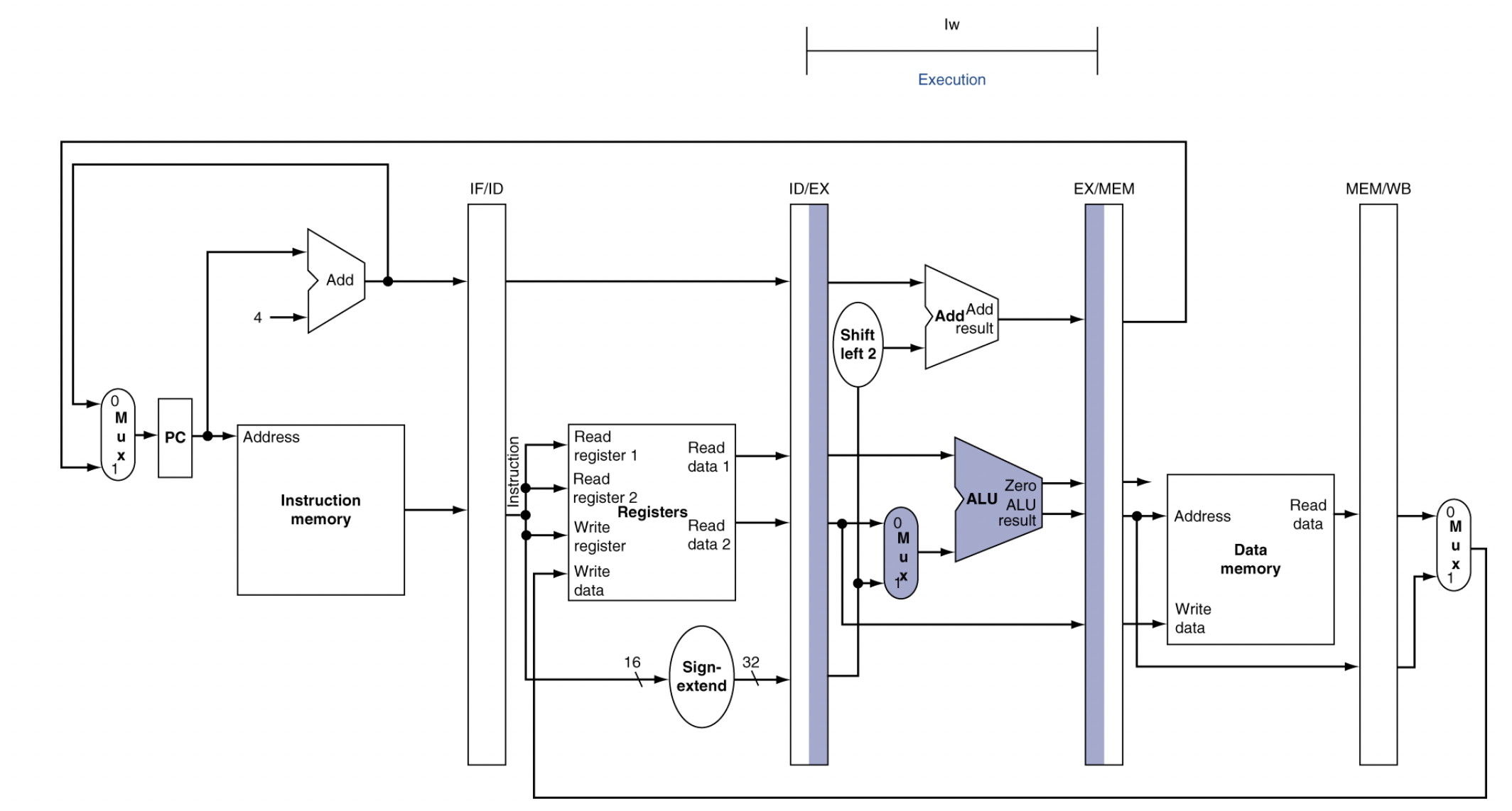

EX

- offset + base register address를 통해 메모리 주소를 계산하고 이를 pipeline register에 저장한다

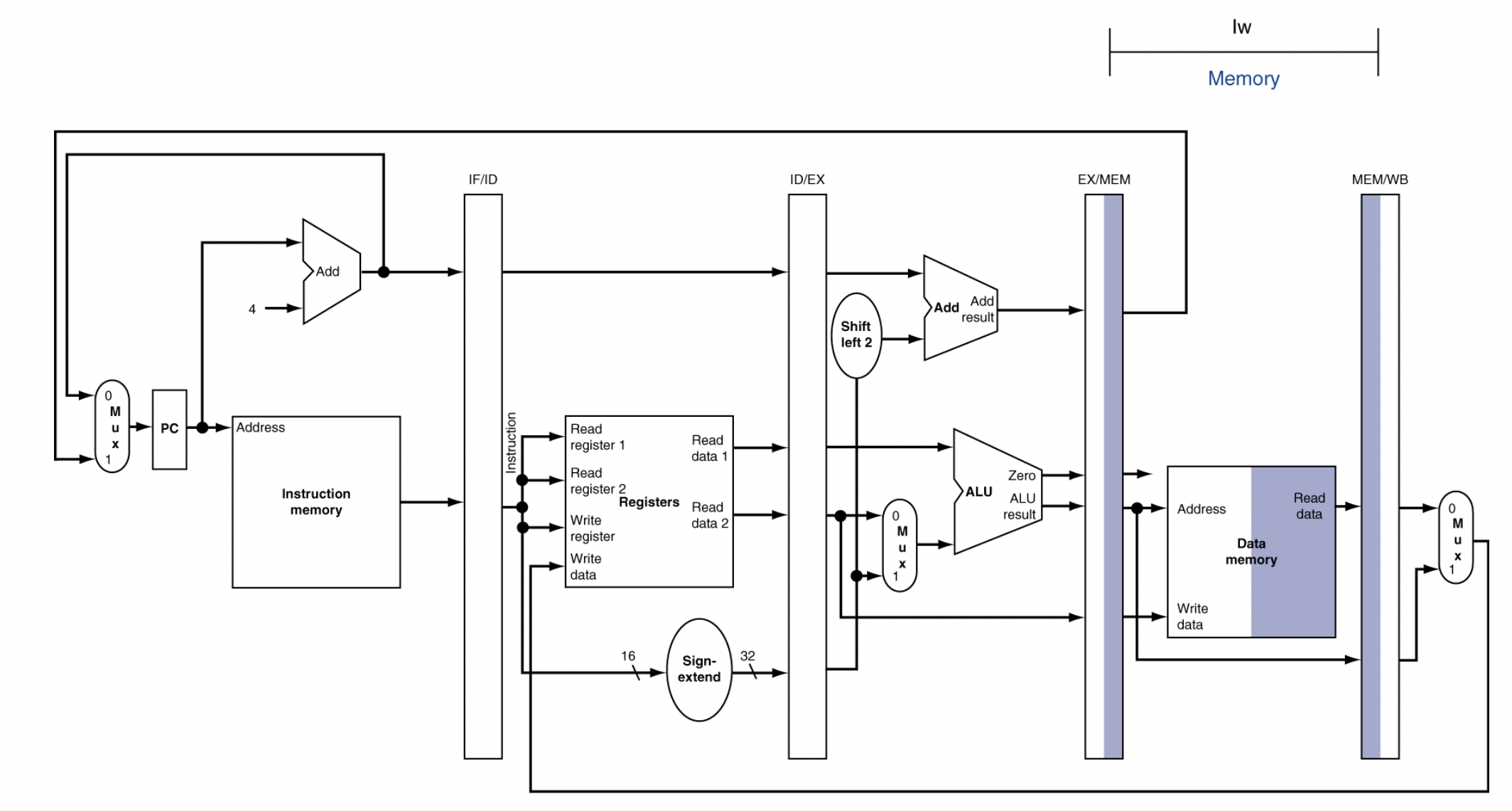

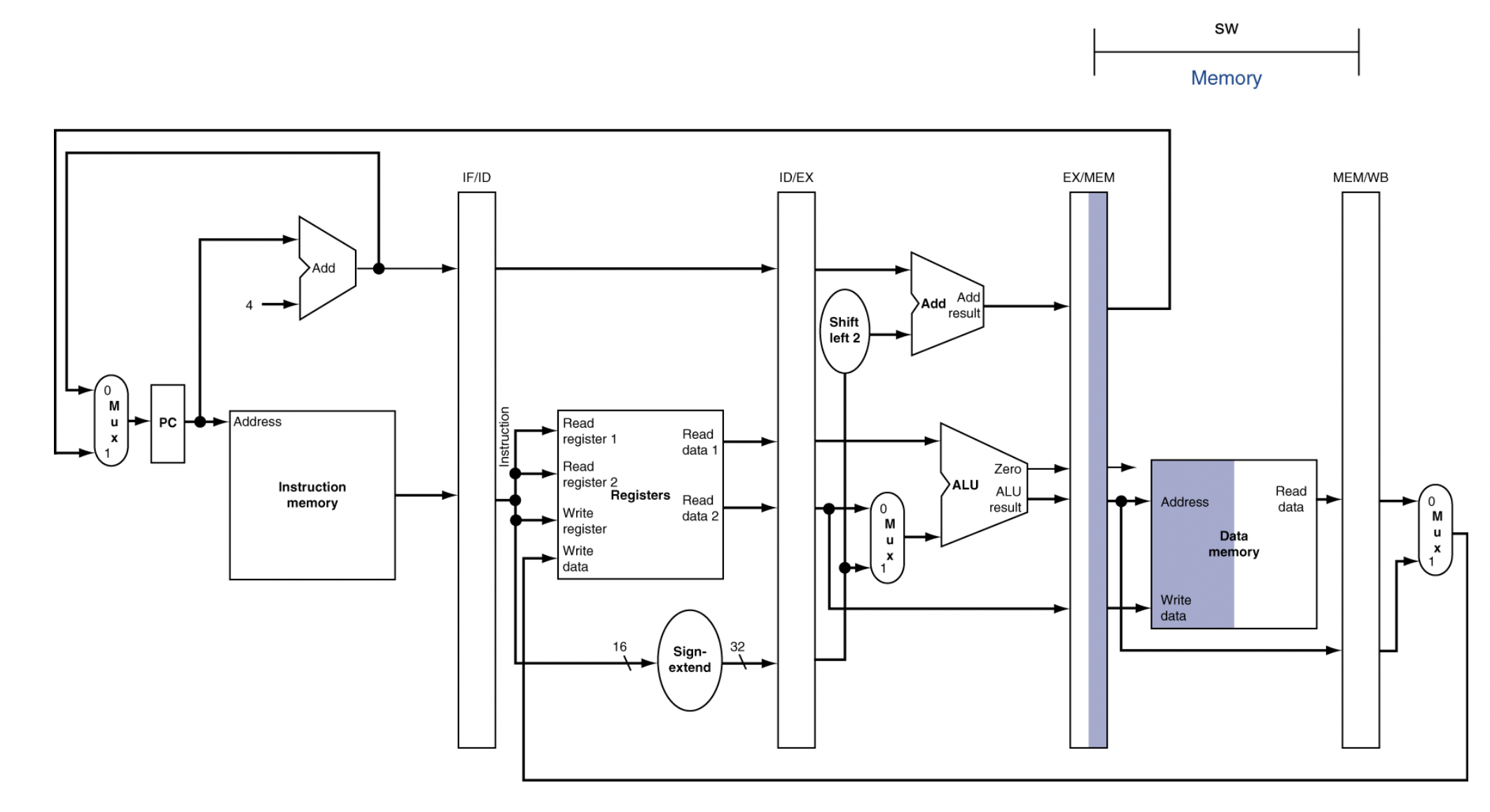

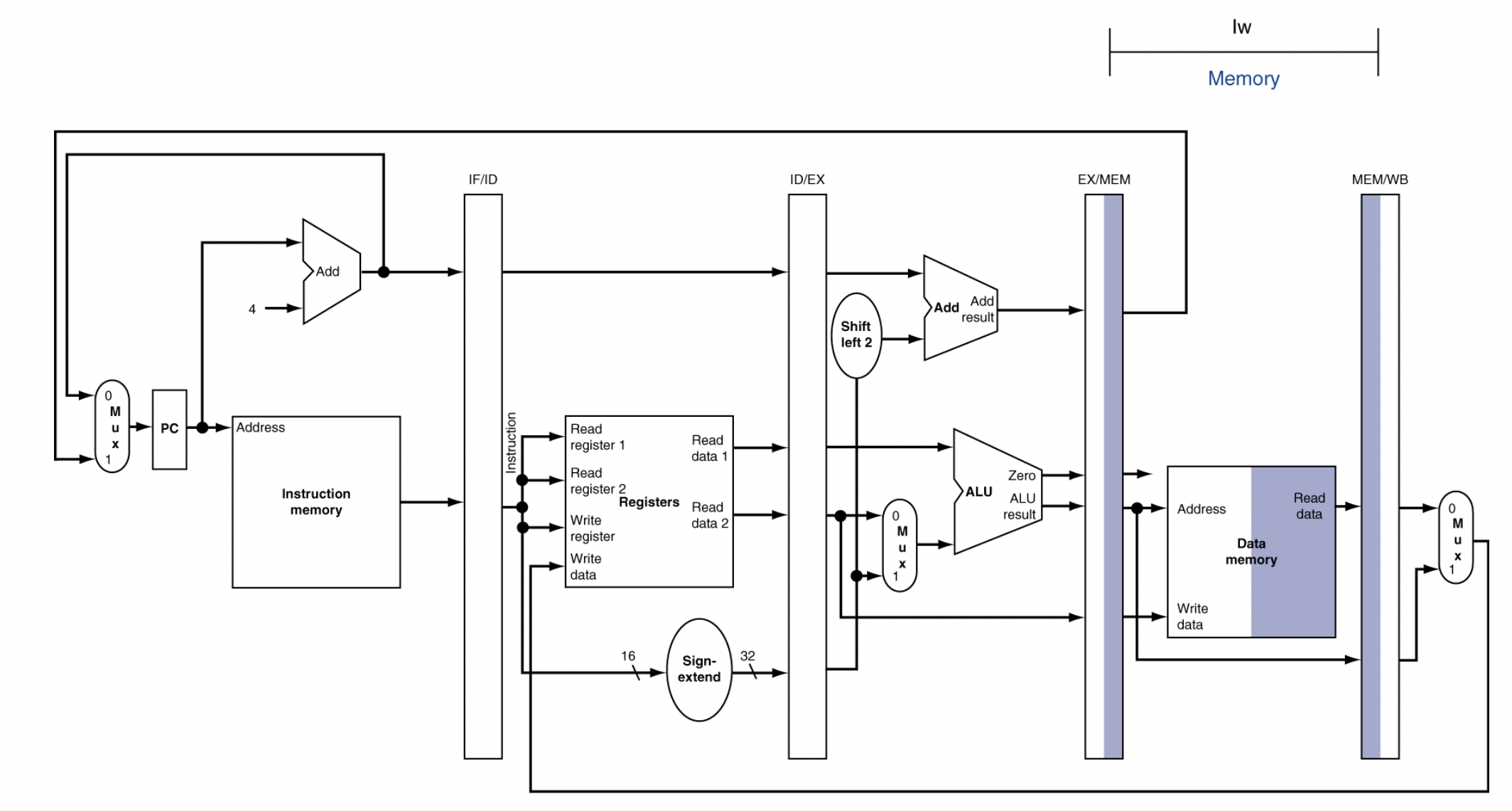

MEM

- (교재)

- 주소를 받아서 데이터 메모리를 읽고, 이 데이터를 p-registerdp wjwkdgksek

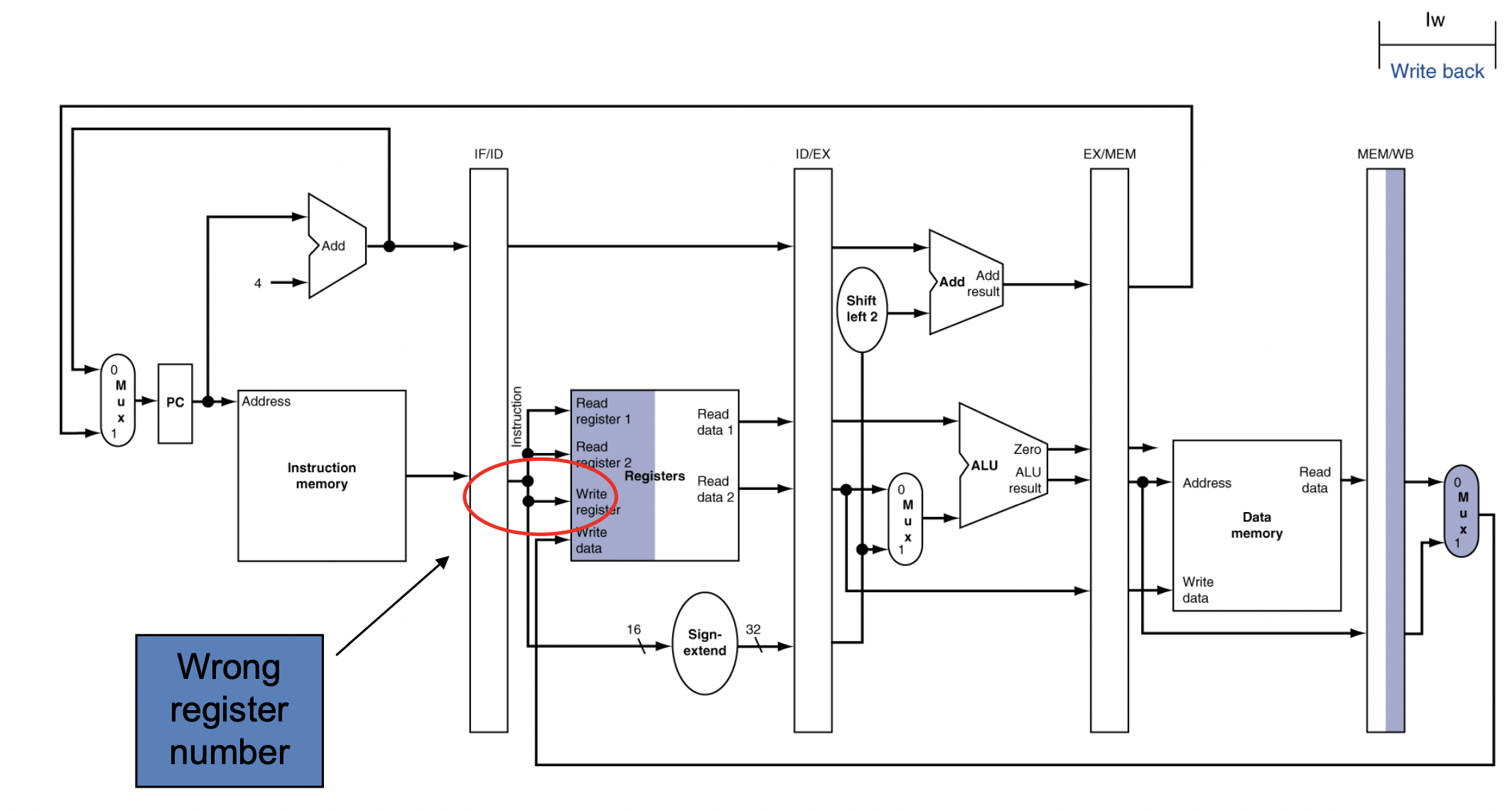

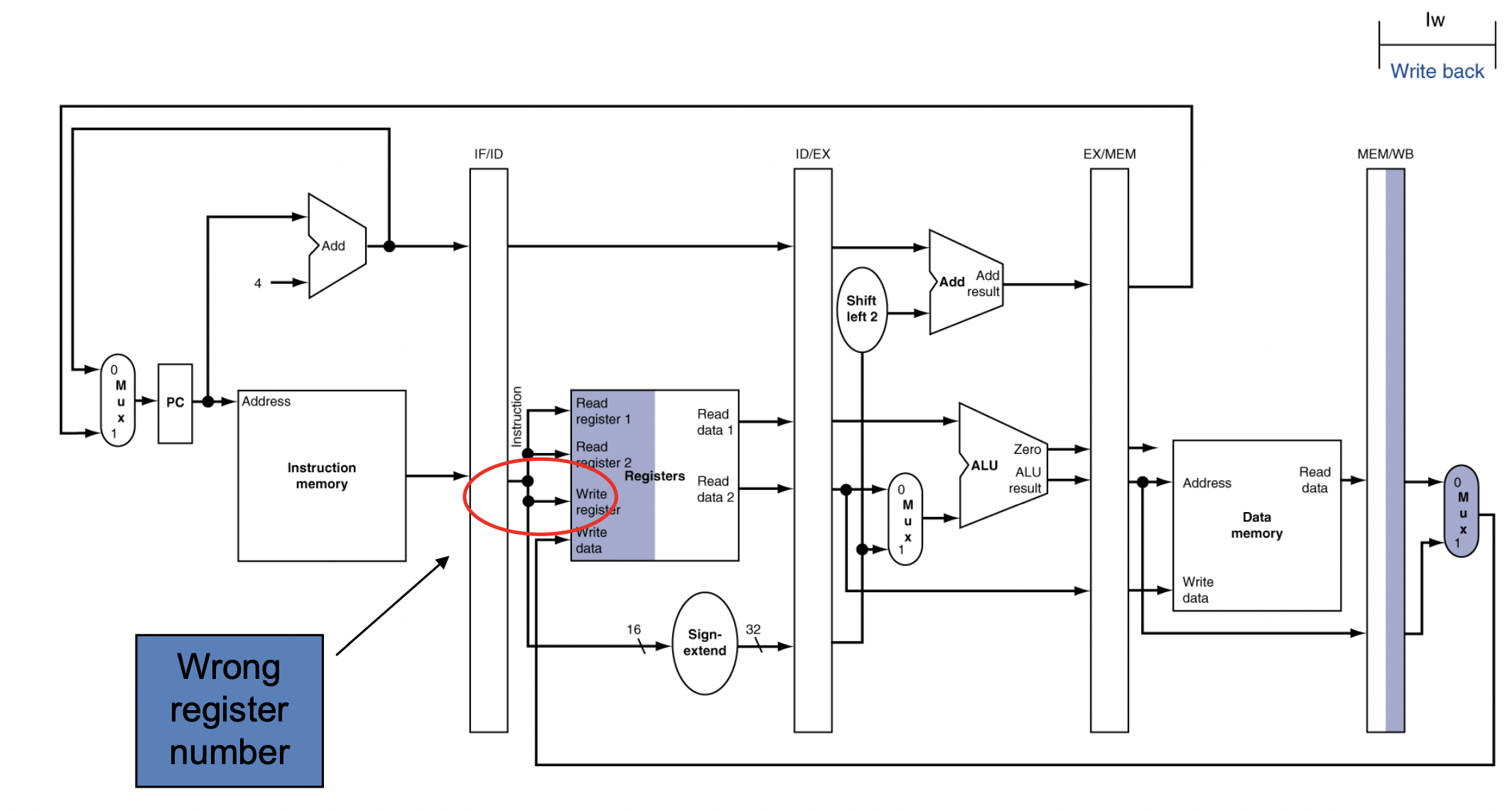

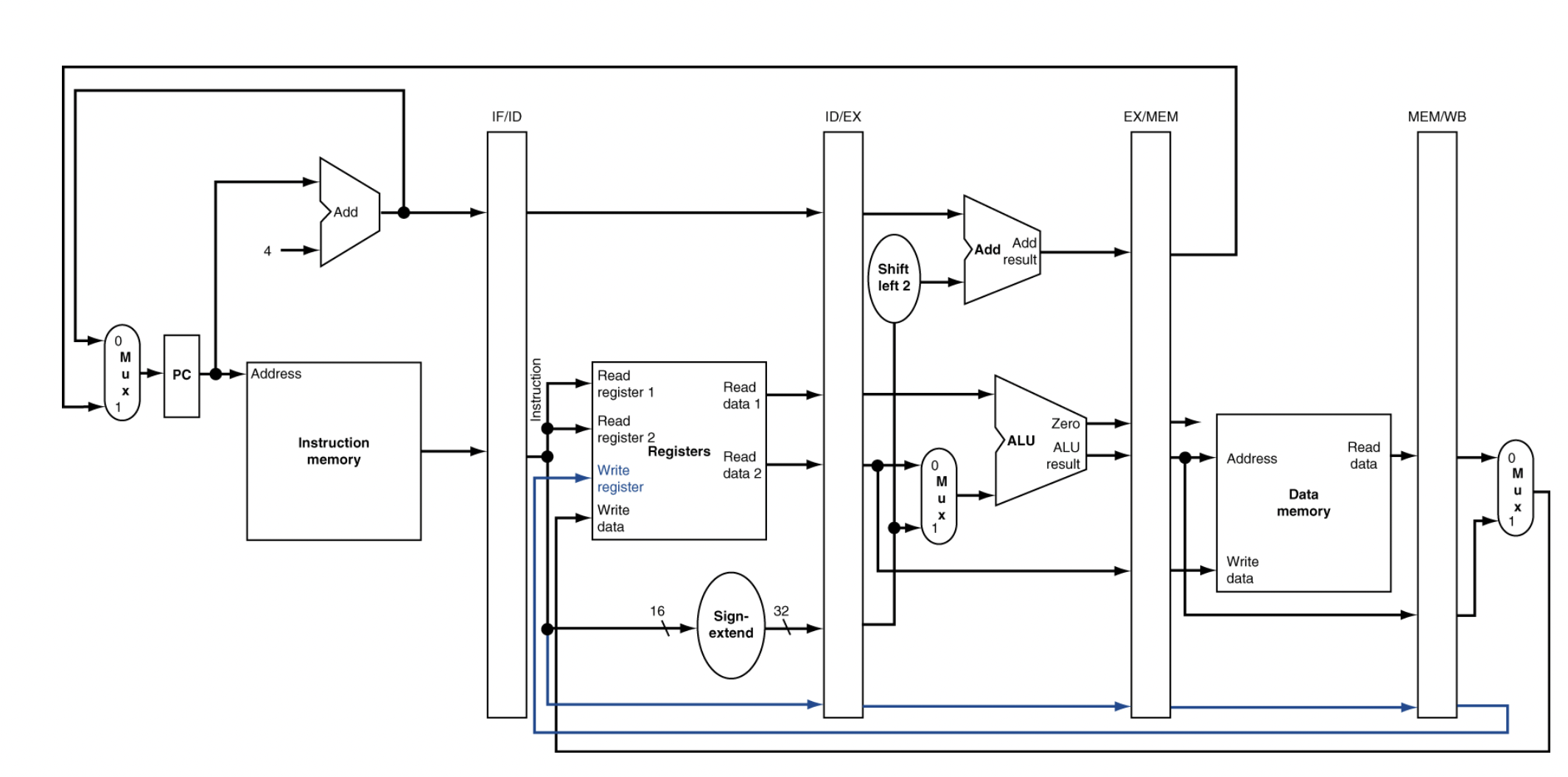

WB

- data를 register file에 쓴다

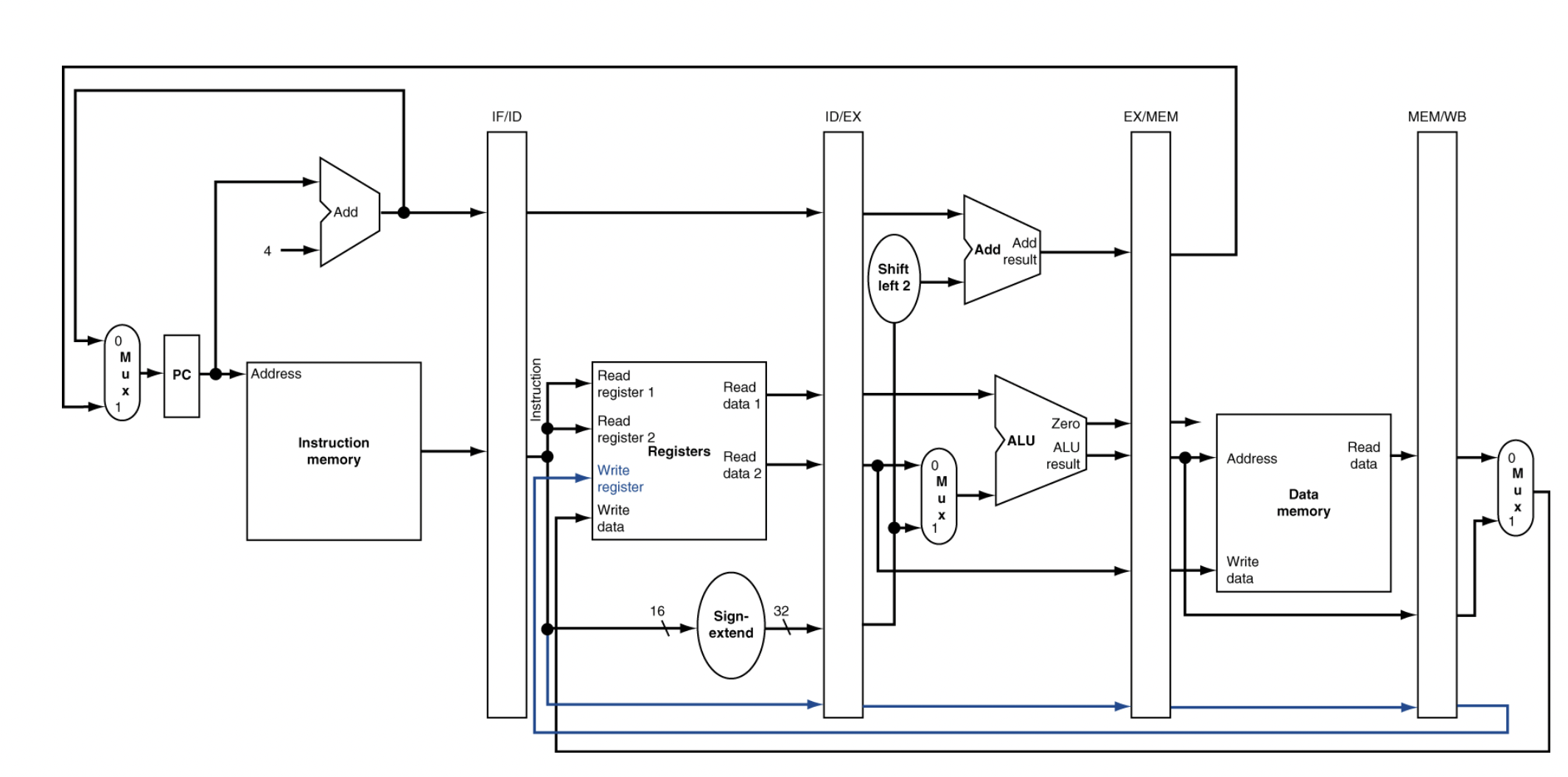

- We need Data and Register Number

- register number는 ID에서부터 pipeline을 통해 계속 가져와야 한다

Corrected Datapath for Load

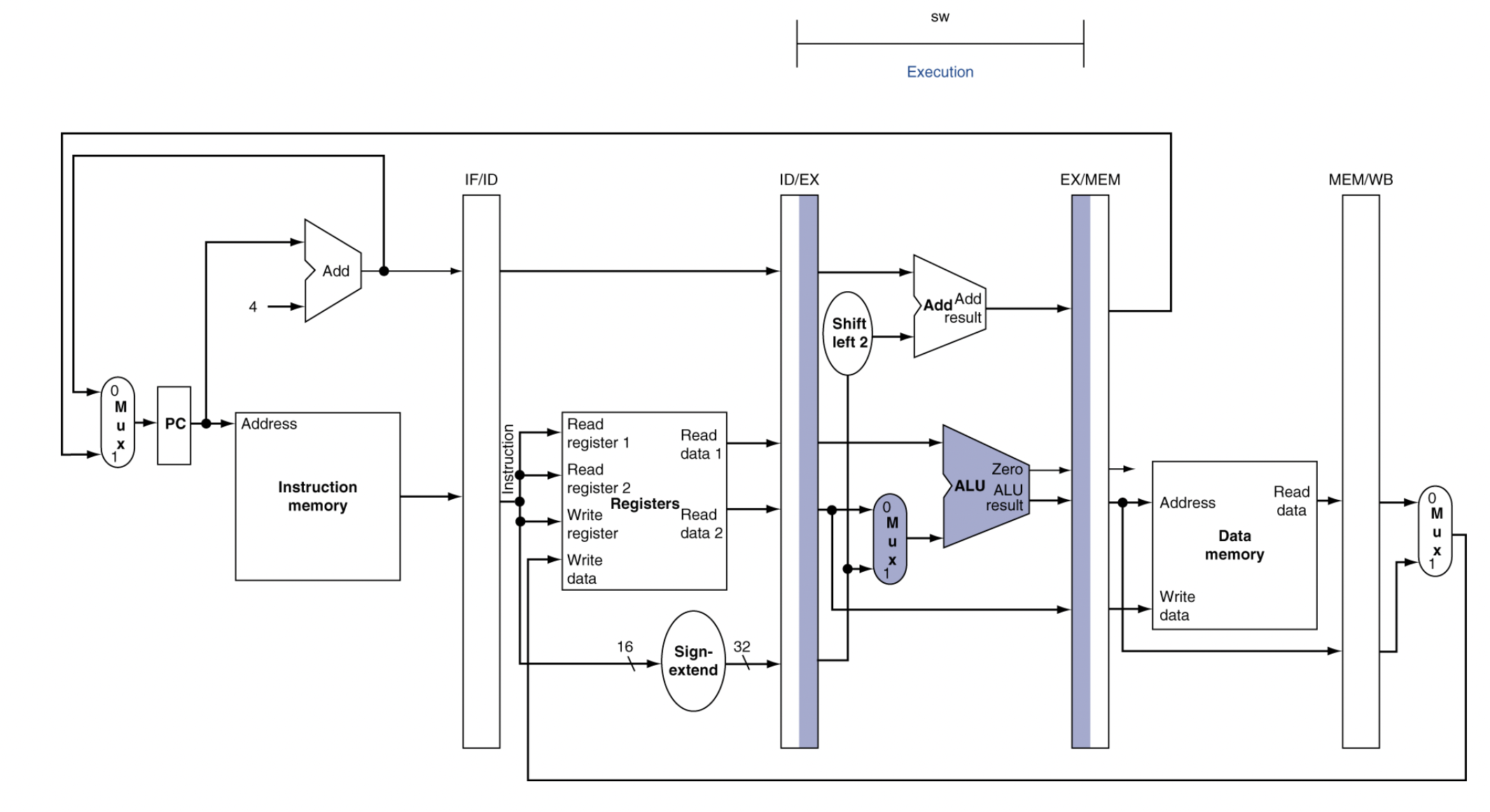

STORE

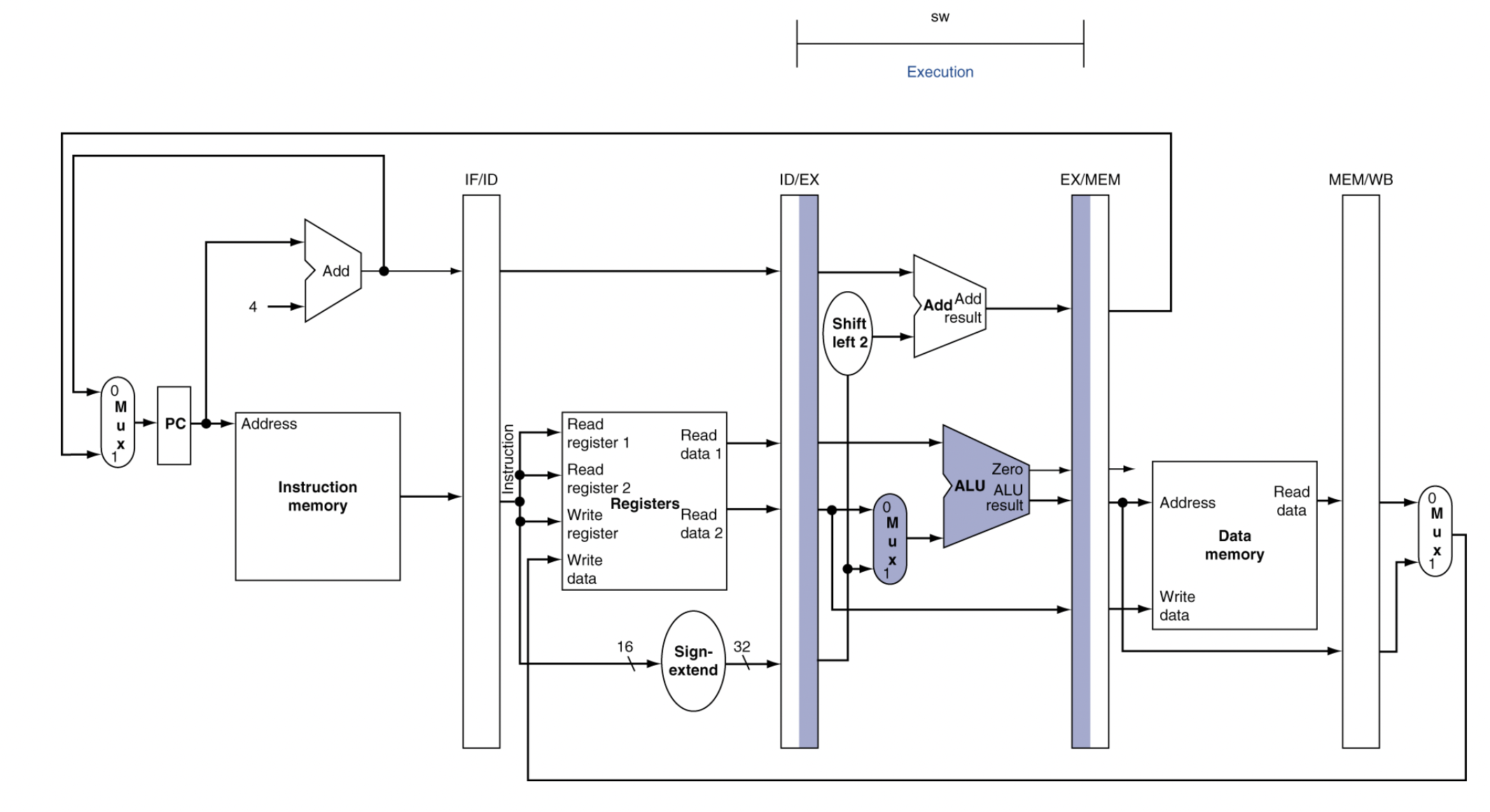

IF, ID, EX는 LOAD와 동일

EX

- (교재)

- Load에서와 다르게 두 번째 register값이 다음 p-register에 저장된다.

-> 다음 단계에서 사용된다

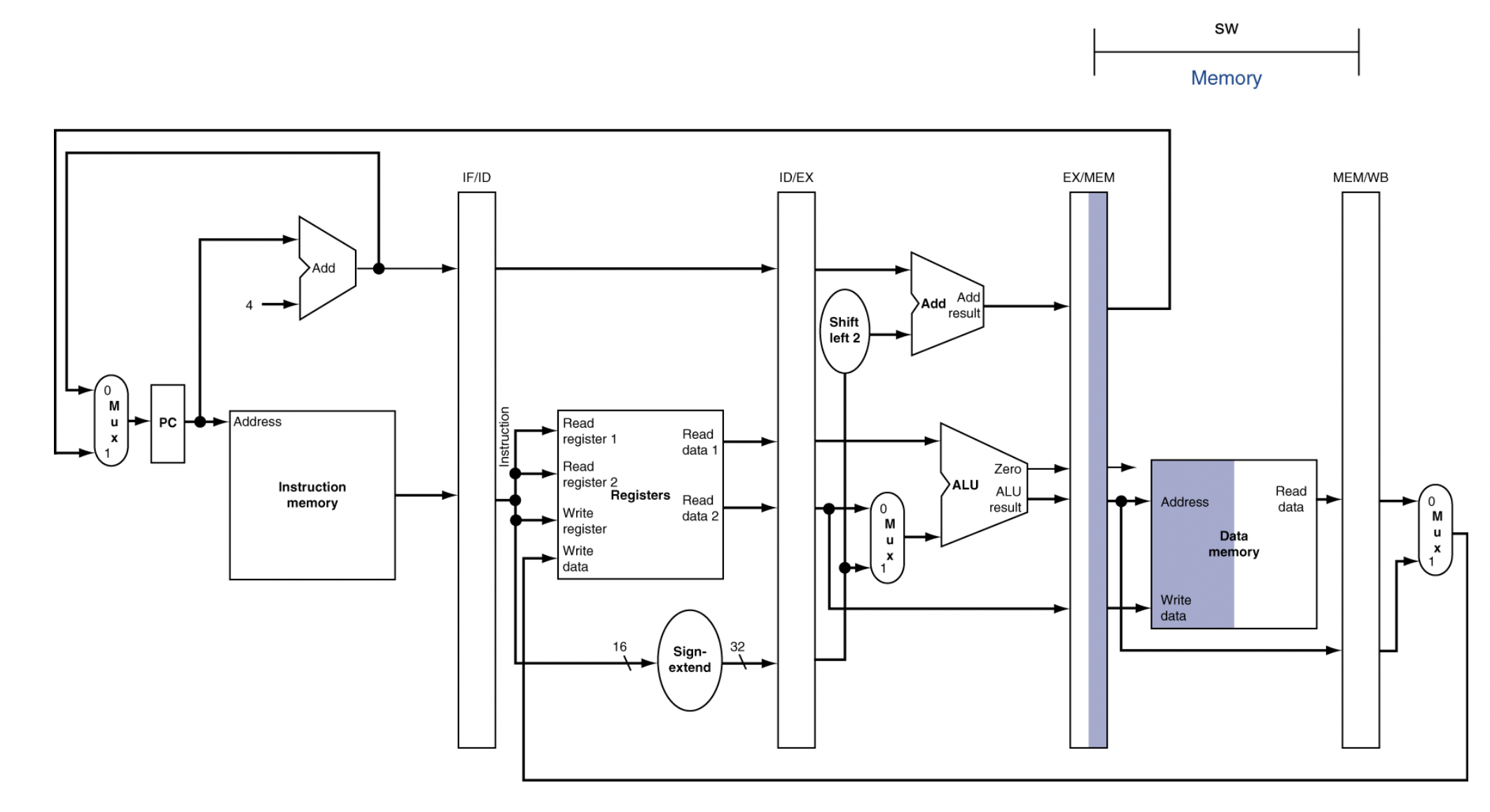

MEM

WB

- store에서는 데이터를 메모리에 쓰고 난 후 할 게 없기 때문에

아무 일도 일어나지 않는다

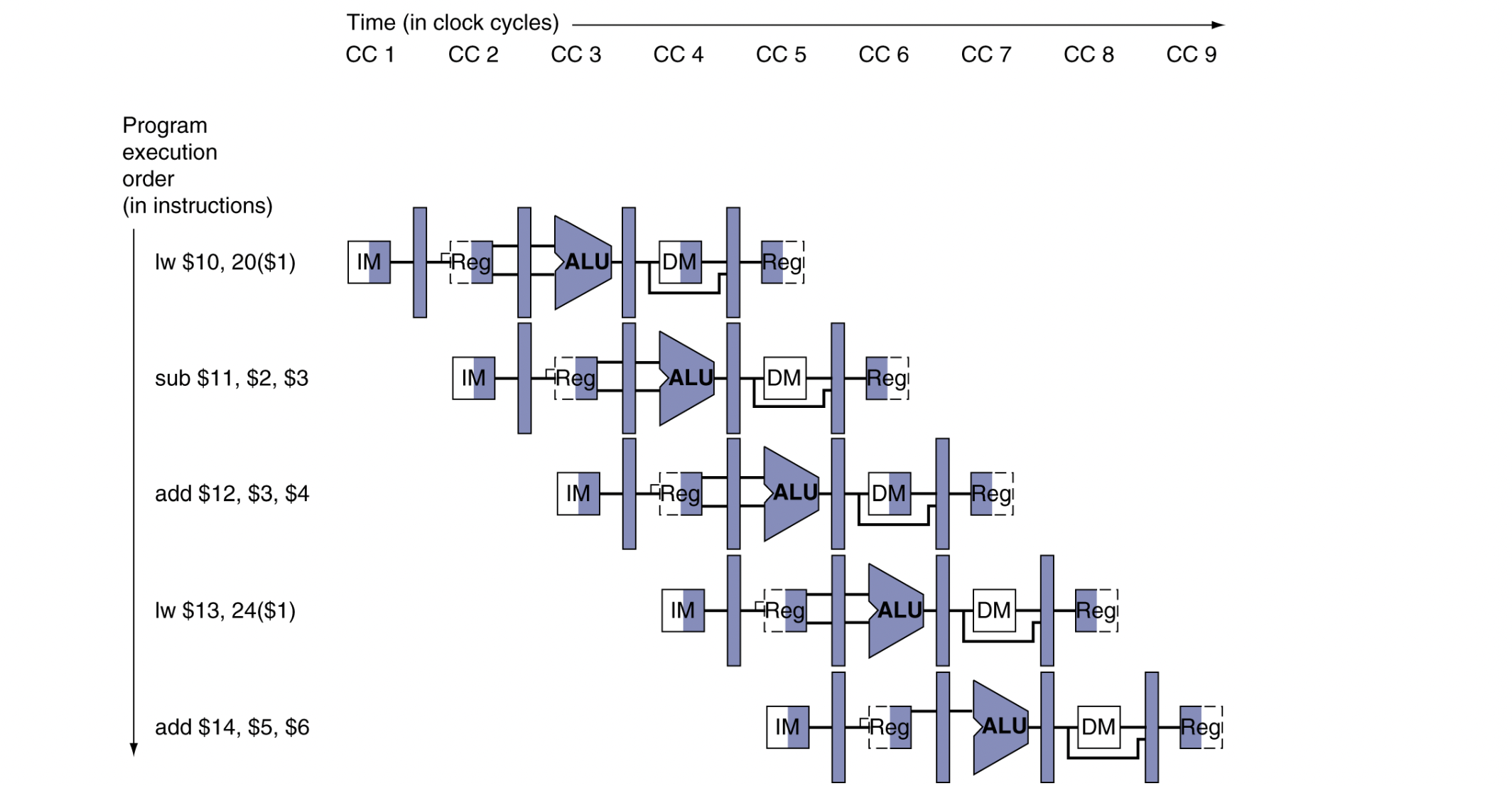

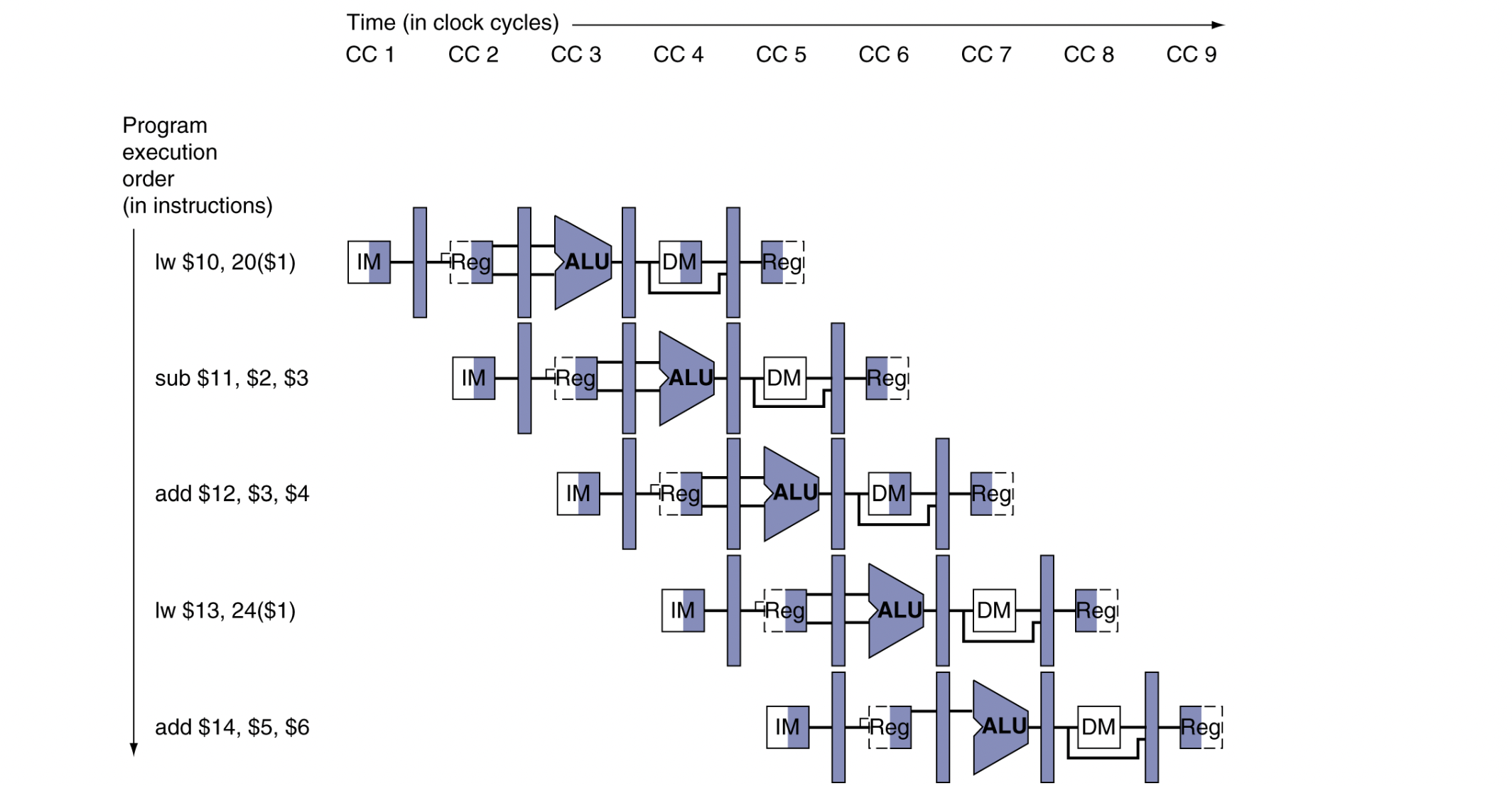

Multi Cycle Pipeline Diagram

Single Cycle Pipeline Diagram

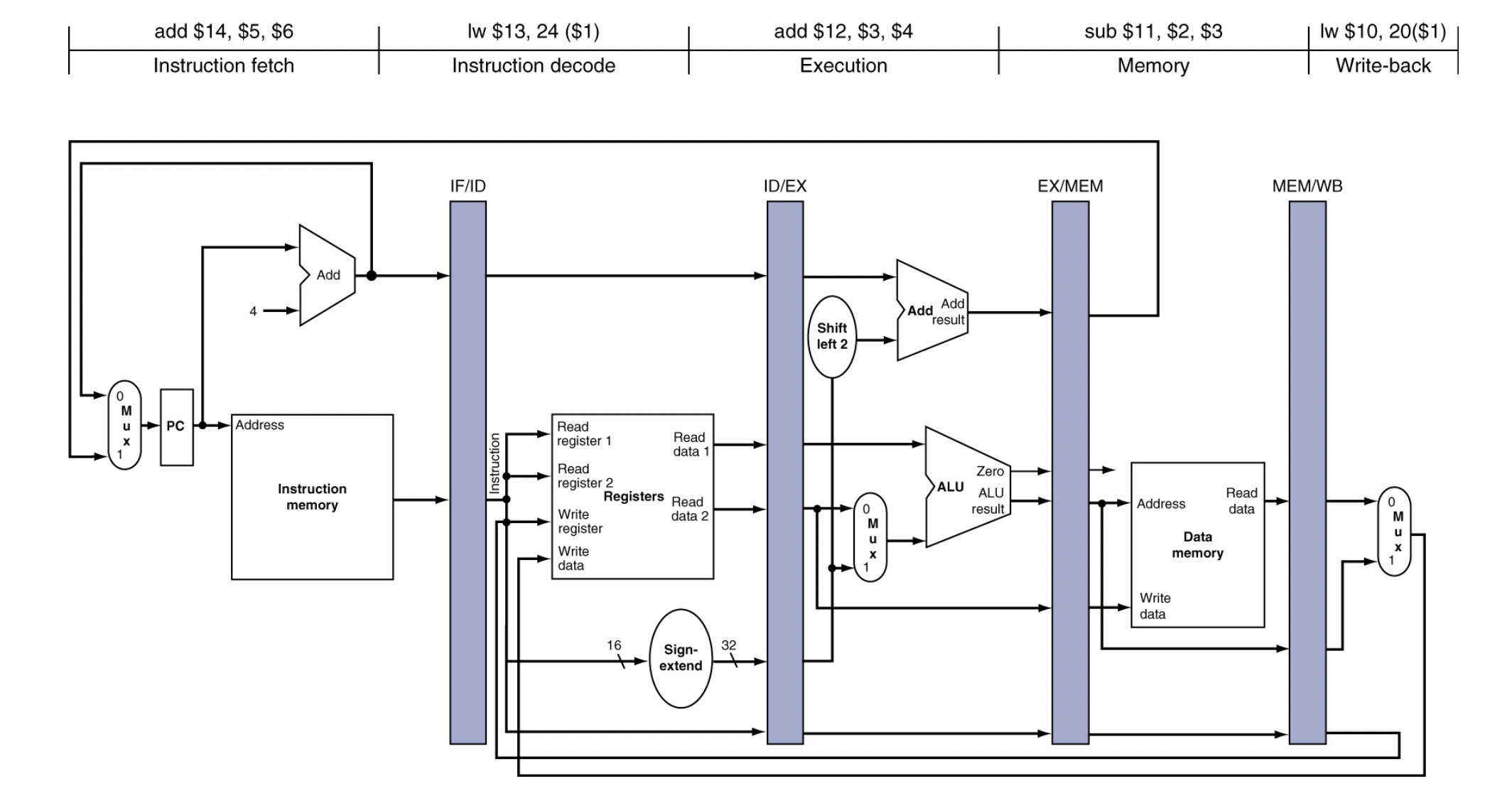

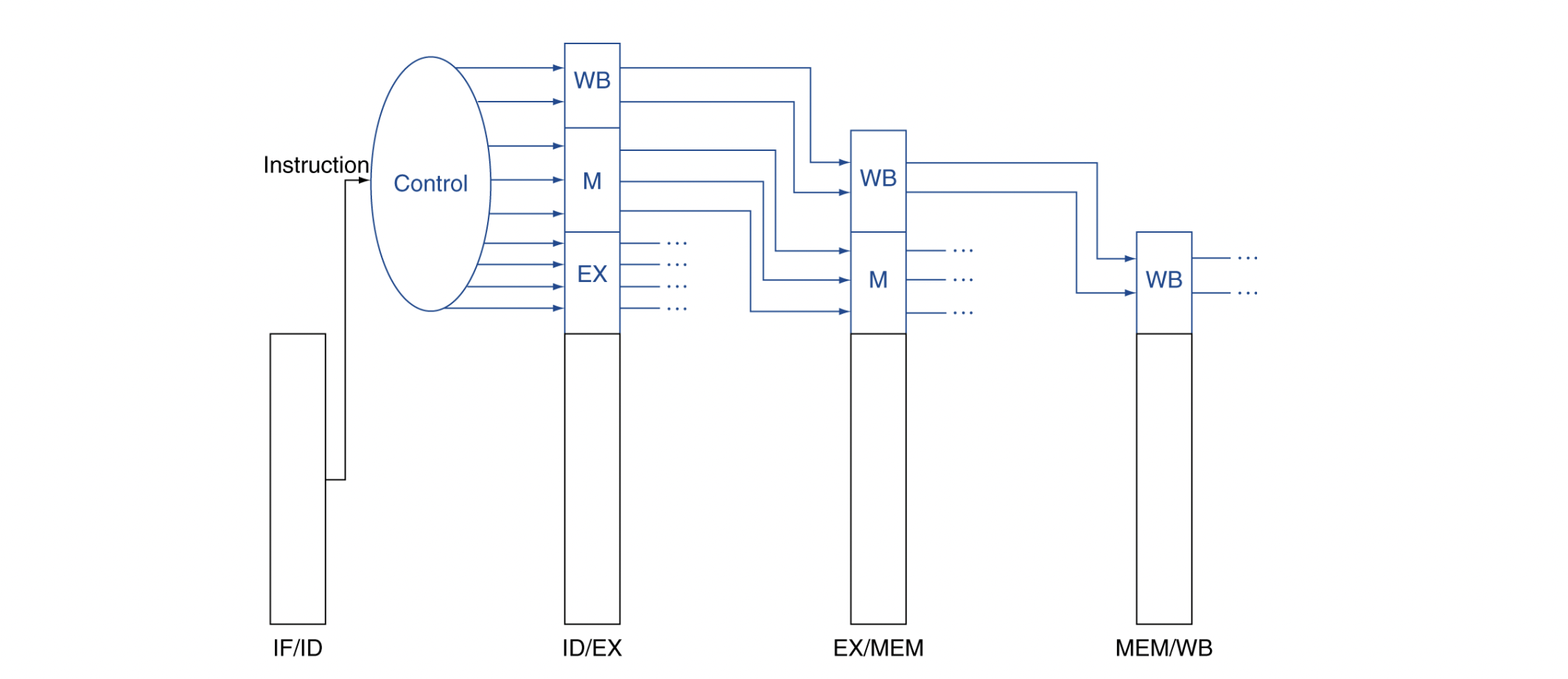

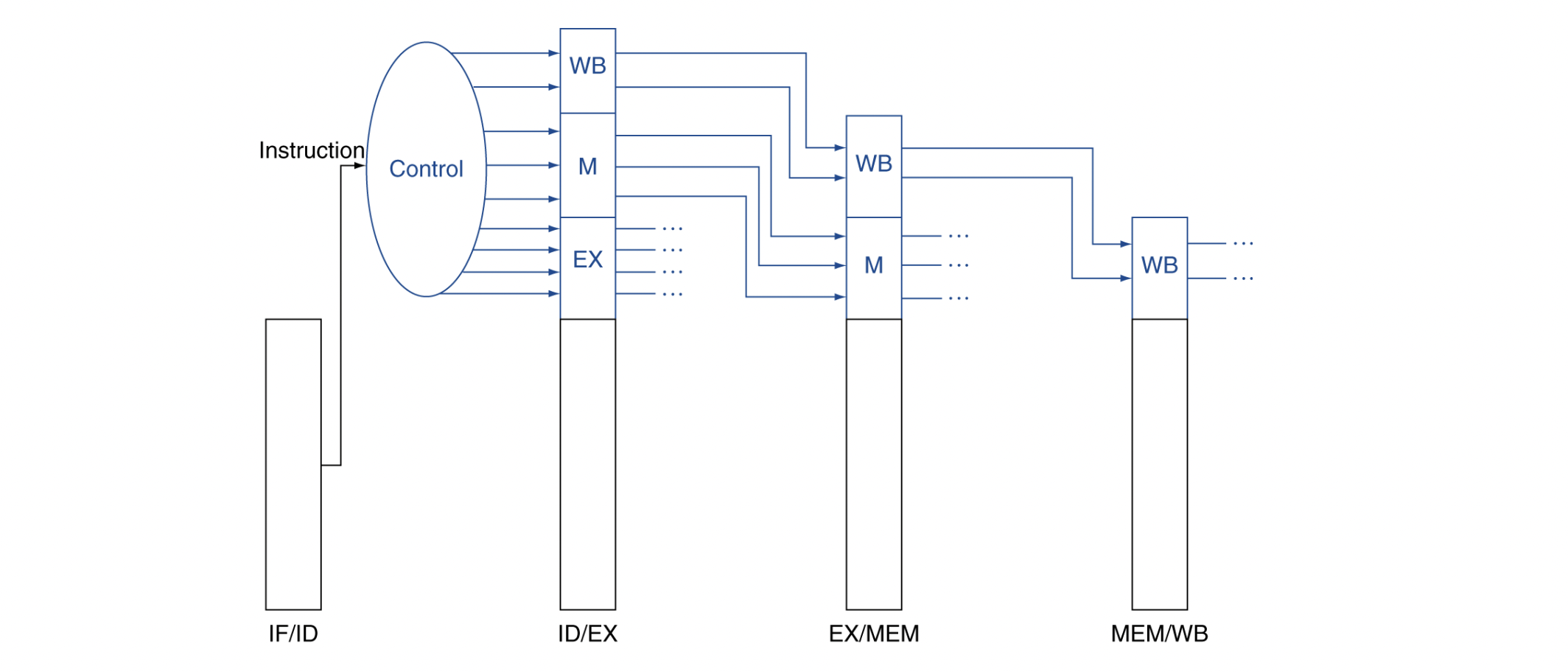

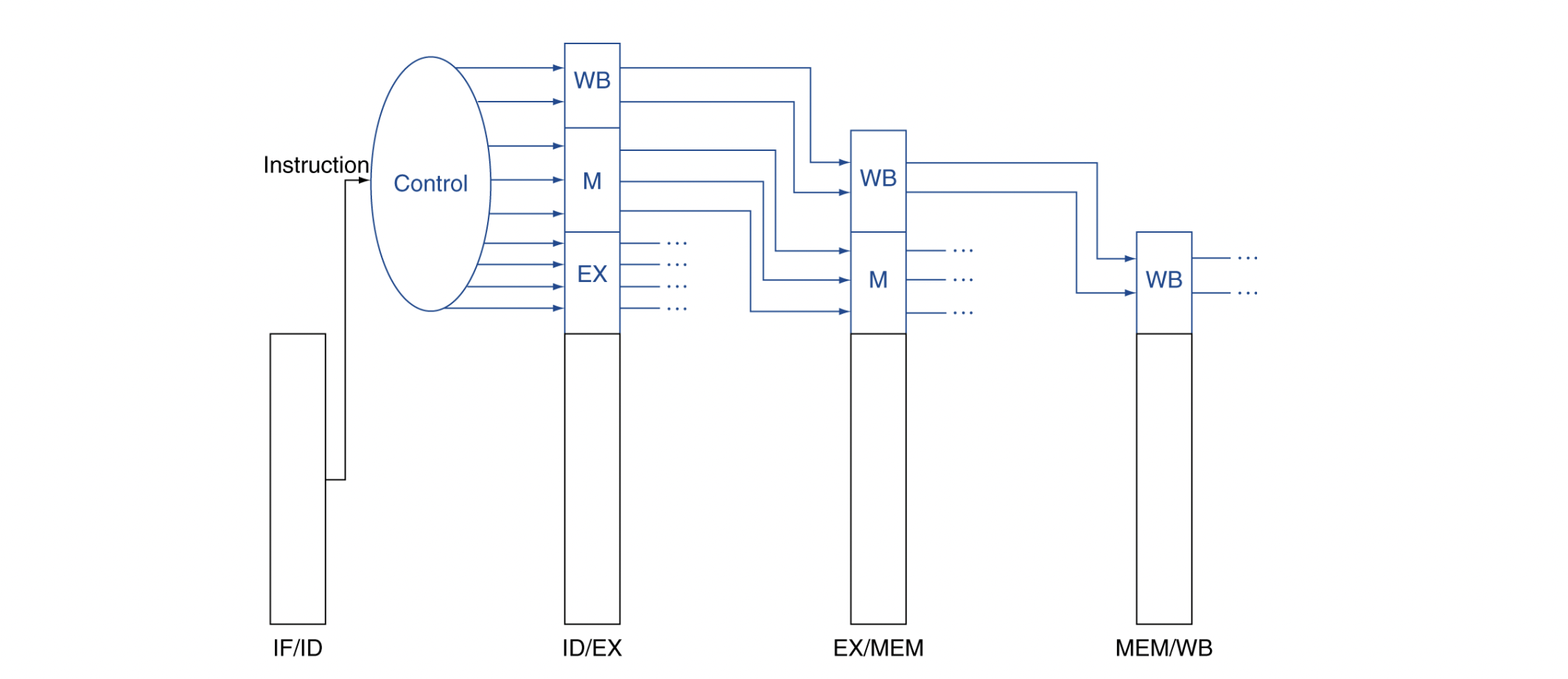

Pipelined Control

- 필요한 control signal들을 pipeline register를 통해 이동한다.

- 소비된 signal은 더이상 다음 stage로 이동하지 않는다

![업로드중..]()

단계별 control signal

IF

- instruction memory를 읽고 PC값을 쓰기 위한 제어신호들은 항상 인가되므로 여기서는 따로 제어할 것이 없다

ID

- 매 clock cycle마다 같은 일이 일어나기 때문에 설정할 제어선이 없다

EX

- RegDst, ALUOp, ALUSrc

- 목적지 register와 ALU 연산을 선택하고,

Read data2와 sign-extension된 수치 중 하나를 ALU의 입력으로 선택한다

MEM

- Branch, MemRead, MemWrite

WB

- MemtoReg, RegWrite

- register file에 ALU 결과를 보낼 것인지 메모리 값을 보낼 것인지 결정하고,

선택된 값을 register에 쓰게 한다