Introduction

- CPU 성능의 세 가지 주요 요인

- Instruction Count (명령어 개수)

- Determined by ISA and compiler

(컴파일러와 명령어 집합 구조가 결정한다)

- Determined by ISA and compiler

- CPI (명령어 당 클럭 사이클 수) & Cycle time (클럭 사이클 시간)

- Determined by CPU hardware

(프로세서의 구현 방법에 따라 결정된다)

- Determined by CPU hardware

- Instruction Count (명령어 개수)

- Two MIPS implementation

- A simplified version

- A more realistic pipelined version

- 핵심적인 MIPS 명령어 집합의 부분집합을 구현한다

- Memory reference (메모리 참조) : lw, sw

- Arithmetic / logical (산술/논리) : add, sub, AND, OR, slt

- Control transfer (분기) : beq, j

- 모든 명령어의 처음 두 단계

- 프로그램 카운터(PC)를 프로그램이 저장되어 있는 메모리에 보내서

메모리로부터 명령어를 가져온다. - 읽을 레지스터를 선택하는 명령어 필트를 사용해 하나 또는 두 개의 레지스터를 읽는다. (lw는 하나, 대부분은 두 개의 레지스터를 읽는다)

- 프로그램 카운터(PC)를 프로그램이 저장되어 있는 메모리에 보내서

- 점프 명령어를 제외한 모든 명령어 종류는 레지스터 읽은 후 ALU를 사용한다

- Memory reference : 주소 계산(calculate address)을 위해 ALU 사용

- Arithmetic / logical : 연산을 수행하기 위해 ALU 사용

- Control transfer : 비교하기 위해 ALU 사용

- ALU 사용 후 명령어 실행을 끝내는 데 필요한 행동들은 명령어 종류에 따라 다르다.

- Memory reference : 메모리에 접근한다

- 저장 : 데이터를 기록하기 위해

- 적재 : 데이터를 읽기 위해

- 산술/논리 명령어와 적재 명령어는 ALU나 메모리에서 온 데이터를 레지스터에 써야 한다

- Control transfer

: 비교 결과에 따라 다음 명령어의 주소를 바꿀 수도 있고, PC값을 4 증가시켜 다음 명령어의 주소를 갖게 할 수도 있다

- Memory reference : 메모리에 접근한다

CPU

- CPU Overview

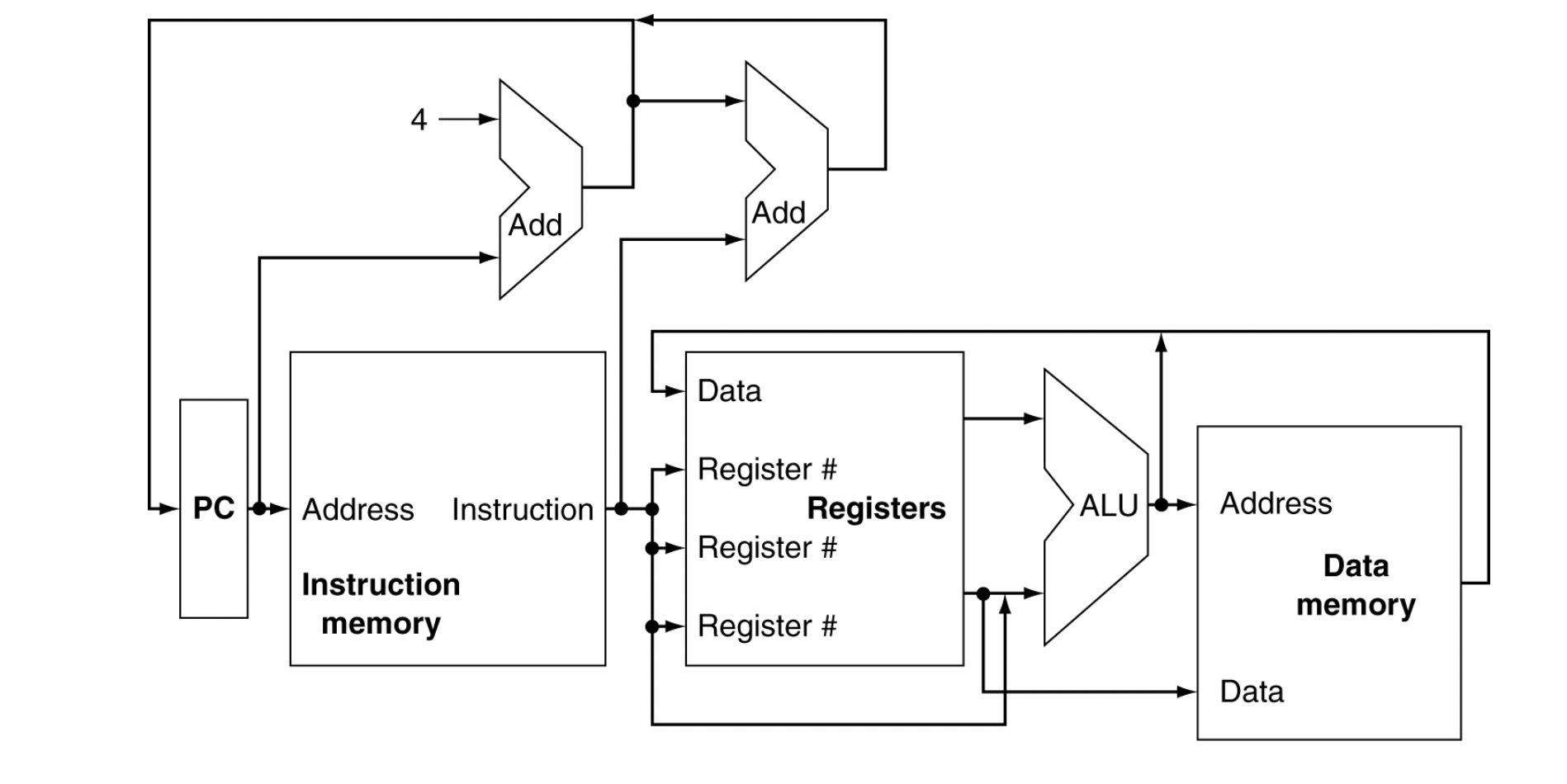

-

맨 왼쪽 PC(Program Counter)는 다음에 실행할 instruction의 주소를 가리키고 있다.

-

Instruction Memory는 data memory(stack, heap, static)의 아래 부분이다. 일반적으로 알고 있는 '코드' 부분이라고 보면 될 듯 하다.

add $1, $2, $3와 같은 코드가 들어있다. -

Instruction Memory와 Register 사이에는 원래 instruction의 의미를 알기 위한 약간의 장치가 있다. (little bit for decoding)

-

코드에서 사용하는 register를 Registers에서 찾아서 가리킨다.

-

연산이 필요한 register를 ALU에 input으로 넣어 결과를 얻는다.

$2와 $3가 input으로 들어가서, ALU의 결과값으로 그 합을 받고,

이 결과값을 다시 돌아가서 $1에 저장하게 된다.

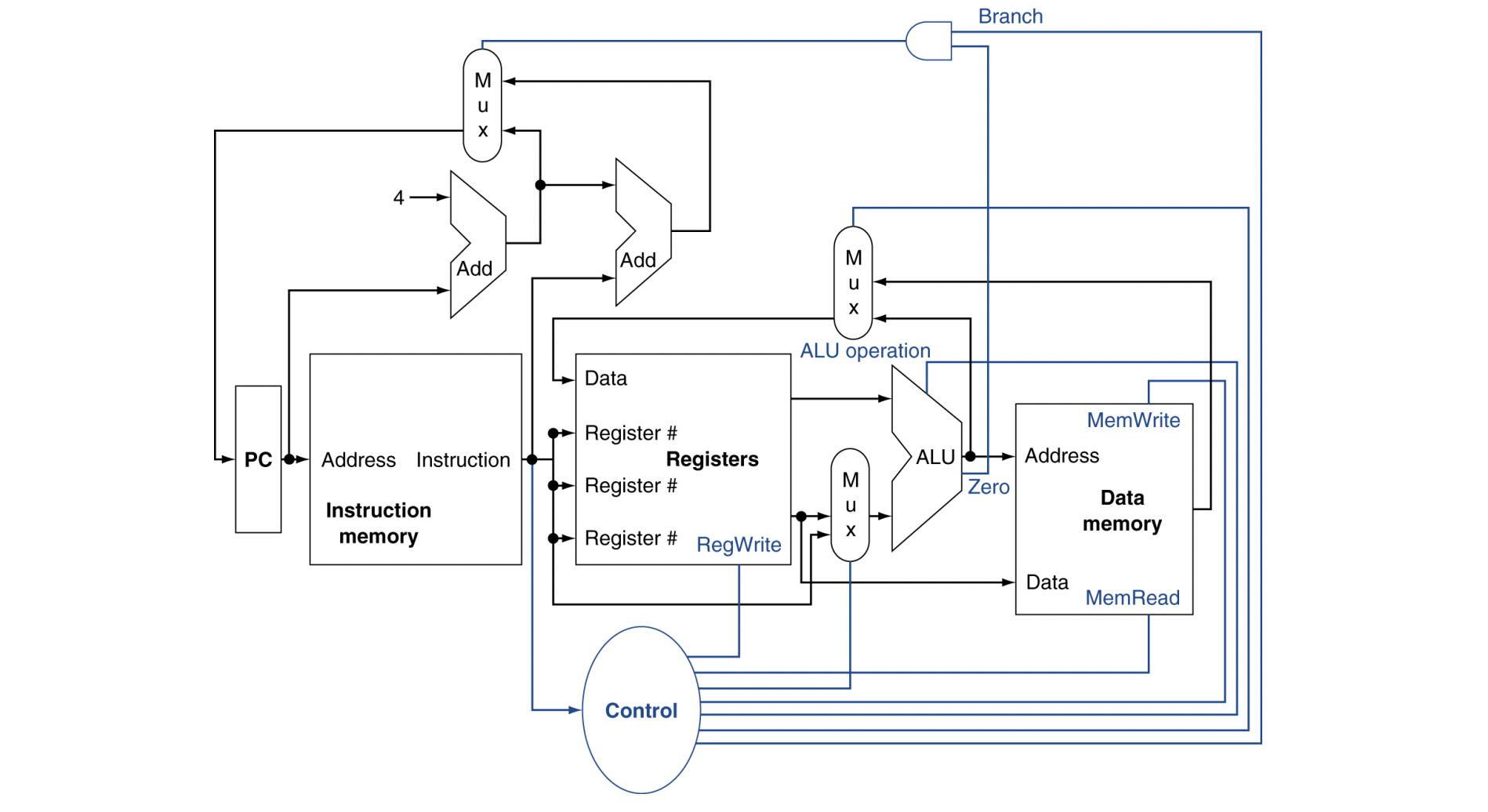

Multiplexor & Control

- 서로 다른 곳에서 나온 데이터가 같은 유닛으로 갈 때, 실제로 이들을 단순히 연결할 수는 없다

- 멀티플렉서를 이용해 다수의 근원지 중 하나를 선택하여 그것만 목적지로 보낸다

- 제어선의 값에 따라 여러 개의 입력 중 하나를 선택한다.

-

맨 위에 있는 MUX는

어떤 값이 새 PC 값이 될 지를 결정한다.

(PC+4 또는 분기 목적지 주소) -

가운데에 있는 MUX는

ALU 출력과 데이터 메모리 출력 중 어떤 것을 레지스터에 쓸 지 결정한다.

ALU 출력 : 산술/논리 명령어의 경우

메모리 출력 : 적재 명령어의 경우 -

맨 아래에 있는 MUX는

ALU의 두 번째 입력을 레지스터 또는 명령어의 변위 필드 중 어디에서 받을 지 결정한다.

레지스터 : 산술/논리, 분기 명령어의 경우

명령어 변위 필드 : 적재 또는 저장 명령어

Logic Design

Basic

-

Information encoded in binary

- Low voltage = 0, High voltage = 1

- One wire per bit

- Multi-bit data encoded on multi-wire buses

-

두 가지 종류의 논리 소자

- Combinational element (조합 소자)

- 출력이 현재의 입력에만 의존

- 같은 입력이 주어지면 항상 같은 출력 (Output is a functino of input)

- State (sequential) element (상태 소자)

- 내부 기억장소가 있다.

- 컴퓨터 플러그 뺐다가 켜도 괜찮다

- 맨 위 그림의 Instruction memory, Registers, Data memeory가 예시이다

Element

Combinational Elements

- AND gate (Y = A & B)

- Adder (Y = A + B)

- Multiplexer (Y = S ? 1 : 0)

- ALU(Arithmetic / Logic Unit) (Y = F(A, B))

Sequential Elements

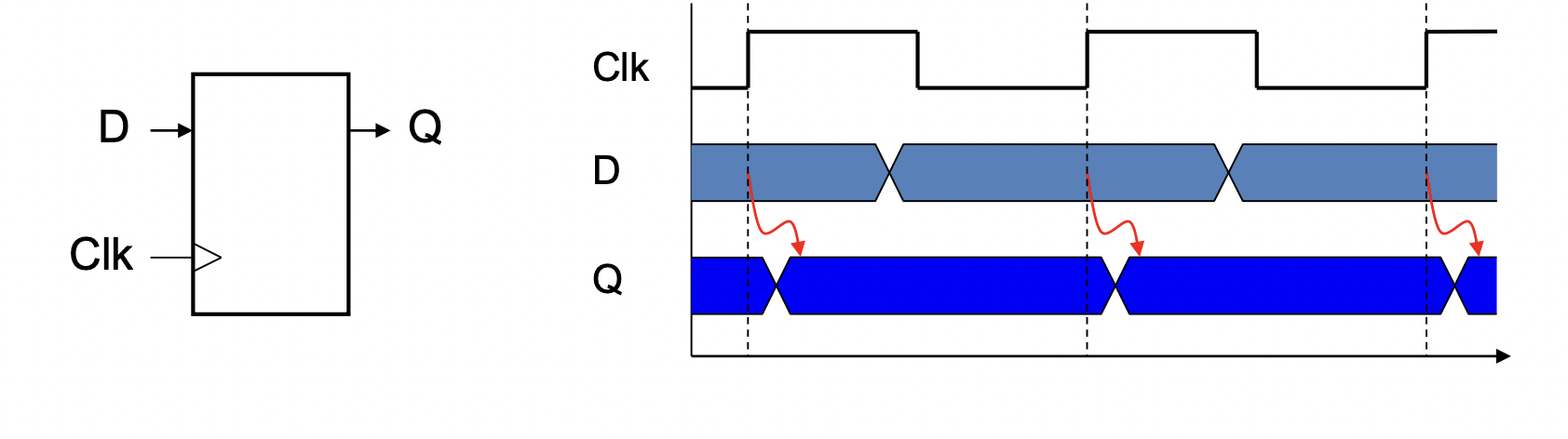

Register : store data in a circuit

- D flip flop

- clock signal을 이용해서 저장된 값을 언제 update할 지 결정한다

- Edge-triggered : clock이 0->1 로 바뀔 때 update한다 (positive edge)

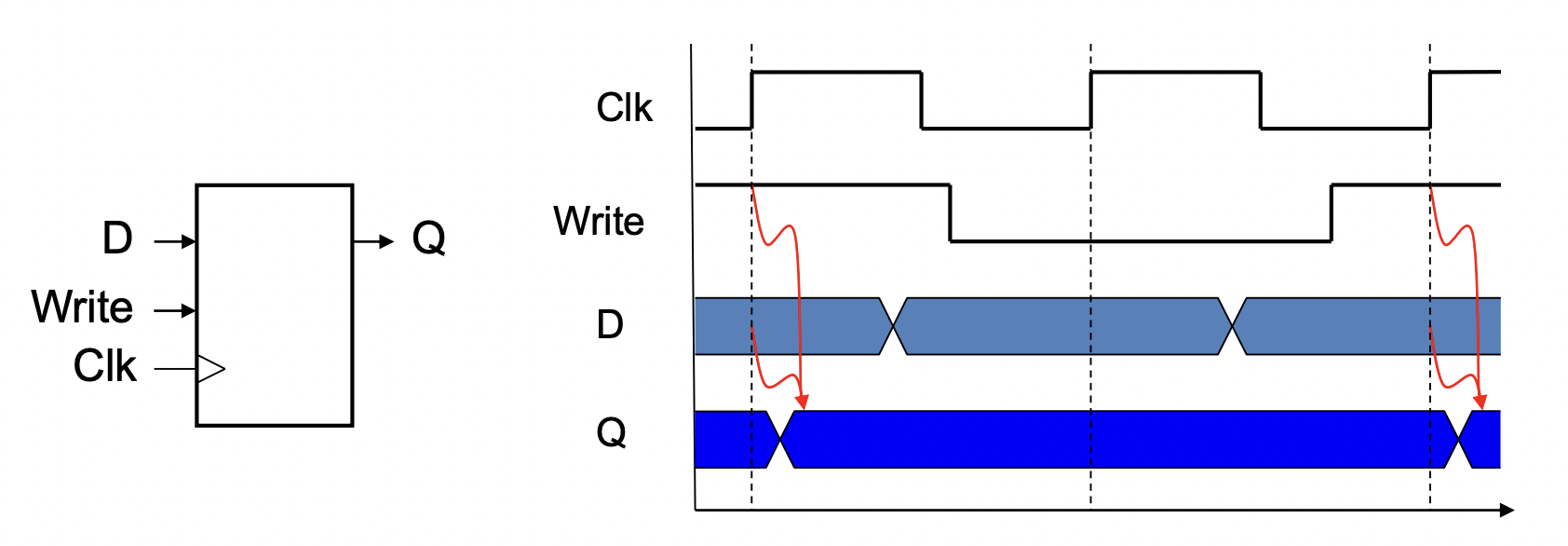

Register with write control

- write control input이 1일 때 + clock edge에 update한다

- 저장된 값이 나중에 필요한 경우에 이용된다.

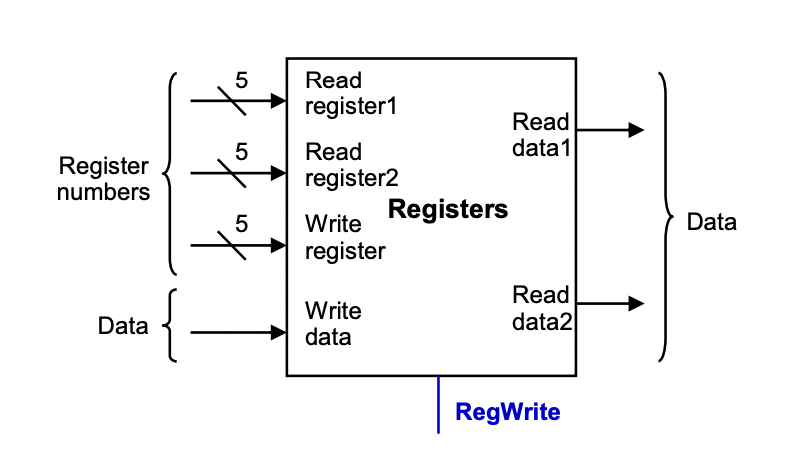

Storage element : register file

- Register file은 32개의 register로 구성되어 있다 :

- 2개의 32 bit output busses : Read data1 and Read data2

- 1개의 32 bit input bus : Write data

- Register는 다음과 같이 선택된다 :

- Read register1이 Read data1에 들어갈 register를 선택한다

- Read register2가 Read data2에 들어갈 register를 선택한다

- Write register는 RegWrite = 1일 때, Write data를 통해 쓰여질 register를 선택한다

- Clock input (CLK)

- CLK input is a factor only for write operation

(data changes only on falling clock edge)

- CLK input is a factor only for write operation

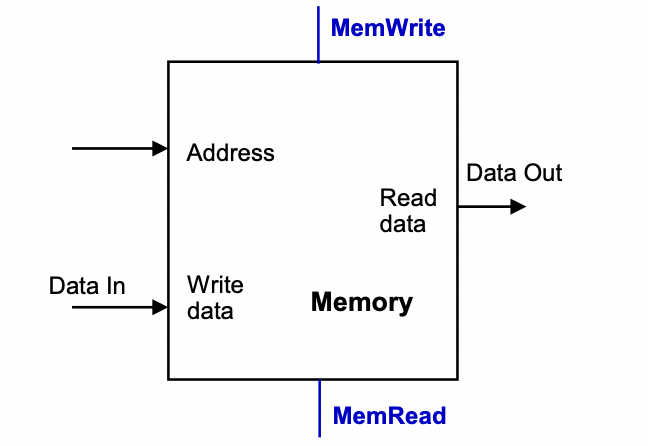

Storage element : Memory

- Memory는 2개의 bus가 있다 :

- 1개의 output bus : Read data (data out)

- 1개의 input bus : Write data (data in)

- 주소(Address)

- MemRead = 1일 때, selects the word to put on Data Out

- MemWrite = 1일 때, the word to be written via the Data In

- Clock input (CLK)

- CLK input is a factor only for write operation

- During read, behaves as combinational logic block

- valid address -> Data Out valid after "access time"

- Minor simplification of reality

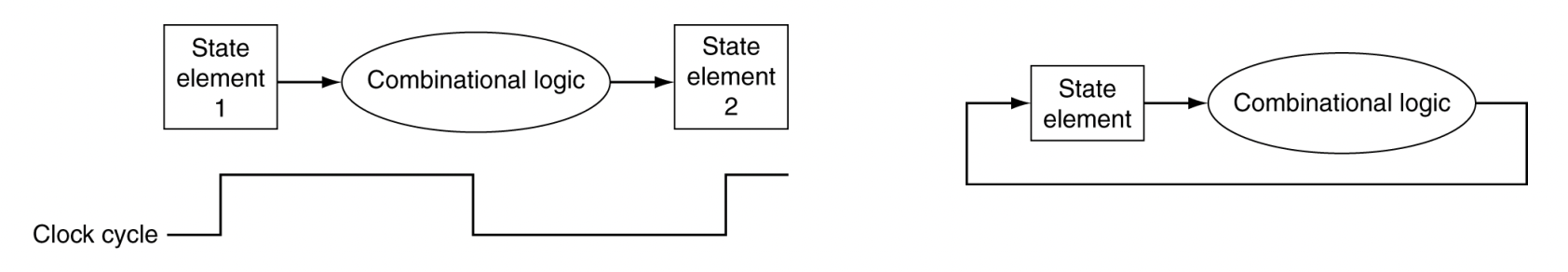

Clocking Methodology

- 신호를 언제 읽을 수 있고, 언제 쓸 수 있는지 결정한다

- state element에서 입력을 받고 state element로 출력한다.

- 첫 번째 그림은 조합회로를 둘러싼 두 개의 상태소자를 보여준다.

- 이 회로는 하나의 clock cycle에 동작한다

- 즉, 모든 신호가 state element1에서 나와 조합회로 거치고 state element2로 전달되는 데 하나의 clock cycle이 걸린다.

- 이 때, 신호들이 상태소자2에 도착하는 데 필요한 시간이 clock cycle의 길이를 정의한다.

Longest delay determines clock period

- 두 번째 그림은 edge triggered clocking methodology를 보여준다

- 레지스터 내용을 읽고 그 값을 조합회로로 보내고 같은 레지스터에 쓰는 작업 모두가 한 clock cycle에 일어난다.