개인 공부용 강의 정리

Basic Elemets

1-1 Basic elemets

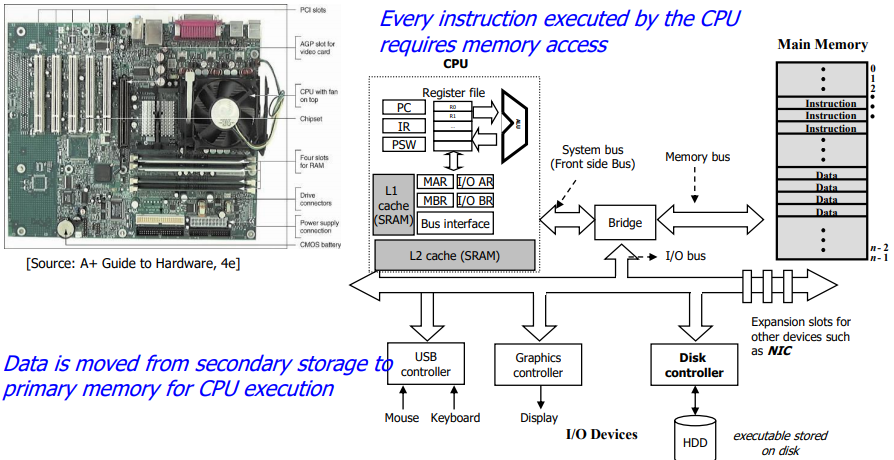

CPU를 통해 처리되는 모든 명령어들은 메모리에 접근한다.

데이터는 CPU가 실행되면서 보조저장장치에서 중앙저장장치로 이동한다.

1-2 Processor

- Arithmetic/logic unit(ALU) : 대수연산과 논리연산을 수행

- Central processing unit(CPU) : ALU와 control unit, register들을 이용하여 명령어를 처리하는 하드웨어

현대에 와서 3GHz 이상으로 frequency를 높히는 것은 한계에 도달하였다. 따라서 병렬처리를 이용해 성능을 높히는 방향으로 나아가고 있다.

frequency가 높을수록 소모 전력도 높아지기 때문에, 좋은 성능이 요구되지 않고 베터리의 오랜 지속이 요구되는 환경에서는 PIC와 Z80의 수요가 여전히 많다.

- GPU(Graphical Processing Units) : 행렬을 이용한 연산 수행 장치. 정수 연산을 넘어서는 그래픽 분야에서의 연산을 빠르게 하기 위해 사용되었으나, 최근 인공지능 분야에서 사용하기 위해 활발히 연구중에 있다.

- SoC(System on Chip) : DSP, GPU, cedec, main memory, CPU, cache, NPU 등 여러 구성 요소들을 하나의 칩에 넣어둔 것을 의미

↑ 4개의 big core와 4개의 little core로 구성된 Big-little solution octa-core

1-3 Memory

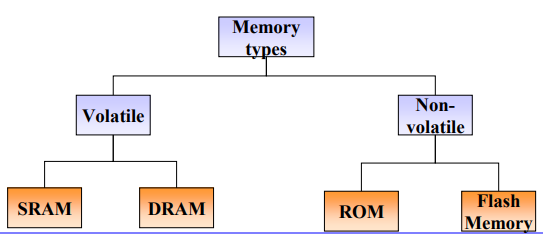

- Random Access Memory; 휘발성

- Static RAM : 높은 연산속도, No refresh required(Capacitor가 없기 때문), Poor density(6T), 비쌈

- Dynamic RAM : 비교적 느린 연산속도, High density(1T1C)

- Hard Disk drive; 비휘발성(a kind of magnetic storage media)

HDD, 플로피디스크, magnetic tape, 마그네틱형 신용카드 등

최근 접근속도를 높히기 위해 헤드와 플래터 사이의 거리를 최대한 가깝게 하고, 빨리 돌아가도록 하는 방향으로 연구가 진행 중이다. - Flash memory; 비휘발성

기존 MOS 트랜지스터에 Floating Gate를 추가하여 데이터를 저장하는 방식. 휴대전화 등 부피가 큰 Hard Disk drive를 쓸 수 없는 휴대형 기기에서 주로 사용.

Processor Register

2-1 General-purpose register(범용-)

- 메인메모리를 참조를 최소화

- Register file(or bank) : 모든 범용 레지스터의 집합

2-2 Special-purpose register(특수목적-)

- Program counter(PC) : 다음에 fetch될 명령어의 주소 저장

- Instruction register(IR) : PC에 저장되있는 주소의 명령어를 가져옴

- Program status word(PSW) : 상태정보를 갖는 레지스터(Privilaged states, Condition code)

- Memory address register(MAR) : 현재 수행되고있는 명령어가 요구하는 데이터의 주소를 저장

- Memory buffer register(MBR) : MAR에 저장된 정보가 가르키고 있는 곳의 데이터를 가져옴

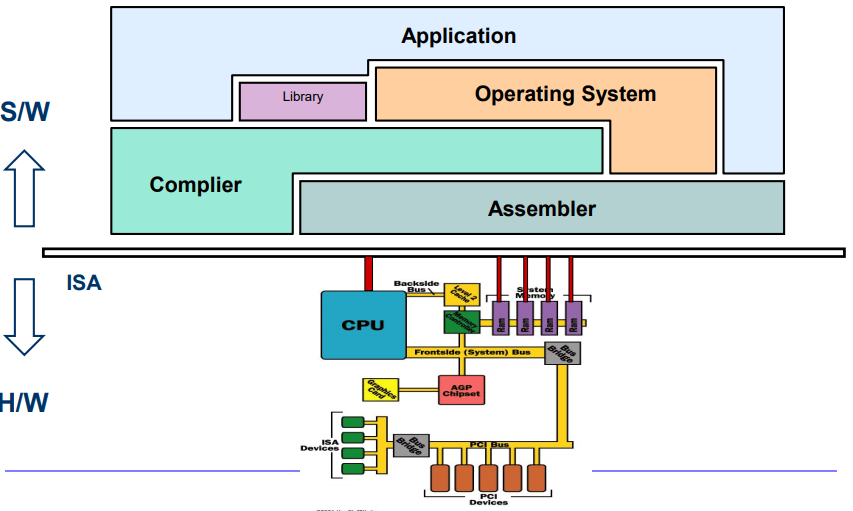

Instruction Set Architecture

컴퓨터의 실제 구조를 추상화한 것. SW의 최하단이라고 볼 수 있다.

프로그래머가 보는 컴퓨터의 시스템으로 개념적 구조(state; register + memory)와 기능 수행(operations; instructions)로 나눌 수 있다.

Instruction Execution

4-1 프로그램

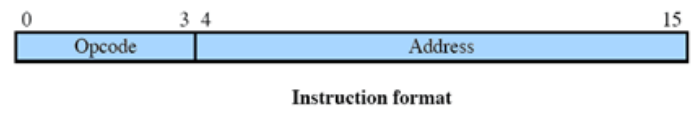

4-2 Instruction format

opcode의 길이, 피연산자의 수와 길이를 나타낸다.

ex) 16비트에서 사용되는 format의 예시

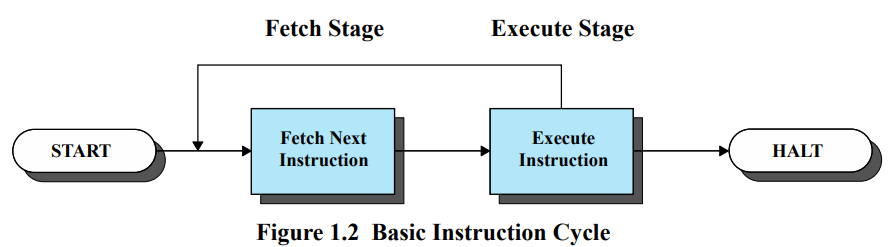

4-3 Instruction fetch

PC에 있던 주소값을 참조하여 IR에 명령어를 저장

4-4 Instruction decode and execute

명령어를 해석하여 주어진 명령어를 수행(Data processing, control, processor-memory, processor-I/O)

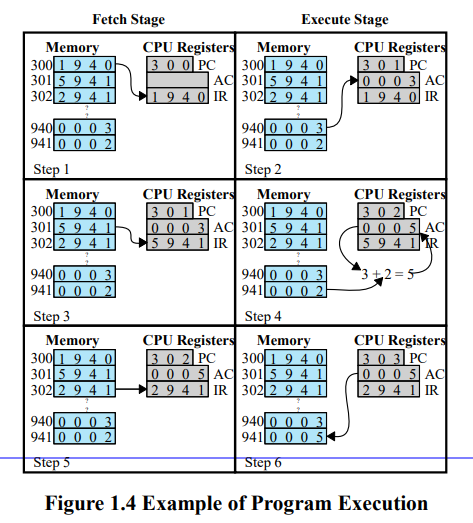

AC : 누산기 / 0001 = 메모리에 저장된 값을 AC에 적재 / 0010 = AC에 저장된 값을 메모리에 저장 / 0101 = 메모리에 저자된 값을 AC에 더함

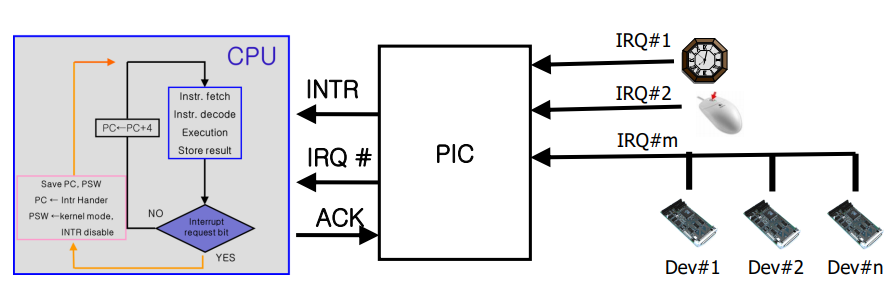

Programmable Interrupt Controller

I/O device는 Interrupt Request(IRQ) 선을 가지고 있다. 이는 unique할 수도 있고 공유될 수도 있다.

이는 PIC로 전달되며(CPU에는 연결할 수 있는 회로의 수가 제한되어 있기 때문), PIC는 INTR 발생 여부와 해당 벡터를 CPU에 전달한다. PIC의 기능을 정리하자면 다음과 같다.

- I/O device의 Intr requset(IRQ)를 벡터로 변환한다.

- I/O device로부터의 intr을 CPU로 전달

- CPU로부터 ACK가 올 때까지 대기

- 여러 개의 IRQ가 전달됐을 때, PIC나 CPU로의 전달을 mask(disable)할 수 있다.(programmable; 우선순위 지정)

↑ Interrupt가 CPU로 전달되기 까지의 회로

↑ Interrupt가 CPU로 전달되기 까지의 회로

↑ cascading 가능한 PIC

↑ cascading 가능한 PIC

Interrupts

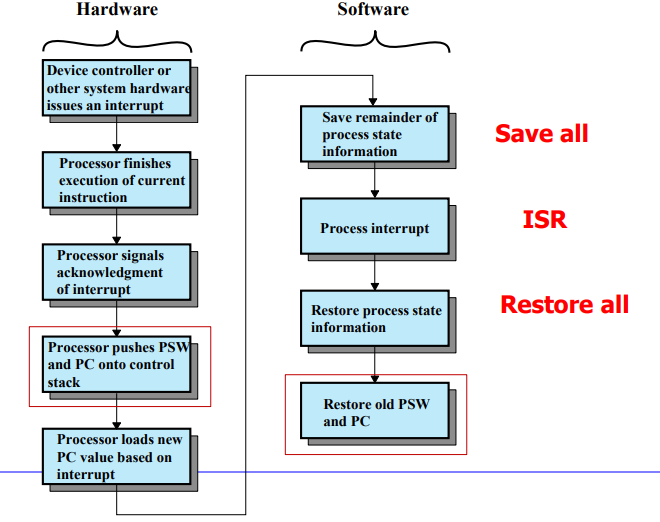

6-1 Interrupt mechnism

탄생 배경

- 대부분의 I/O device들은 프로세서보다 느리다.

- 따라서 프로세서들은 device들이 결과를 보내주기 전까지 멈춰있어야 한다.

프로세서의 사용률을 높히기 위해 Interrupt Handler를 통한 메커니즘 탄생

↑ Interrupt Stage가 추가된 Instruction Cycle. 회색으로 색칠된 단계에서 PC에 저장된 값이 Interrupt Handler의 주소로 바뀜

↑ Interrupt Stage가 추가된 Instruction Cycle. 회색으로 색칠된 단계에서 PC에 저장된 값이 Interrupt Handler의 주소로 바뀜

↑ 프로그램 실행 도중 device에서 intr가 발생했을 때의 알고리즘 순서도(주황색 화살표)

↑ 프로그램 실행 도중 device에서 intr가 발생했을 때의 알고리즘 순서도(주황색 화살표)

6-2 Interrupt handler

- interrupt hander

- OS 내에 어셈블리어로 구현되어 있다(in Linux).

- 커널 진입점이라고 불린다.(Linux/arch/i386/kernel/entry.S)

- 레지스터들의 정보를 저장(save all)한 후, IRQ 함수를 호출한다.

- IRQ 함수 내부에서 ISR이 모두 수행된 후, 저장했던 모든 정보를 restore한다.

- interrupt service routine(ISR)

- C언어로 구현되어 있다(in Linux)

- IDT(interrupt descriptor table)에 저장되어 있는 ISR 함수의 주소값을 통해 호출된다.

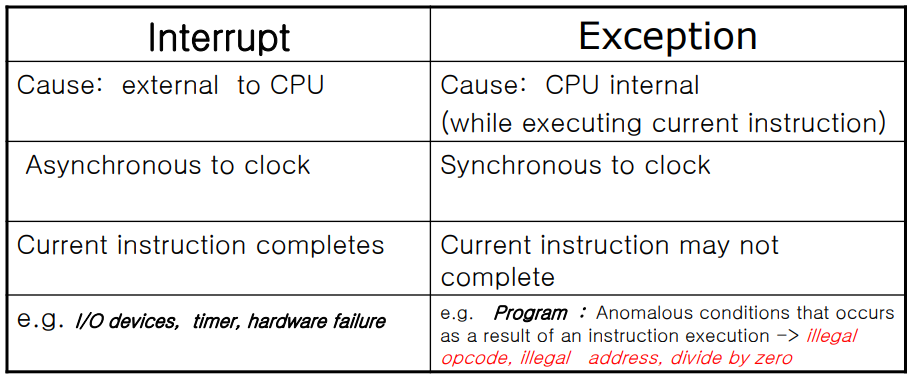

6-3 Interrupt and exeption

Interrupt는 다음과 같이 두 가지로 분류된다.

- Asynchronous interrupts(i.e. (external) interrupt)

- 외부의 HW 디바이스에 의해 생성됨

- Synchronous interrupts(i.e. internal/software interrupt, exception, trap)

- CPU에 의해 생성됨

- segmentation faults, page faults, divide by zero에서 발생되는 예외

21.03.08 Instruction Execution까지 정리 완료

21.03.11 Interrupts까지 정리 완료