OS 수업 정리S 수업 정리

Interrupts

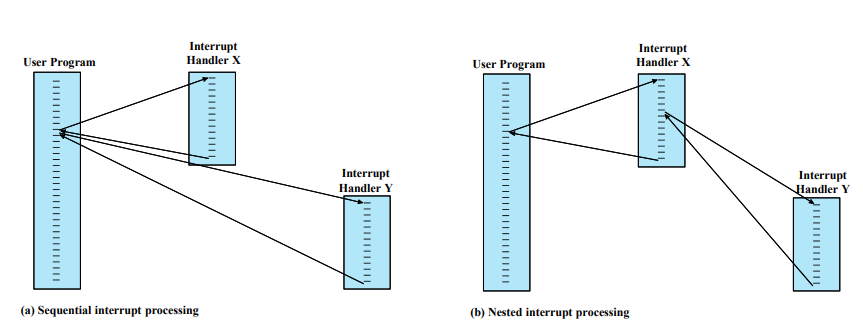

6-4 Multiple Interrupts

-

Sequential interrupt processing(순차 -)

- 현재의 intr를 처리할 때까지 새로운 intr 요청을 pause/pending한 후 처리를 완료했을 때 재개하는 방식

-

Nested interrupt processing(중첩 -)

- intr 간 우선순위를 사용하는 방식

- 우선순위가 높은 intr가 들어오면 커널 스택영역에 저장하여 먼저 해결한 후 pop

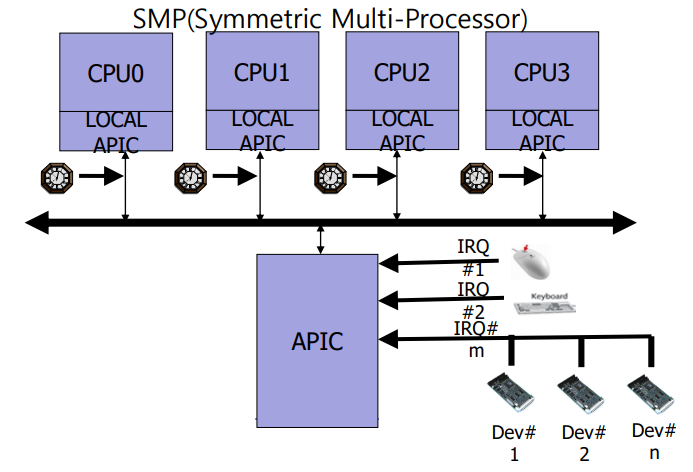

6-5 APIC for SMP

- SMP(Symmetric Multi-Processor)

- 각 CPU들은 메모리와 I/O device를 공유함; 동등한 level에서 동등한 기능을 제공하는 구조

- Advanced PIC(APIC)

- IRQ가 발생했을 때 CPU를 select한 후, 해당 IRQ를 CPU(corresponding local APIC)에 보내주는 기능을 수행

- Local APIC(LAPIC)

- CPU마다 하나씩 위치해, 내부 IRQ(ex. timer intr)가 발생했을 때 처리. External APIC과 연결되어있다.

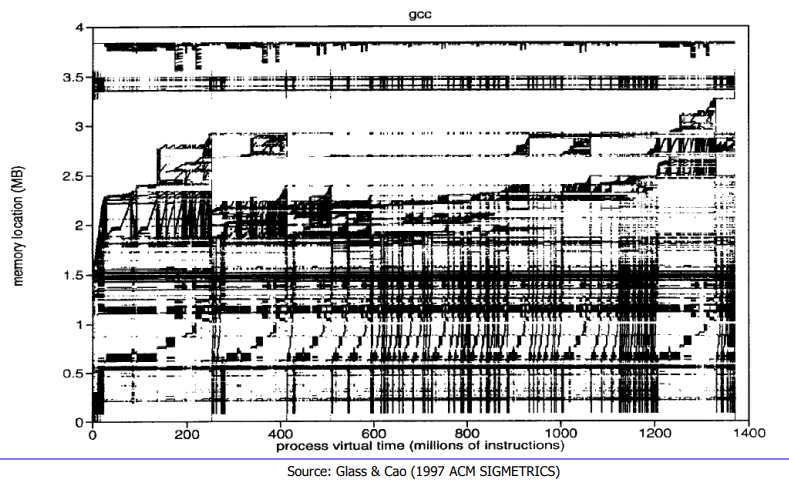

Memory Hierarchy

7-1 Memory hierarchy

메모리의 speed와 cost(capacity도 추가될 수있음) 간 양립불가능의 문제를 해결하기 위해 메모리를 계층화하기 시작.

-> 최고계층 메모리의 접근 시간과 최저계층 메모리의 비용을 제공하는 가상의 메모리 기술 제공을 목표로 함

계층 구조를 만족하면서도 두 가지의 locality(temporal, spacial)를 보인다.

7-2 Terminology

- Hit : 상위 계층에서 목표 데이터가 발견되는 것을 의미

- Hit rate

- Hit time

- Miss : 하위 계층에서만 목표 데이터가 발견되는 것을 의미

- 상위 계층으로 데이터를 fetch한 후 process 재개

- Miss rate = 1 - hit rate

ex) L1의 접근시간이 0.1µs, L2의 접근시간이 1µs라 가정하고 95%의 메모리 접근이 L1 계층에서 발견된다고 했을 때, 평균 접근시간 T

T = 0.95(0.1µs) + 0.05(0.1µs + 1µs) = 0.15µs

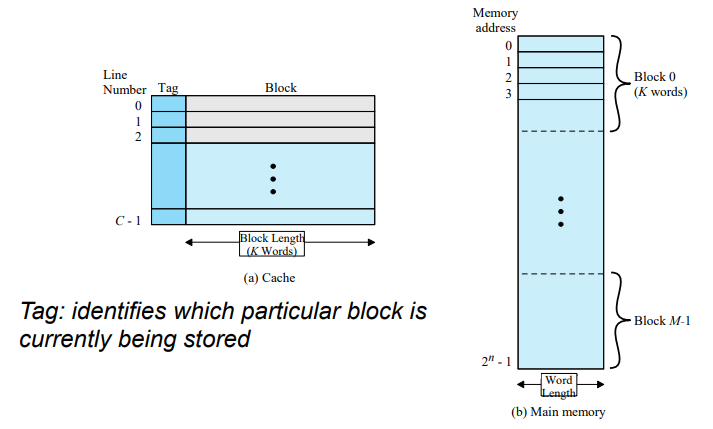

Cache Memory

8-1 Terminology

- Cache

- SRAM의 빠르기를 가지면서도 DRAM의 사이즈와 비용을 갖는 '가상' 메모리를 제공하기 위한 장치(혹은 DRAM의 장점과 Disk의 장점을 동시에 제공하는 메모리를 제공하기 위한 장치)

- Momory bandwidht를 줄임으로써 hit rate를 올린다.

- Blocks / Slots

- block : main 메모리의 처리 단위. 블록의 크기가 라고 했을 때, main 메모리에는 개의 블록이 존재한다.

- slot : 캐시 내에 있으면서 block 크기를 갖는 구역을 slot(or line)이라 칭한다. 슬롯의 개수 c는 block의 개수 m보다 무조건 작다. 한편 slot들의 집합을 set이라 한다.

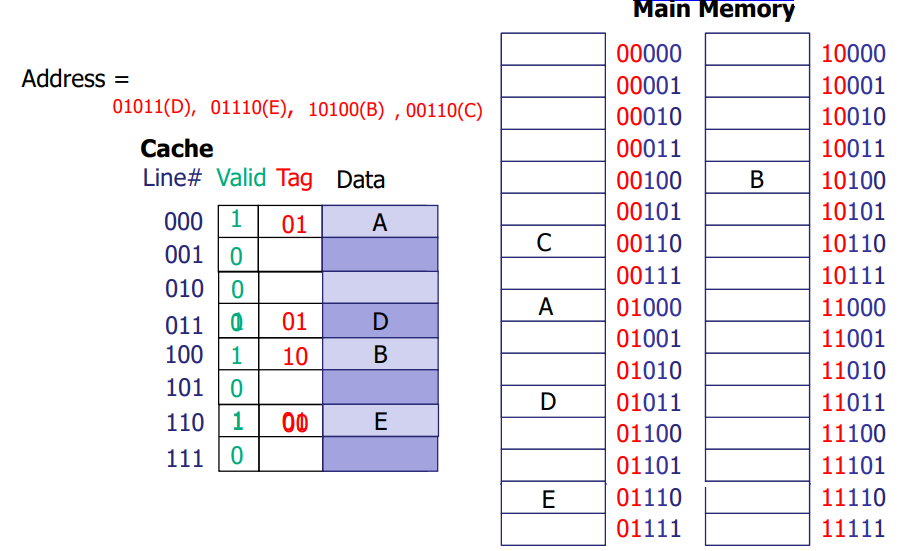

8-2 캐시 구성 방식

- Direct mapped Cach

- 각각의 block들이 하나의 cache block에 사상되는 방식

- 각각의 block들이 하나의 cache block에 사상되는 방식

- N-way set associative caches

- hit rate을 높히기 위해 N개의 라인을 하나의 set으로 구성하는 방식(allow multiple entries, 사진 : 2way set associative)

- hit rate을 높히기 위해 N개의 라인을 하나의 set으로 구성하는 방식(allow multiple entries, 사진 : 2way set associative)

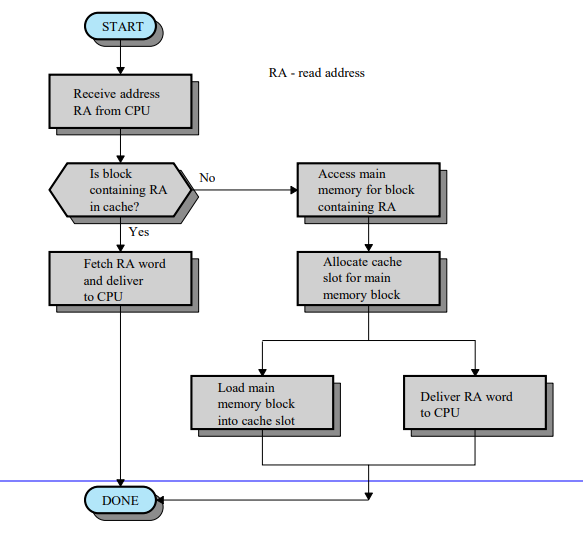

8-3 Read and write

-

read

-

write

- Write-through

- 항상 메인메모리와 캐시 모두에 write를 하는 방식

- 단순하지만 느리고 메모리 traffic을 증가시킨다(write buffer 필요).

- Write-back

- 캐시에만 write을 한 후 적절한 시간에(해당 자리가 다른 자료에 의해 rewrite될 때 등) 메인메모리에 write하는 방식(해당 여부를 확인하는 dirty bit 필요)

- 빠르지만 구현이 어렵고, consistency 문제를 가질 수 있다.

- Write-through

I/O Communication Techniques

9-1 Intro

IO device들은 자신만의 레지스터(= port register, hw)와 device driver(sw)를 갖는다. 드라이버는 명령어들과 명령어가 수행된 후 레지스터로부터 읽고 쓸 데이터를 가지고 있다.

디바이스는 주소값으로 cpu에서 접근이 가능하다. 주소를 표현하는 방식엔 두 가지가 있다.

- Port I/O(I/O instruction) : 일반적인 주소표현방식과 독립적인 주소공간을 갖는다(extra I/O pin). 이를 제어하는 별도의 instruction이 필요하다는 단점이 있다.

- Memory-mapped I/O

- 데이터와 명령어들의 주소가 메모리에 사상되는 방식

- 주소와 데이터 버스를 많이 사용한다는 단점이 있다.(접근이 비교적 느릴 수 있다.)

9-2 I/O communication techniques

입출력 연산을 수행하기 위한 방법에는 세 가지가 있다.

-

Programmed I/O(Polling) : 프로세서가 I/O operation이 끝날 때까지 주기적으로 I/O 모듈의 상태를 확인한다.

io 장치가 빠르다면 효과적이지만, 느리다면 멈춰있는 시간이 길어지게 된다. cpu가 기다리는 동안 다른 일을 하게 되면 pending되고 있는 일의 데이터가 덮어써지거나 없어질 수 있다.

-

Interrupt-driven I/O : I/O 모듈이 데이터를 송수신할 때 프로세서에 interrupt를 일으키는 방식이다.

Polling 방식에 비해 효과적이긴 하지만, 입출력 장치와 메모리가 여전히 CPU를 거쳐 통신한다는 overhead가 존재한다. -

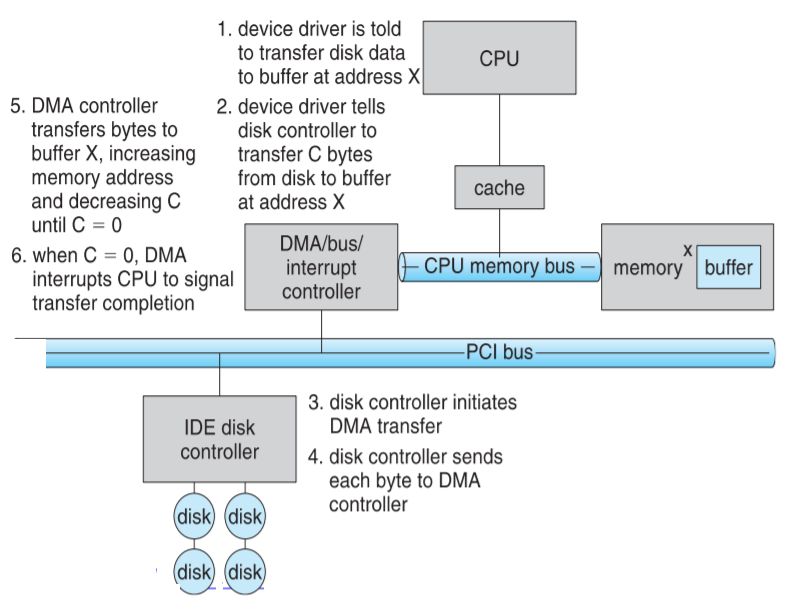

DMA(Direct Memory Access) : CPU의 개입 없이 I/O controller가 local buffer의 내용을 main memory에 직접시키는 접근하는 방식. intr가 빈번하게 일어나는 문제를 해결할 수 있다. 한편 DMA 방식으로 인해 일어날 수 있는 데이터의 충돌 문제는 memory management unit 안에 있는 bus controller로 해결할 수 있다. 대용량 device(ex. 그래픽카드 등)에 적합하다.

- Cycle stealing mode : CPU가 쉬고있을 때 메모리에 접근한다. CPU입장에서 봤을 땐 효과적이지만, DMA controller는 느려지게 된다.

- Block transfer mode : CPU와 대등하게 메모리에 접근한다.(default) 이후 CPU의 메모리 접근을 비교적 긴 시간 동안 제한한다.

OS는 다음의 내용을 포함하는 Command block을 메모리에 write한다.

- source and destination address

- read or write mode

- count of bytes

해당 내용을 수행한 후 완료를 알리는 신호를 CPU에 전송한다.

21.03.18 I/O Communication Techniques 전까지 정리 완료

21.03.22 computer system overview 완성