1. 명령어 수준 병렬성(ILP)

파이프라이닝은 ILP 중 하나이다

ILP를 증가시키기

- Superpipeline : 파이프라인을 더욱 세분화해서 클럭을 높일 수 있다.

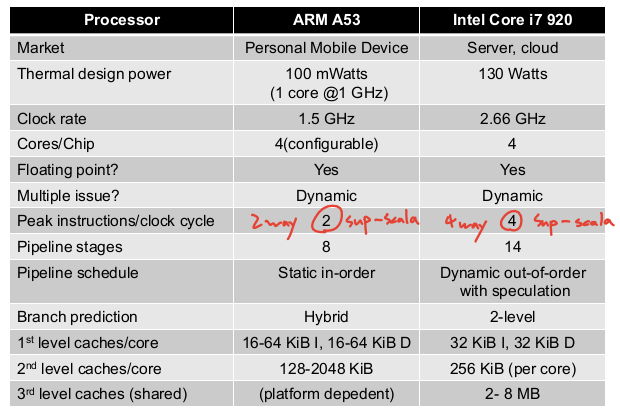

ex) ARM A-8은 14단계의 파이프라이닝을 한다. - Superscalar : 복수의 파이프라인을 도입해 여러 명령어를 단일 클럭에 실행한다. 한 클럭에 하나 이상의 명령어를 처리할 수 있다. 명령어 간 의존성 때문에 성능이 기대치보다 떨어질 수 있다.

ex) ARM A-8은 최대 4개까지 명령어를 동시에 처리할 수 있다.

IPC

- CPI가 1보다 작다면 이의 역수인 IPC를 사용한다.

ex) 4GHz 4 way multiple issue = 16 BIPS, CPI = 0.25, IPC = 4

2. Multiple Issue

Superscalar는 Multiple Issue하여 성능을 높인다

2-1. Static Multiple Issue:

- 컴파일러가 동시 수행할 명령어를 묶는다.

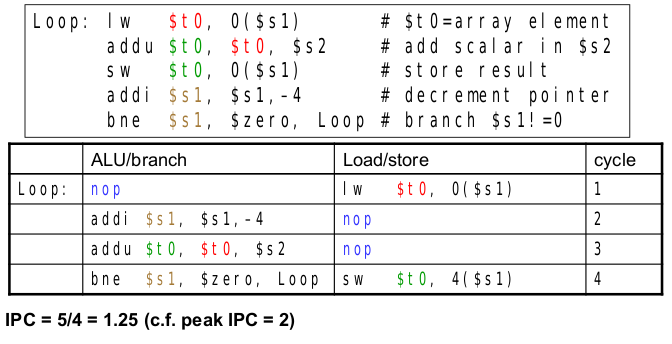

MIPS static dual issue

- ALU/branch -> load/store 순으로 묶음

- 둘 중 하나가 없으면 nop으로 비워놓음

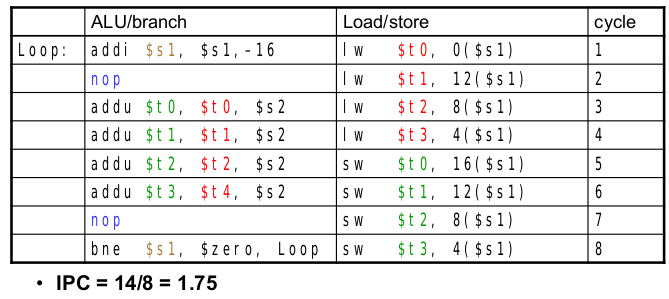

Loop Unrolling

- 루프의 오버헤드를 줄이기 위해 풀어서 실행한다

- 더 빠르지만 레지스터와 코드 크기가 늘어난다

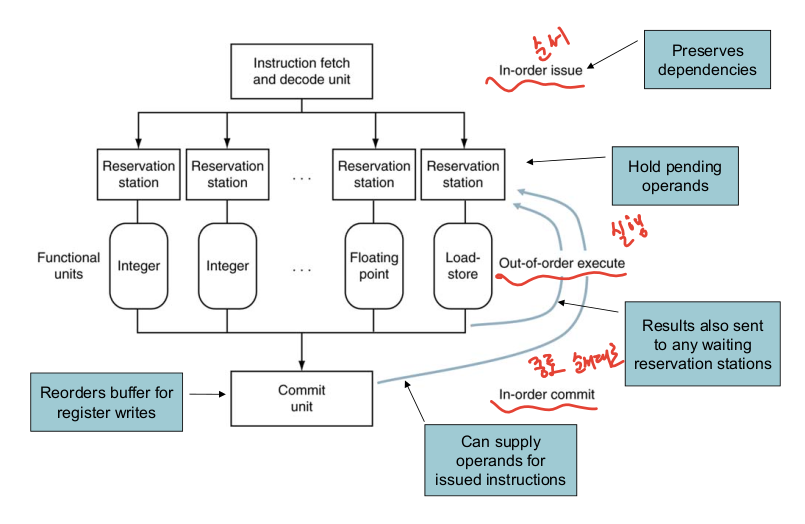

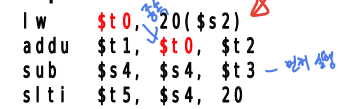

2-2. Dynamic Multiple Issue

- CPU가 명령어 스트림에서 동시에 처리할 명령어를 선택한다.

- out of order로 시행, 결과의 반영은 순서대로 해야한다.

- 이슈 : in order, 실행 : out of order, 반영 : in order

3. Speculation, Out-of-order Execution

3-1. Speculation

- 명령어를 guessing하여 시작

- 맞으면 처리, 틀리면 rollback

- Static, Dynamic Multiple Issue 모두에서 사용

3-2. Out-of-order Execution

- 의존하고 있는 명령어를 기다리지 않고 다른 명령어를 처리하여 stall을 최소화 한다.

- 정리는 이후에 한다.

4. ARM vs x86