▶ 제어 장치

▷ 기능

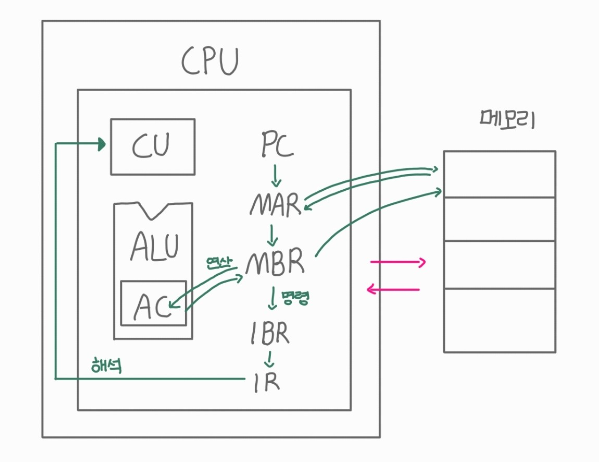

- IR에 있는 명령어를 받아 해석

- 명령어 실행에 필요한 제어 신호들의 발생

- 회로가 아닌 마이크로프로그래밍으로 구현한다!

- 제어 신호들의 종류와 발생 시간은 명령어마다 서로 다름 → 명령어의 수가 많아질수록 제어

유닛의 내부 회로가 복잡해지기 때문

- 제어 신호들의 종류와 발생 시간은 명령어마다 서로 다름 → 명령어의 수가 많아질수록 제어

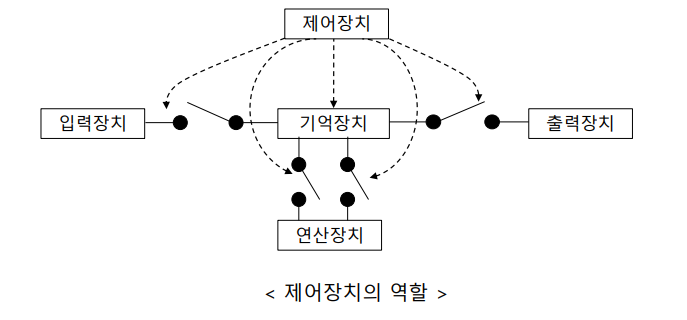

- 프로그램의 입장에서 볼 때 제어장치는 해석장치

- ⭐데이터 입장에서의 제어장치는 데이터를 각 장치에 이리저리 보내주는 역할 (데이터 흐름 제어)

=> 즉, 명령어 해석 장치 뿐만 아니라, 내가 필요한 레지스터로 옮겨갈 수 있는 신호들을 발생시켜준다!

- 마이크로 명령어

- 명령어 사이클에 Line by Line이 마이크로 명령어이다!!!

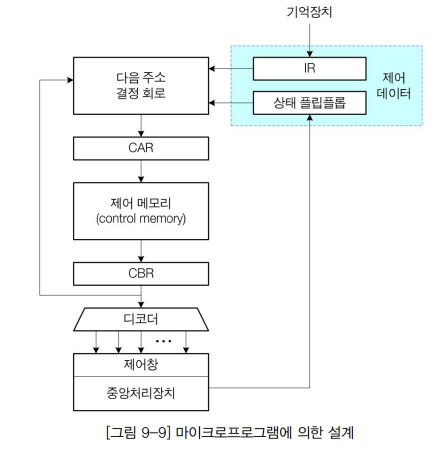

▷ 구조

-

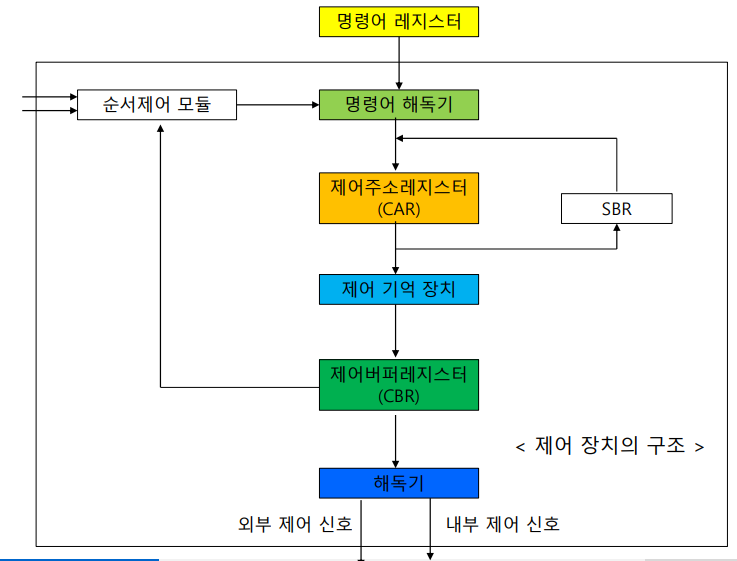

명령어 해독기(Instruction Decoder)

- 명령어 레지스터(IR)로부터 들어오는 명령어의

연산코드를 해석하여 해당 연산을 수행하기 위한

루틴의 시작 주소를 결정

- 명령어 레지스터(IR)로부터 들어오는 명령어의

-

제어 주소 레지스터(CAR, Control Address Register)

- 마이크로 명령어의 주소를 저장하는 레지스터

- 이 주소는 제어 기억장치의 특정 위치를 지칭

- 마이크로 명령어의 주소를 저장하는 레지스터

-

제어 기억장치(Control Memory)

- 마이크로 명령어들로 이루어진 마이크로프로그램을 저장하는 내부 기억장치 (보통 ROM으로 구성)

→ 만약 LOAD 명령이 들어 온다면 LOAD 명령은 루틴이 시작되는 시작번지로 온다. 그 후, CAR을 통해서 제어 기억장치로 간 후 세부적인 연산이 수행되는 것이다!

-

제어 버퍼 레지스터(CBR, Control Buffer Register)

- 마이크로 명령어 비트들을 일시적으로 저장하는 레지스터

-

서브루틴 레지스터(SBR, Subroutine Register)

- 마이크로프로그램에서 서브루틴이 호출되는 경우에 현재의 CAR 내용을 일시적으로 저장하는 레지스터

-

순서 제어 모듈(Sequencing Module)

- 마이크로 명령어의 실행 순서를 결정하는

회로들의 집합 - 순서 제어 모듈의 구성은 설계와 회로에 따라 다르다.

- 마이크로 명령어의 실행 순서를 결정하는

▷ 설계

① 고정 배선 제어 (Hardwired control)

- 특징

- 하드웨어적인 방식으로 구현하는 것

- 회로에 선들을 박아버려 순서적으로 진행!할 수 있도록 한다.

- 순서적으로 진행이 되는데, 시간 조절을 위해 지연 소자나 순차 카운터들로 구현한다.

- 장점

- 속도가 빠르다

- 단점

- 변경이 어렵다.

② 마이크로프로그램 제어

- 특징

- H/W 회로들이 복잡해져서 S/W 방식인 마이크로프로그램을 사용하게 되었다.

- 제어용 타이밍 신호를 제어용 ROM에서 얻는 방식이다.

- IR에 갖고 있는 명령어 값과 상태 플리플롭의 값에 따라서 다음 주소가 결정이 된다.

H/W와 S/W의 장ㆍ단점으로 생각하면 된다!

- 장점

- ROM의 프로그램에 의존하므로 설계가 용이하다.

- 매우 구조적(well structured)이다.

- 마이크로프로그램 제어 방식은 ROM 내의 프로그램에 의하므로 매우 구조적

- 에뮬레이션이 능률적이다.

- 에뮬레이션 : H/W로 구성되어 수행되는 작업을 S/W로 구현한 것

- 융통성이 있다

- 변경이 용이하다.

- 개발비가 적게든다.

- 프로그램 형태이므로 자기진단 기능을 갖출 수 있다.

- 단점

- 속도가 느리다.

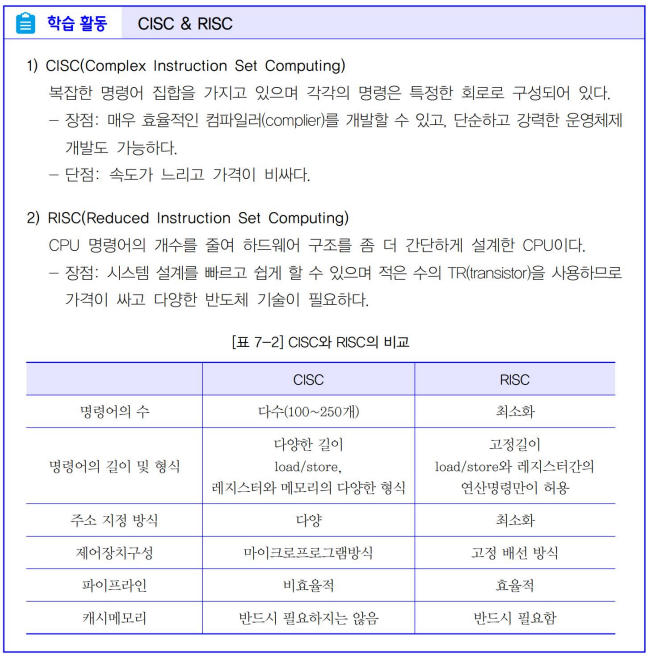

▷ CISC와 RISC⭐⭐

| CISC 방식 | RISC 방식 | |

|---|---|---|

| 개념 | 복잡하고 기능이 많은 명령어로 구성된 컴퓨터이다. | CPU의 명령어 개수를 줄어 H/W 구조를 단순하게 설계한 컴퓨터이다. |

| 제어 장치 구성 | 마이크로 프로그래밍 방식 | 고정 배선 제어 방식 |

| 목적 | 최소의 프로그램 길이로 최대의 동작 → 하나의 명령어당 최대한 많은 작업 | 프로그램 길이는 길어도 실행 시간의 최소화 → 명령어 하나당 하나의 연산 |

| 장점 | 명령어가 S/W적이므로 컴파일 과정이 쉽고, 호환성이 좋다. | 좀 더 빠른 속도로 동작할 수 있다. |

| 단점 | ① 복잡한 명령어로 속도가 느리고 CPU 내부 회로가 복잡하다. ② 가격이 비싸다. | ① 실행하는데 많은 명렁어가 필요하다. ② 저장공간을 많이 차지한다. |

| 명령어 형식 | 가변길이 | 고정길이 |

| 주소지정 방식 | 다양 | 적음 |

| 파이프 라인 | 여러 클럭에 걸쳐 명령어를 수행하기 때문에 비효율적이다. | 1클럭 내외로 명령어를 수행하기 때문에 효율적이다. |

논문을 참고해서 자세히 알아보기!!!!!⭐⭐⭐⭐

RISC와 CISC 혼합 방식에 대해서도 자세히 알아야한다.

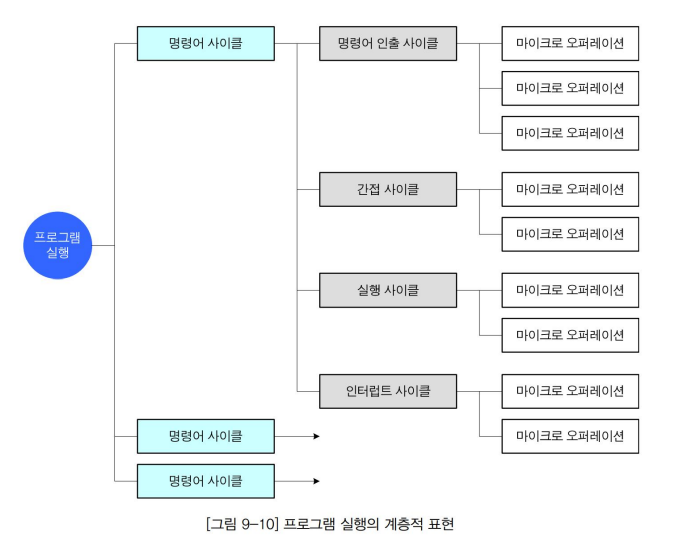

▶ 마이크로 명령어

▷ 종류

- 프로그램 실행의 계층적 표현

데이터 입장에서의 제어장치는 데이터를 각 장치에 이리저리 보내주는 역할이라는 것을 항상 생각하고 있기!!(데이터 흐름 제어)

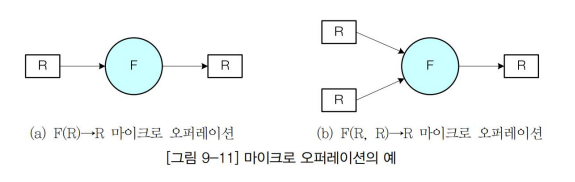

F가 연산장치, R이 레지스터 일 때,

- F(R) → R 마이크로 오퍼레이션

- 첫 번째 레지스터에 있는 값을 연산 장치로 두 번째 레지스터로 이동하는 오퍼레이션을 진행한다.

- F(R, R) → R 마이크로 오퍼레이션

두 개의 레지스터에서 한 개의 레지스터로 이동할 수 있다.

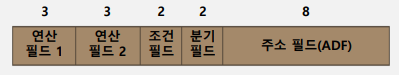

▷ 형식

-

각 필드의 비트수는 늘어날수도, 줄어들수도 있다.

-

조건 필드와 분기 필드를 같이 봐야한다.

-

조건 필드

- 두 비트로 구성되며, 분기의 조건으로 사용

-

분기 필드

- 두 비트로 구성되며, 분기 동작을 지정

▷ 제어 신호 발생 방법

마이크로 명령어 내 연산 필드의 비트들로 제어 신호를 발생한다.

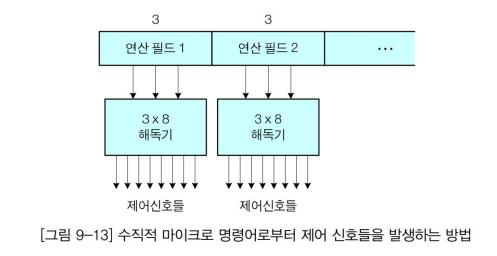

① 수직적 마이크로프로그래밍

- 특징

- 마이크로 명령어의 연산 필드에 적은 수의 코드화된

비트들을 포함시키고, 해독기를 이용하여 그 비트들을 필요한 수만큼의 제어 신호들로 확장하는 방식

- 마이크로 명령어의 연산 필드에 적은 수의 코드화된

- 예시

- 3개 비트를 받아 8개로 확장

- 3개 비트를 받아 8개로 확장

- 장점

- 마이크로 명령어의 길이(비트 수) 최소화 (해독기들로 확장할 수 있기 때문에 적은 비트수로 표현 가능) → 제어 기억장치 용량 감소

- 마이크로 명령어의 길이(비트 수) 최소화 (해독기들로 확장할 수 있기 때문에 적은 비트수로 표현 가능) → 제어 기억장치 용량 감소

- 단점

- 해독 동작에 걸리는 만큼의 지연 시간 발생

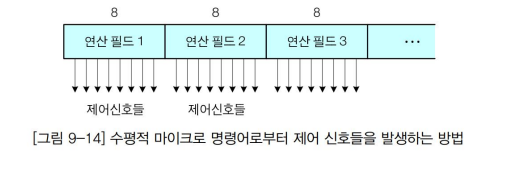

② 수평적 마이크로프로그래밍

- 특징

- 연산 필드의 각 비트와 제어 신호를 1:1로 대응시키는 방식

- 필요한 제어 신호 수만큼의 비트들로 이루어진 연산 필드 비트들이 마이크로 명령어에 포함되어야 한다.

- 연산 필드에서 받는 필드 그대로 제어 신호 발생!

- 예시

- 8비트의 연산 비트를 가지고 있을 때, 그대로8개의 제어 신호가 발생한다.

- 8비트의 연산 비트를 가지고 있을 때, 그대로8개의 제어 신호가 발생한다.

- 장점

- 하드웨어가 간단하고, 해독에 따른 지연 시간이 없음

- 단점

- 마이크로 명령어의 비트 수가 길어지기 때문에 제어

기억장치의 용량이 증가

- 마이크로 명령어의 비트 수가 길어지기 때문에 제어

📎참조

- 『 성결대학교 김자원 교수님 』 - 컴퓨터 구조 (2023)

- 『 컴퓨터구조(제5판) 』 - 복두 출판사

- https://m.blog.naver.com/webserver3315/221389714502