Verilog 복습 4일차

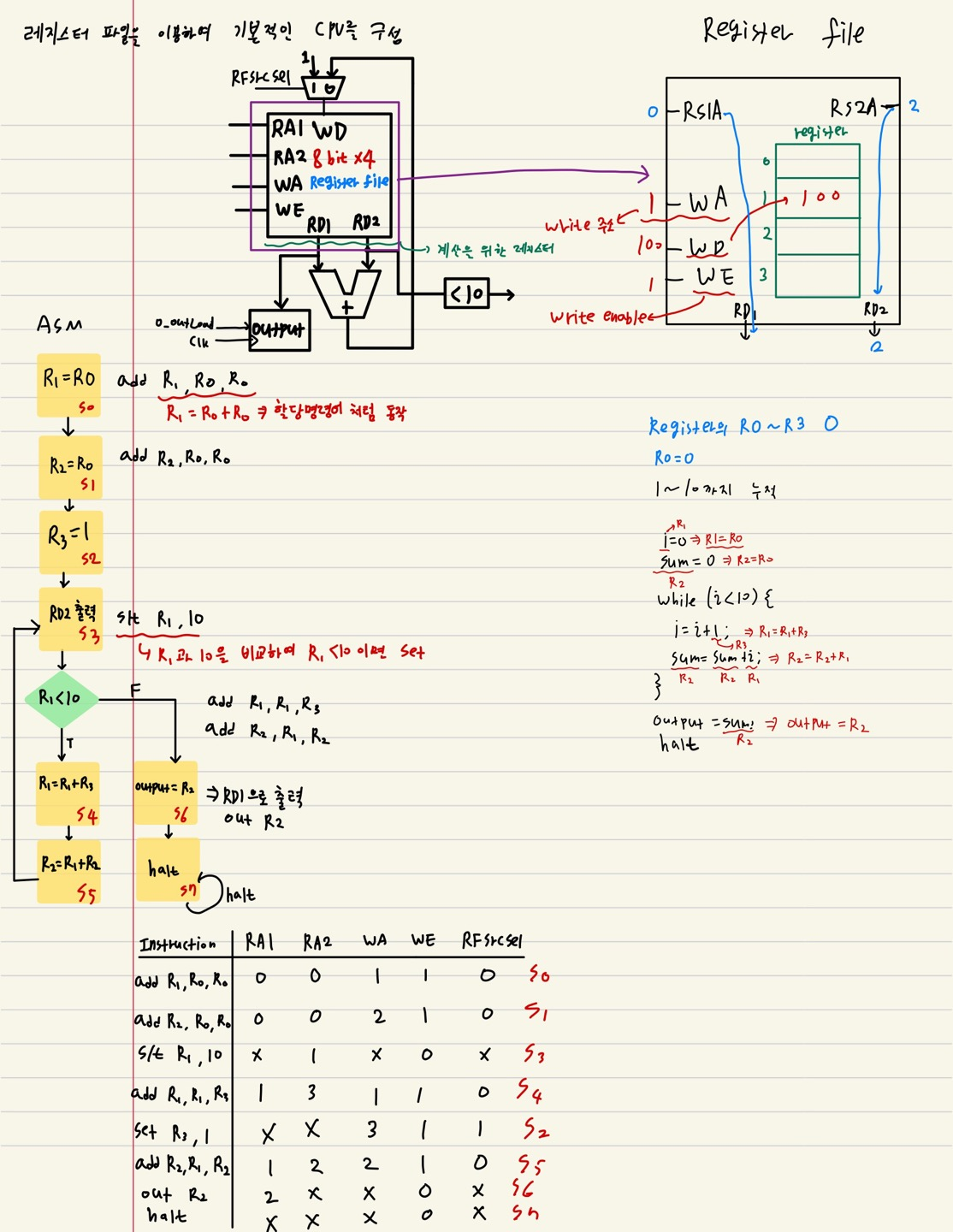

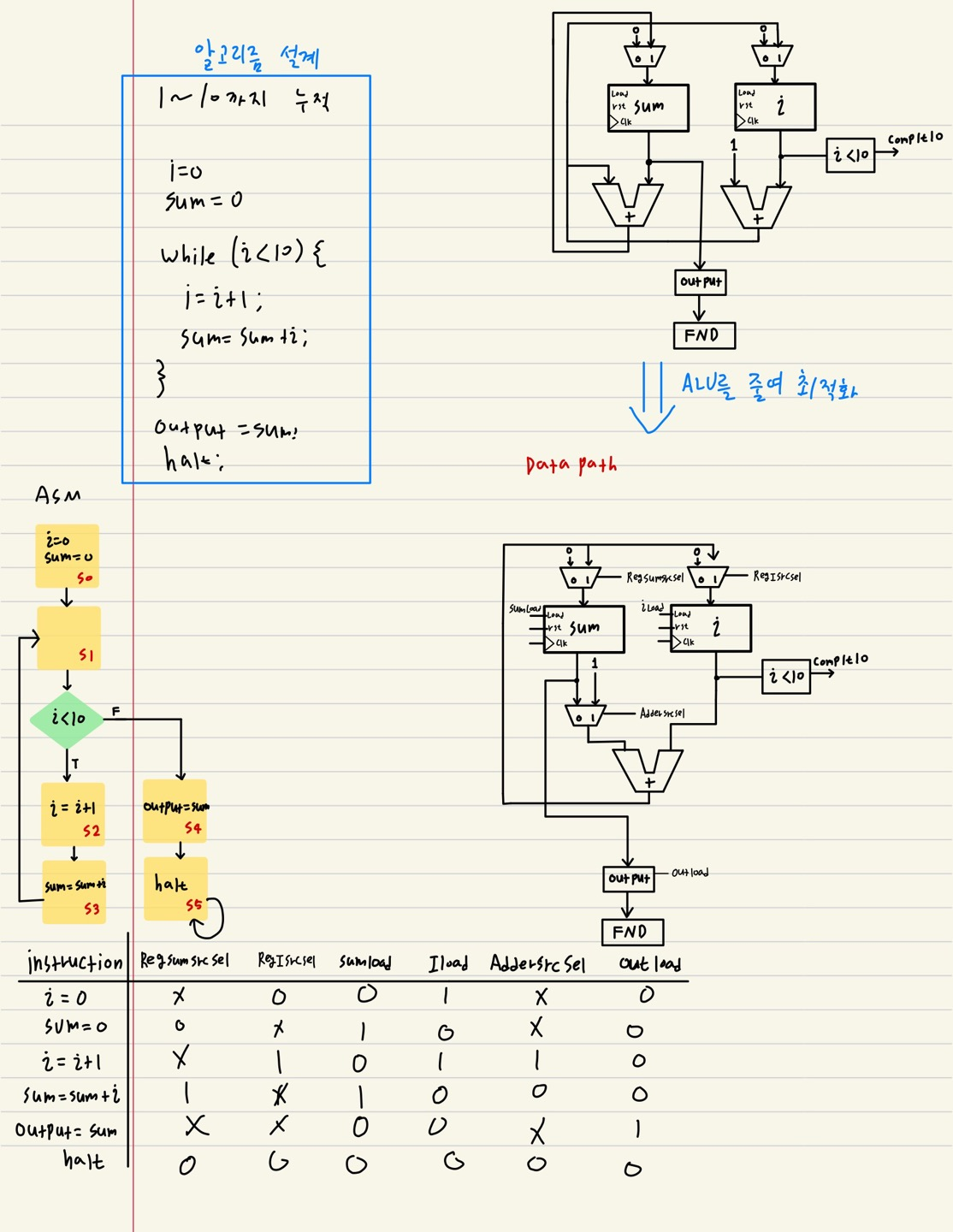

오늘의 목표는 어제 구현한 간단한 CPU구조에 1~10 까지 더한 값이 출력되도록 하는 것이다.

Count에는 1개의 레지스터가 사용됐지만, 이번에는 2개의 레지스터를 사용해볼 것이다.

위처럼 회로도를 설계하였다.

설계 스텝은 다음과 같다.

- 알고리즘을 간단하게 코드화

- 코드를 바탕으로 schematic 설계

- schematic을 바탕으로 ASM차트와 Signal Table을 설계한다.

- 이를 바탕으로 코딩을 진행한다.

#Control_unit# module controlUnit( input clk, input reset, input i_iLt10, output reg o_regSumSrcSel, output reg o_regISrcSel, output reg o_sumLoad, output reg o_iLoad, output reg o_adderSrcSel, output reg o_outLoad ); parameter S0 =0, S1 =1, S2 =2, S3 =3, S4 =4, S5 =5; reg[2:0] curState = S0, nextState; always @(posedge clk, posedge reset) begin if (reset) curState <=S0; else curState <= nextState; end // next state logic always@(*) begin case (curState) S0:nextState =S1; S1: begin if(i_iLt10) nextState = S2; else nextState = S4; end S2: nextState = S3; S3: nextState = S1; S4: nextState = S5; S5: nextState = S5; default: nextState = S0; endcase end always@(curState) begin //output logic circuit case(curState) S0: begin o_regSumSrcSel = 1'b0; o_regISrcSel = 1'b0; o_sumLoad = 1'b1; o_iLoad = 1'b1; o_adderSrcSel = 1'bx; o_outLoad = 1'b0; end S1: begin o_regSumSrcSel = 1'bx; o_regISrcSel = 1'bx; o_sumLoad = 1'b0; o_iLoad = 1'b0; o_adderSrcSel = 1'bx; o_outLoad = 1'b0; end S2: begin o_regSumSrcSel = 1'bx; o_regISrcSel = 1'b1; o_sumLoad = 1'b0; o_iLoad = 1'b1; o_adderSrcSel = 1'b1; o_outLoad = 1'b0;; end S3: begin o_regSumSrcSel = 1'b1; o_regISrcSel = 1'bx; o_sumLoad = 1'b1; o_iLoad = 1'b0; o_adderSrcSel = 1'b0; o_outLoad = 1'b0; end S4: begin o_regSumSrcSel = 1'bx; o_regISrcSel = 1'bx; o_sumLoad = 1'b0; o_iLoad = 1'b0; o_adderSrcSel = 1'bx; o_outLoad = 1'b1; end S5: begin o_regSumSrcSel = 1'bx; o_regISrcSel = 1'bx; o_sumLoad = 1'b0; o_iLoad = 1'b0; o_adderSrcSel = 1'bx; o_outLoad = 1'b0; end default: begin o_regSumSrcSel = 1'bx; o_regISrcSel = 1'bx; o_sumLoad = 1'b0; o_iLoad = 1'b0; o_adderSrcSel = 1'bx; o_outLoad = 1'b0; end endcase end endmodule

#Data_path_unit# module dataPath( input clk, input reset, input i_regSumSrcSel, input i_regISrcSel, input i_sumLoad, input i_iLoad, input i_adderSrcSel, input i_outLoad, output o_iLt10, output [7:0] o_output ); wire [7:0]w_addResult, w_sumSrcData; wire [7:0] w_sumOutData, w_addSrcData; wire [7:0] w_iSrcData, w_iOutData; ///////////////////////////////////////////////////////////////////////////////////// Sum mux_2x1 u_sumSrcMux( .i_a(8'b0), .i_b(w_addResult), .i_sel(i_regSumSrcSel), .o_y(w_sumSrcData) ); register u_sumReg( .clk(clk), .reset(reset), .i_load(i_sumLoad), .i_data(w_sumSrcData), .o_data(w_sumOutData) ); mux_2x1 u_adderSrcMux( .i_a(w_sumOutData), .i_b(8'd1), .i_sel(i_adderSrcSel), .o_y(w_addSrcData) ); /////////////////////////////////////////////////////////////////////////////// I mux_2x1 u_iSrcMux( .i_a(8'b0), .i_b(w_addResult), .i_sel(i_regISrcSel), .o_y(w_iSrcData) ); register u_iReg( .clk(clk), .reset(reset), .i_load(i_iLoad), .i_data(w_iSrcData), .o_data(w_iOutData) ); comperator CompLt10( .i_a(w_iOutData), .i_b(8'd10), .o_lt(o_iLt10) ); /////////////////////////////////////////////////////////////////////////////// Adder adder Adder( .i_a(w_addSrcData), .i_b(w_iOutData), .o_sum(w_addResult) ); register regOutput( .clk(clk), .reset(reset), .i_load(i_outLoad), .i_data(w_sumOutData), .o_data(o_output) ); endmodule module mux_2x1( input [7:0] i_a, input [7:0] i_b, input i_sel, output reg [7:0] o_y ); always @ (*) begin case (i_sel) 1'b0: o_y = i_a; 1'b1: o_y = i_b; endcase end endmodule module register( input clk, input reset, input i_load, input [7:0] i_data, output [7:0] o_data ); reg[7:0] q = 0; assign o_data=q; always @ (posedge clk, posedge reset) begin if(reset) begin q <= 0; end else begin if (i_load) q <= i_data; else q <= q; end end endmodule module comperator( input [7:0] i_a, input [7:0] i_b, output o_lt ); assign o_lt= (i_a < i_b) ? 1'b1: 1'b0; endmodule module adder( input [7:0] i_a, input [7:0] i_b, output [7:0] o_sum ); assign o_sum=i_a+i_b; endmodule

#Top_Module# module DedicatedProcessor( input clk, reset, output [7:0] o_output ); wire w_iLt10, w_regSumSrcSel, w_regISrcSel, w_sumLoad, w_iLoad, w_adderSrcSel, w_outLoad; controlUnit u_CU( .clk(clk), .reset(reset), .i_iLt10(w_iLt10), .o_regSumSrcSel(w_regSumSrcSel), .o_regISrcSel(w_regISrcSel), .o_sumLoad(w_sumLoad), .o_iLoad(w_iLoad), .o_adderSrcSel(w_adderSrcSel), .o_outLoad(w_outLoad) ); dataPath u_DP( .clk(clk), .reset(reset), .i_regSumSrcSel(w_regSumSrcSel), .i_regISrcSel(w_regISrcSel), .i_sumLoad(w_sumLoad), .i_iLoad(w_iLoad), .i_adderSrcSel(w_adderSrcSel), .i_outLoad(w_outLoad), .o_iLt10(w_iLt10), .o_output(o_output) ); endmodule

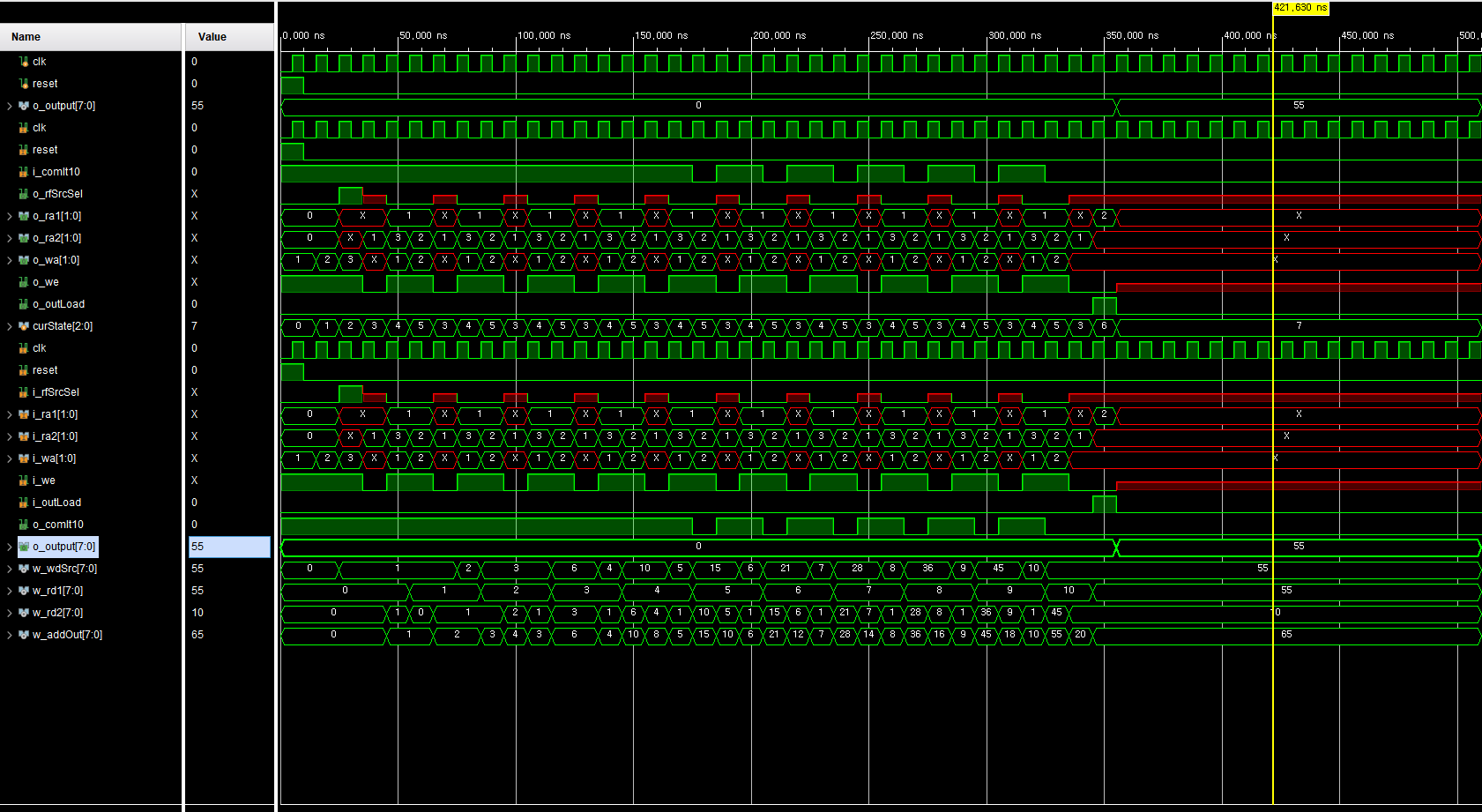

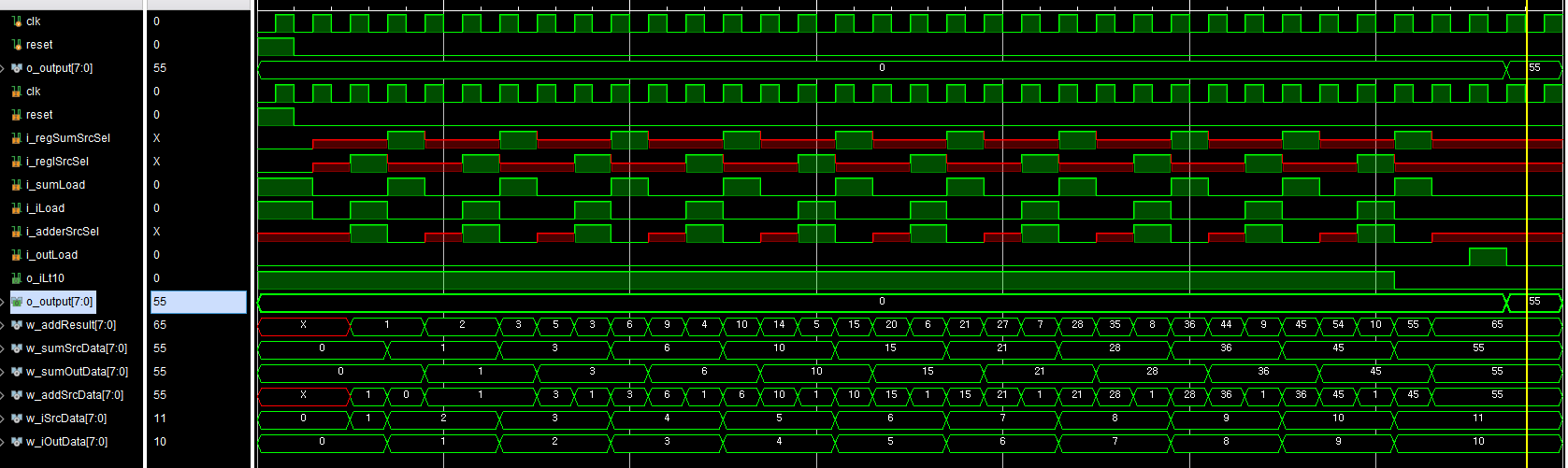

시뮬레이션

- 55가 출력되어 정상적으로 1~ 10까지 덧셈이 이루어졌음을 볼 수 있다.