Verilog 복습 5일차

RISC-V

- RISC-V의 경우, ARM 아키텍처와 다르게 오픈소스화되어 있음.

- 이 때문에 라이센스 비용이 없기에 ARM의 대항마로 각광받고 있음

- 아직은 ARM이 대세지만 리눅스가 유닉스를 밀어냈듯 RISC-V의 전망이 밝음

- 미중 반도체 패권 다툼에서 중국이 미국의 ARM 아키텍처를 사용하기 어렵게되자 RISC-V를 밀어주고 있음

이러한 RISC-V를 이용하여single cycle CPU를 설계할 것이다.

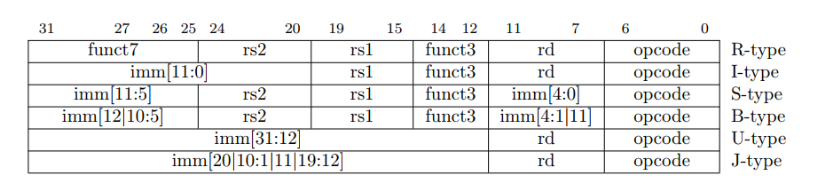

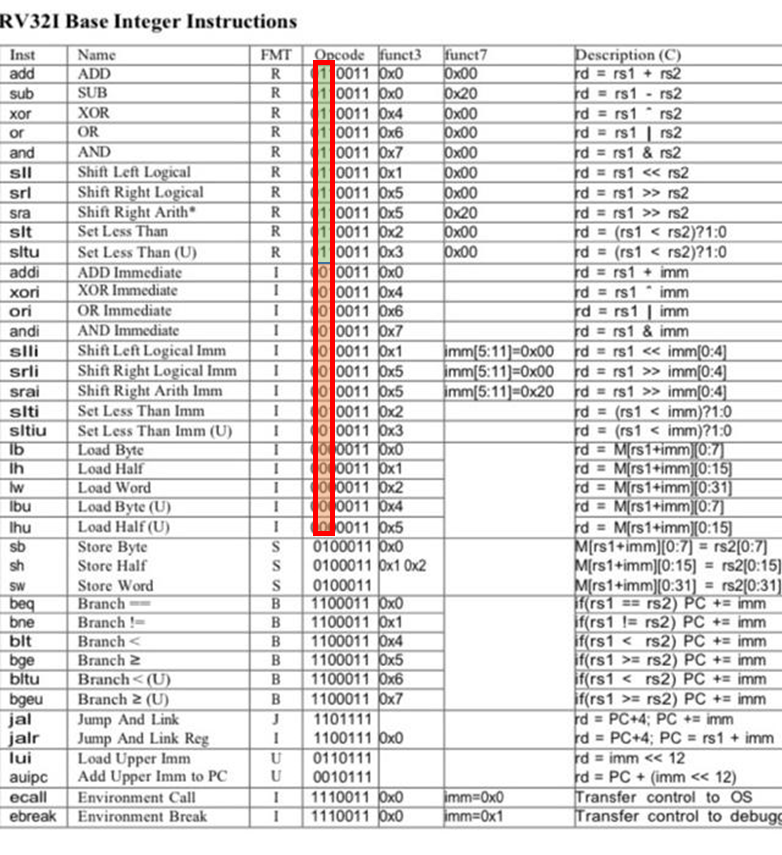

위의 instruction set이 ROM에 들어가는 Instruction 코드이며, 이 동작들을 구현하기 위해 코딩을 진행하였다.

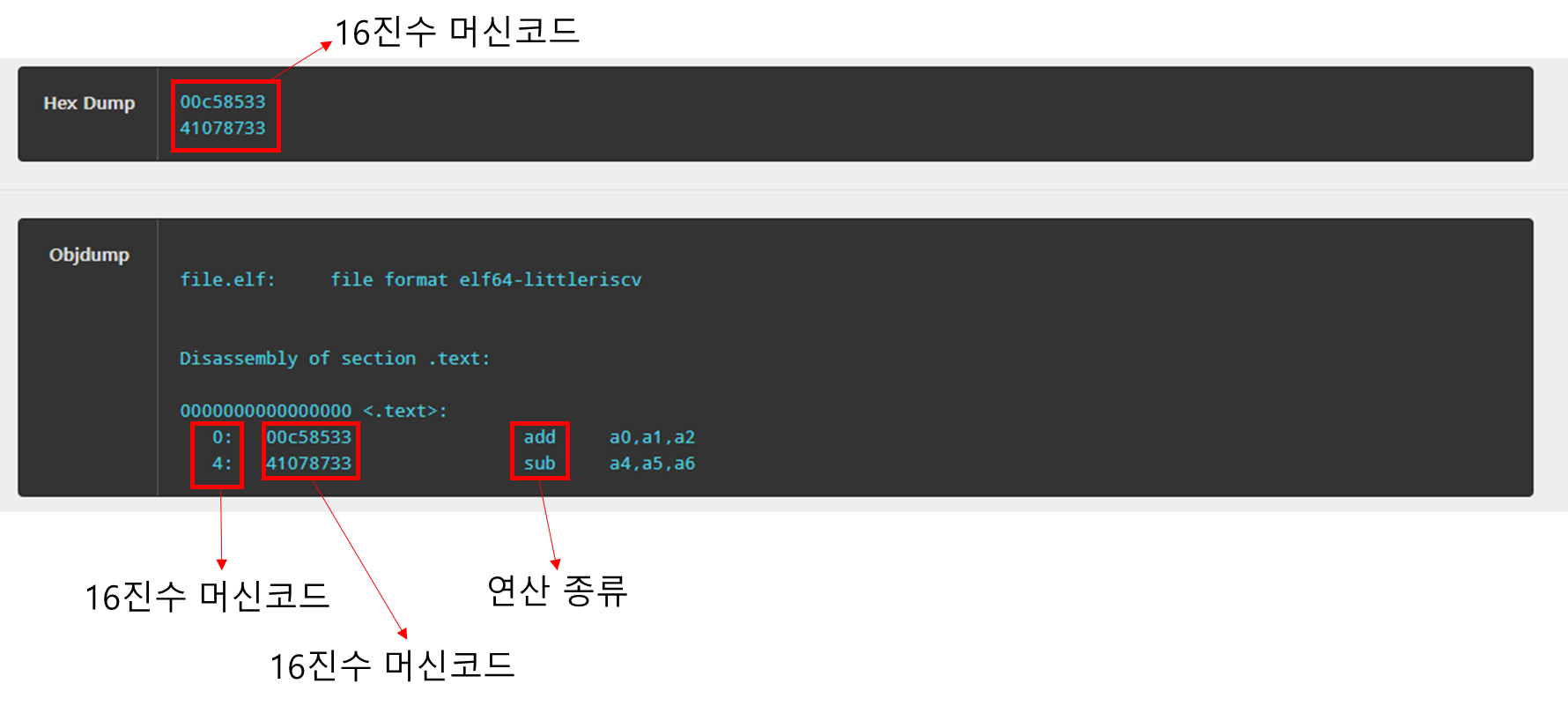

https://riscvasm.lucasteske.dev/

위의 링크는 RISC-V의 instruction set을 16진수 형태로 바꿔주는 사이트이다.

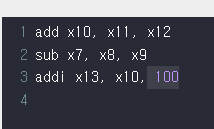

예를 들어 add x10, x11, x12의 연산을 위한 코드를 16진수로 하면 다음과 같다.

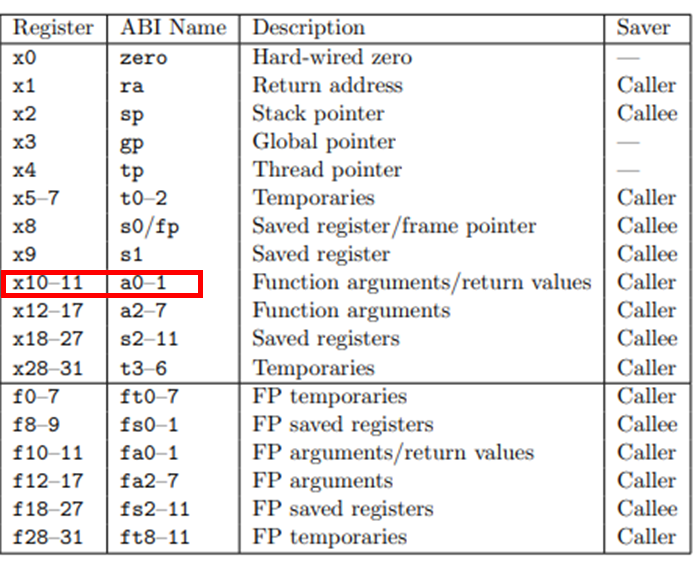

위는 RISC-V의 RVG Calling Convention, 레지스터의 추천 용도이다.

왜 I type은 sub가 없을까 하는 의문이 들었다.

조사를 해보니 i type의 imm이 signed이기에 뺄셈도 가능하다.

word는 register을 크기(내가 설계한 CPU에서는 4byte)

https://godbolt.org/

C언어를 RISC_V의 assembly 언어로 변환해줌

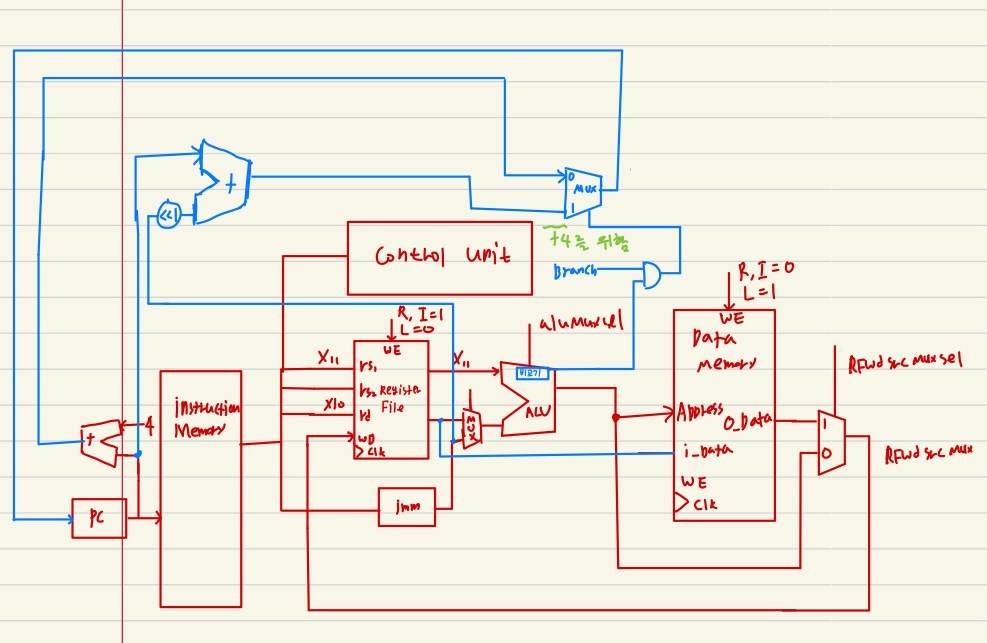

위의 회로도를 기반으로 single cycle CPU를 설계하였다.

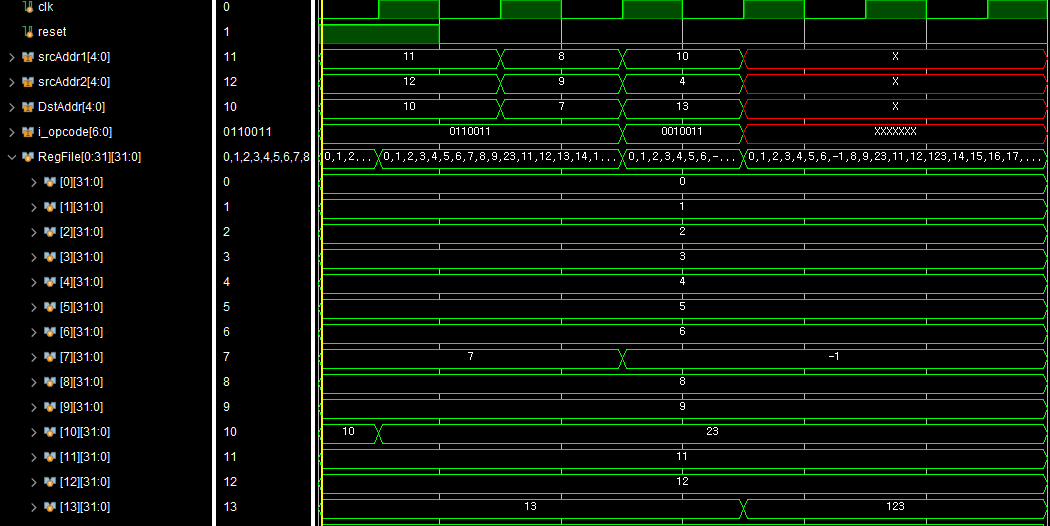

32bit의 RISC V를 사용하였으며, Instruction set을 저장하기 위한 ROM은 32bit 레지스터를 1024개, Data를 저장하기 위한 메모리는 32bit 레지스터를 2048개를 사용하였다.

위의 회로를 구성함에 있어서 문제가 있었다. 처음 시작은 I-type 구현에서 시작하였다.

I Type과 R Type의 경우, opcode[5]가 다름을 볼 수 있었다.

이 opcode를 ALU의 결과값과 즉시값을 선택하는 MUX의 Select신호로 이용하려고 하였다.

그러나 S Type의 경우, 즉시 값을 MUX에서 선택해야하는데, opcode[5]가 R Type과 같은 1이었기 때문에 코드를 수정했어야 했다.

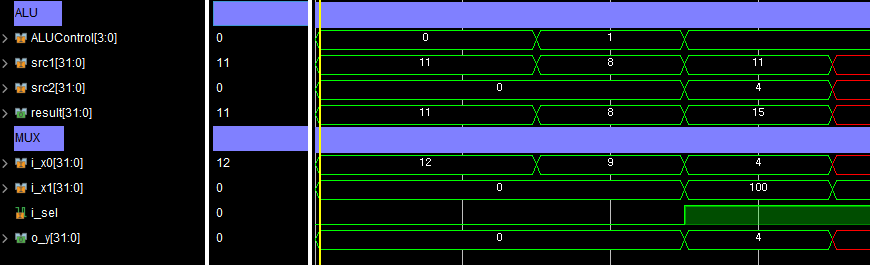

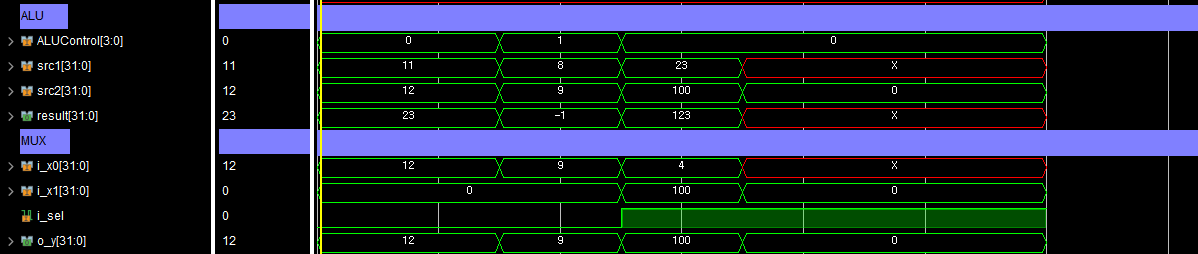

그러나, MUX Module의 0 출력값과 1출력값을 수정하지 않아, register에 엉뚱한 값이 입력됨을 볼 수 있었다.

값이 저장되는 레지스터의 주소는 지정해준 주소값과 같음을 볼 수 있었기 때문에 데이터 값을 주는 곳에서 문제가 있음을 유추할 수 있었다. 레지스터로 값이 들어오는 경로를 하나씩 되 짚어보며 파형을 확인하였고, ALU의 입출력을 확인해 보았을 때, 두번쨰 입력이 지정해준 값이 아닌 엉뚱한 값이 입력됨을 볼 수 있었다.

Mux에서 출력되는 값이 잘못되어 있다 판단하여 Mux에서 출력되는 값을 확인하여 0번과 1번을 반대로 입력함을 알 수 있었다.

오류

수정 후

정리가 잘 된 글이네요. 도움이 됐습니다.