Verilog 복습 7일차

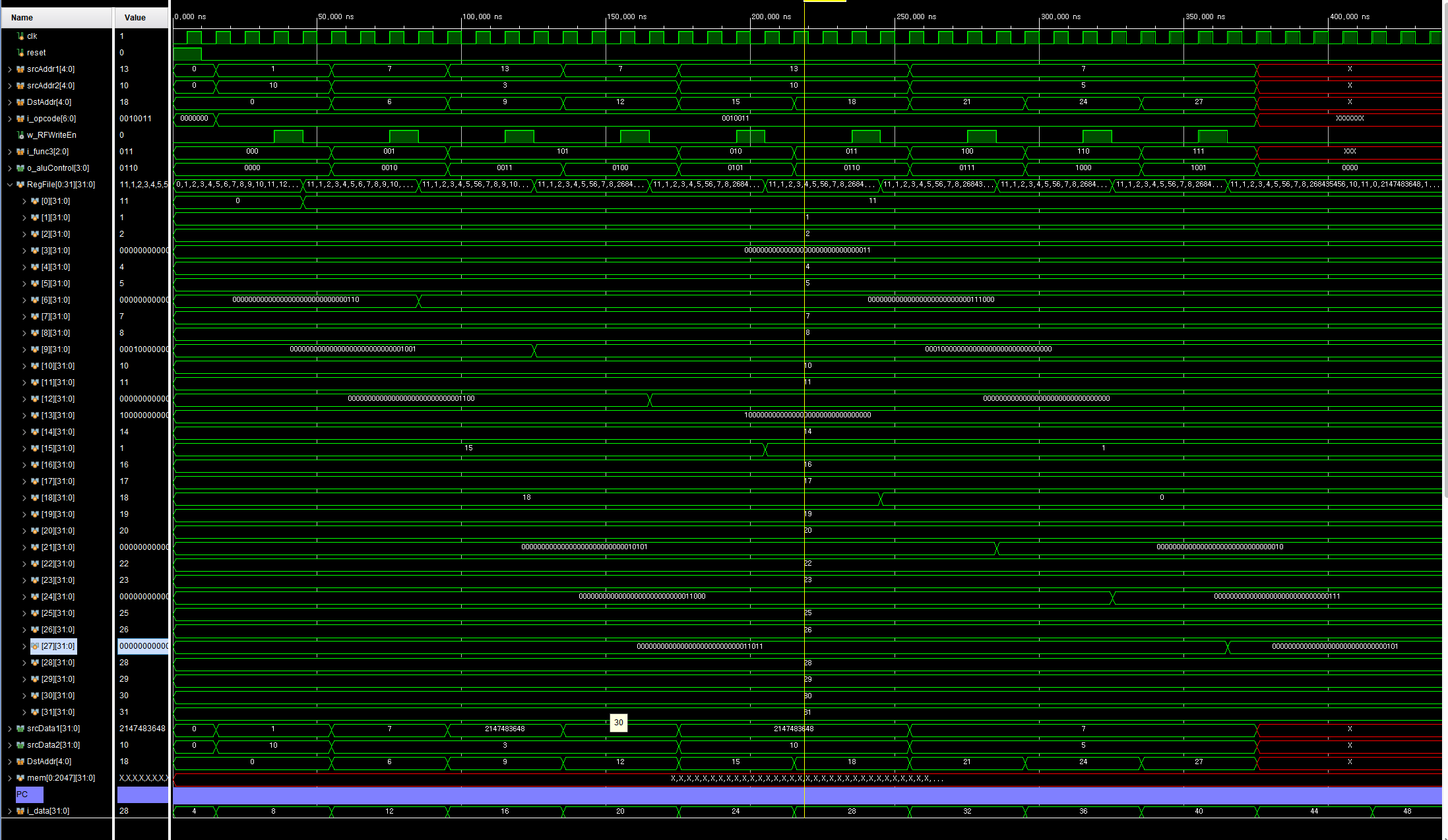

- Brench 시에 input PC값이 Brench 주소값으로 바뀌었다가 다시 원상복구되는 현상이 발생

-> PC 값의 출력을 결정하는 레지스터 i_load가 PC +4와 Branch 값중 하나를 결정해주는 MUX의 출력값이 Branch 시에 1이 되지 않아, Branch한 출력값이 나오지 않았음

iload와 i_branch를 and처리하여 문제를 수정

- Branch 주소가 목표주소보다 +4되어 Branch되는 현상이 발생 이 때문에 Branch 명령어 다음의 동작이 작동하지 않음

-> Brnach 주소값을 결정하는 ALU 결과값에 -4를 해주어 의도한 Branch대로 동작하도록 함.

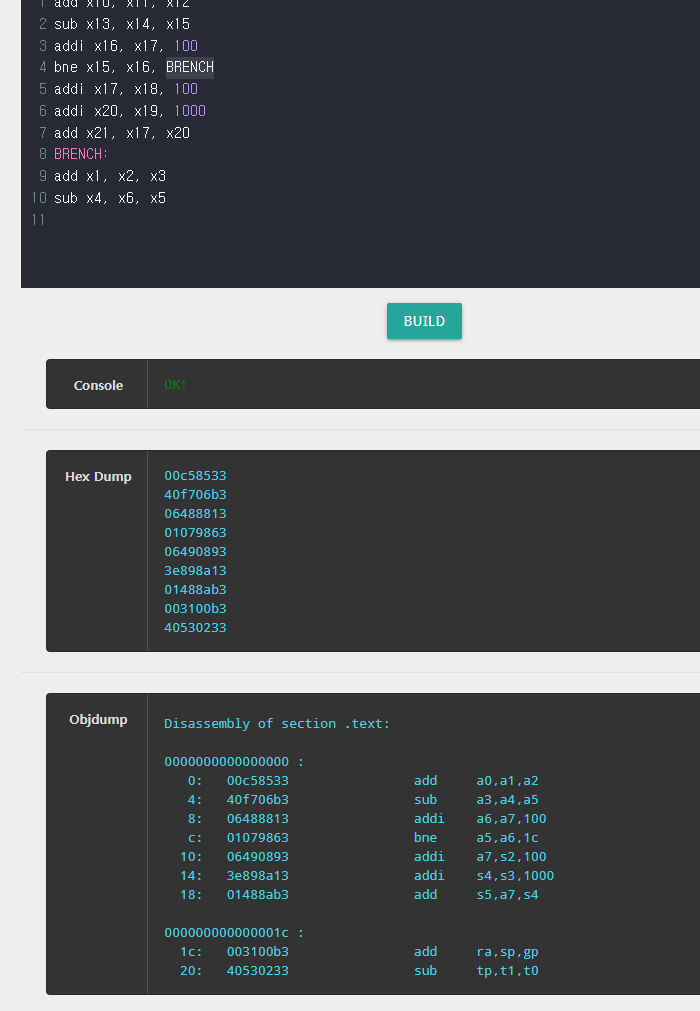

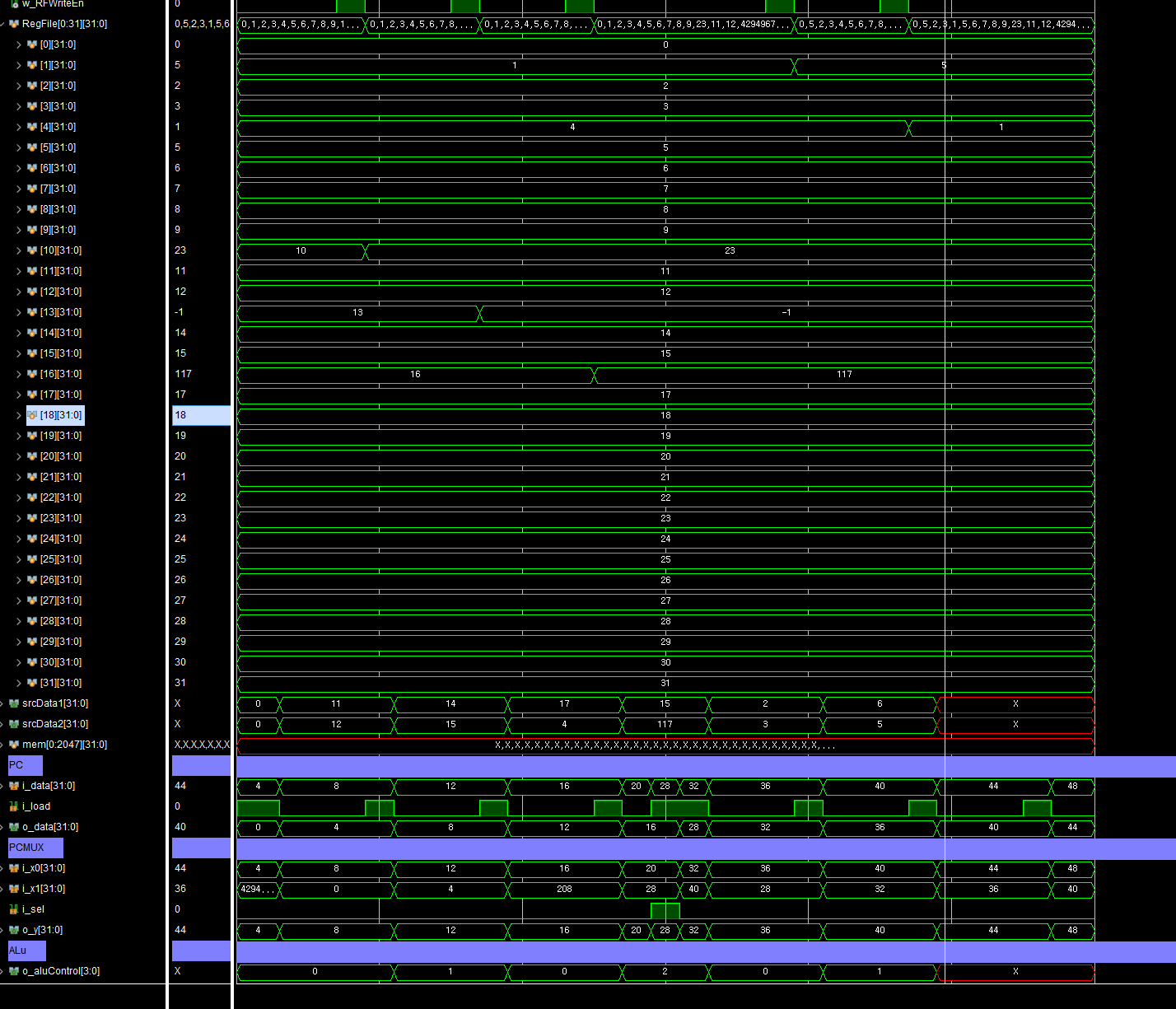

R type 완성

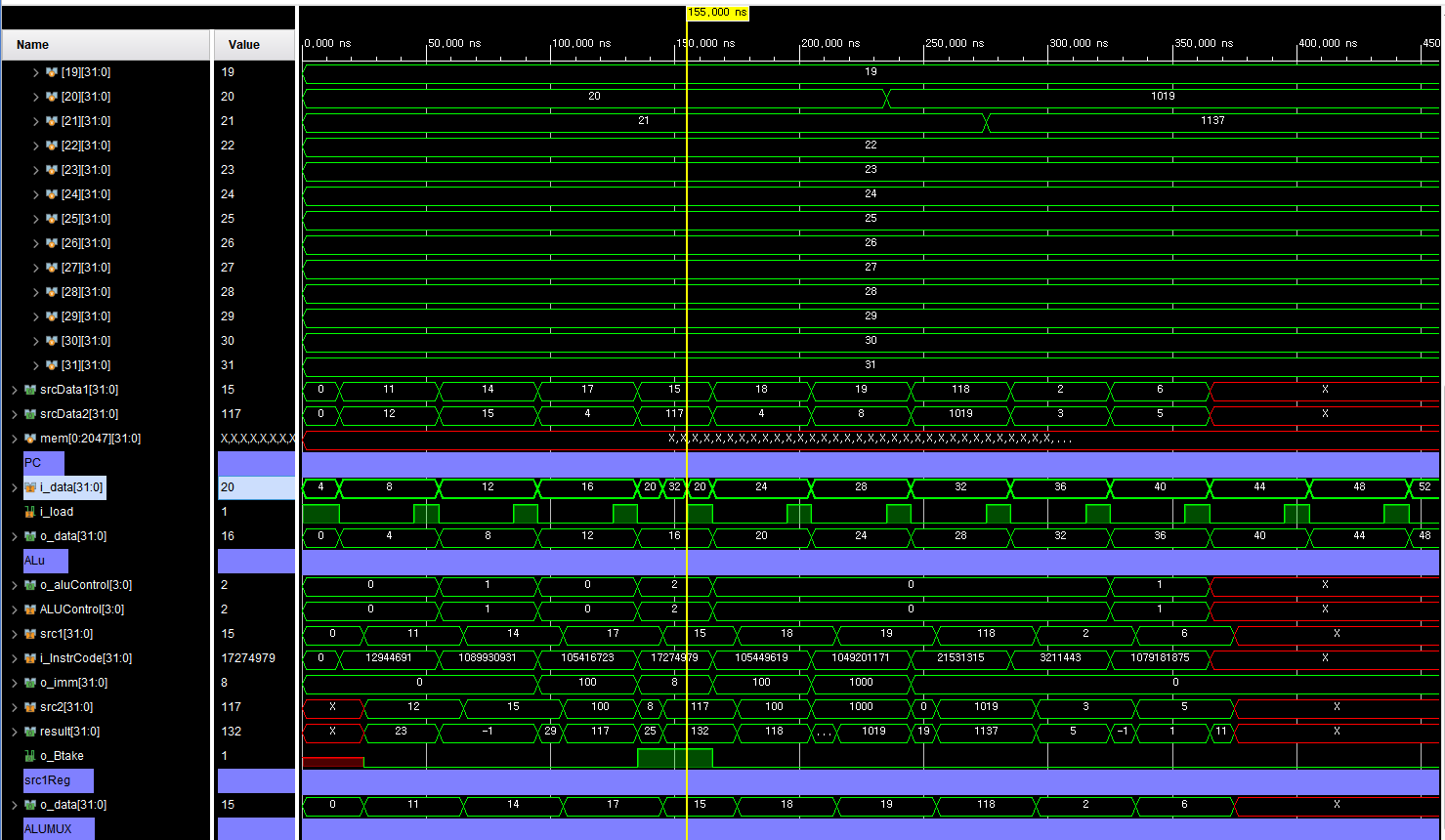

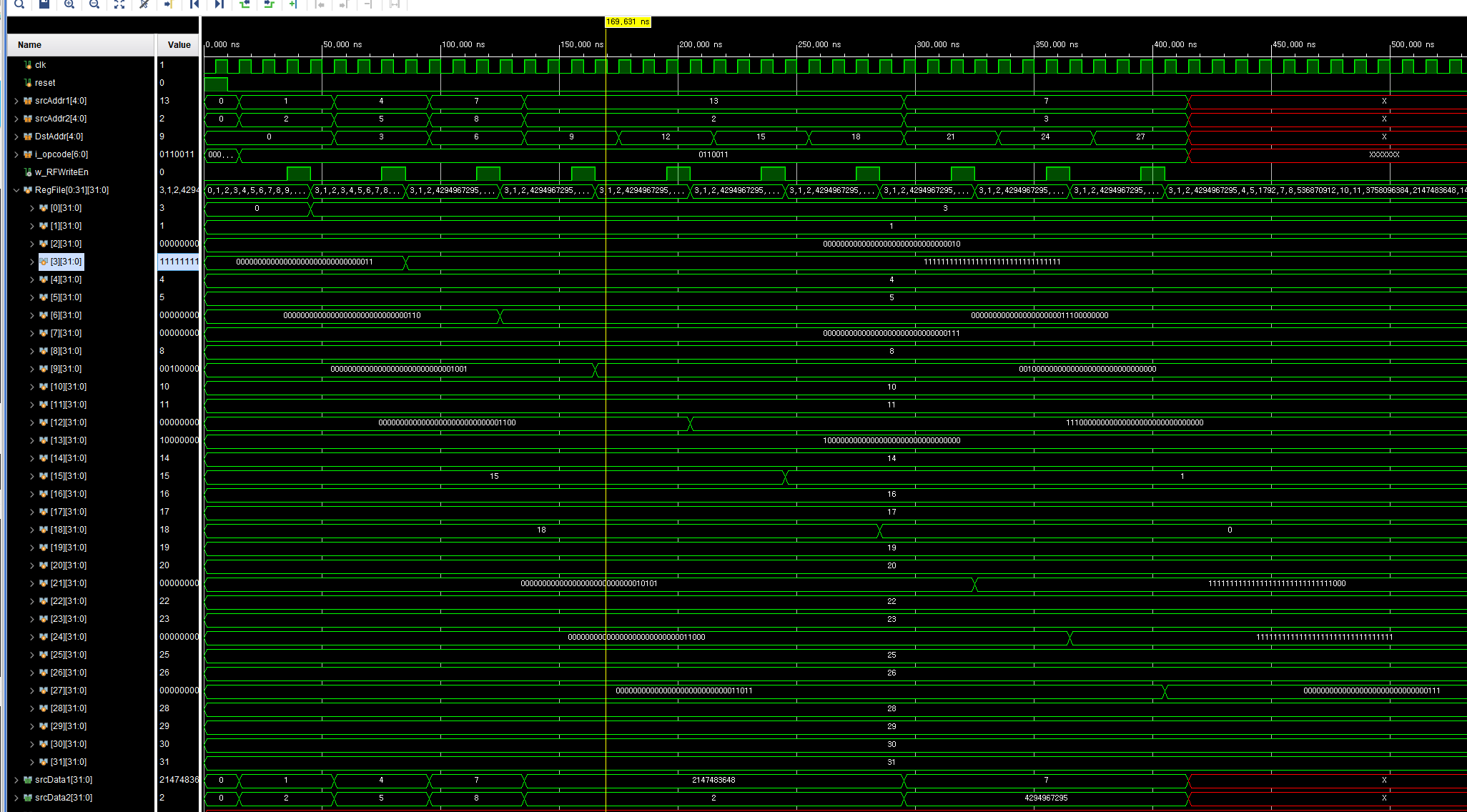

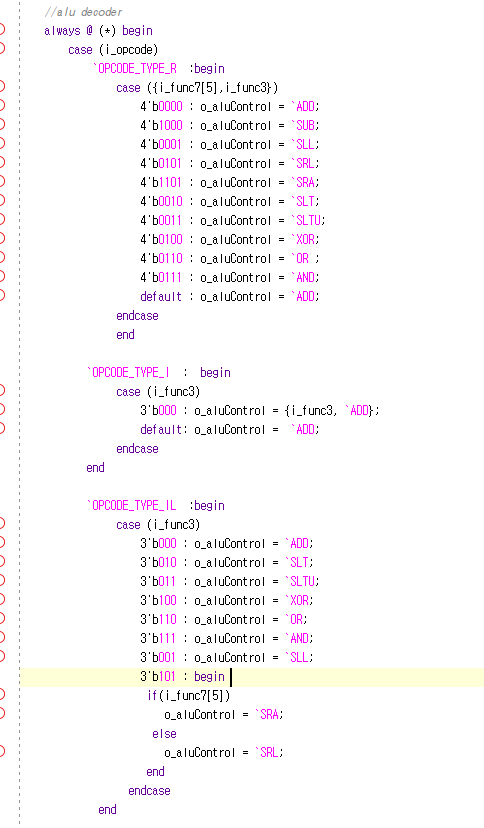

IL type 동작이 정상적으로 이루어지지않음

IMM과 덧셈 동작만 수행된다.

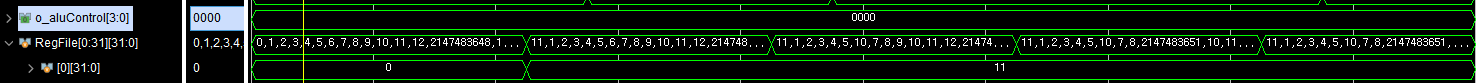

ALU_Control의 값이 계속 0임에 주목을 했다.

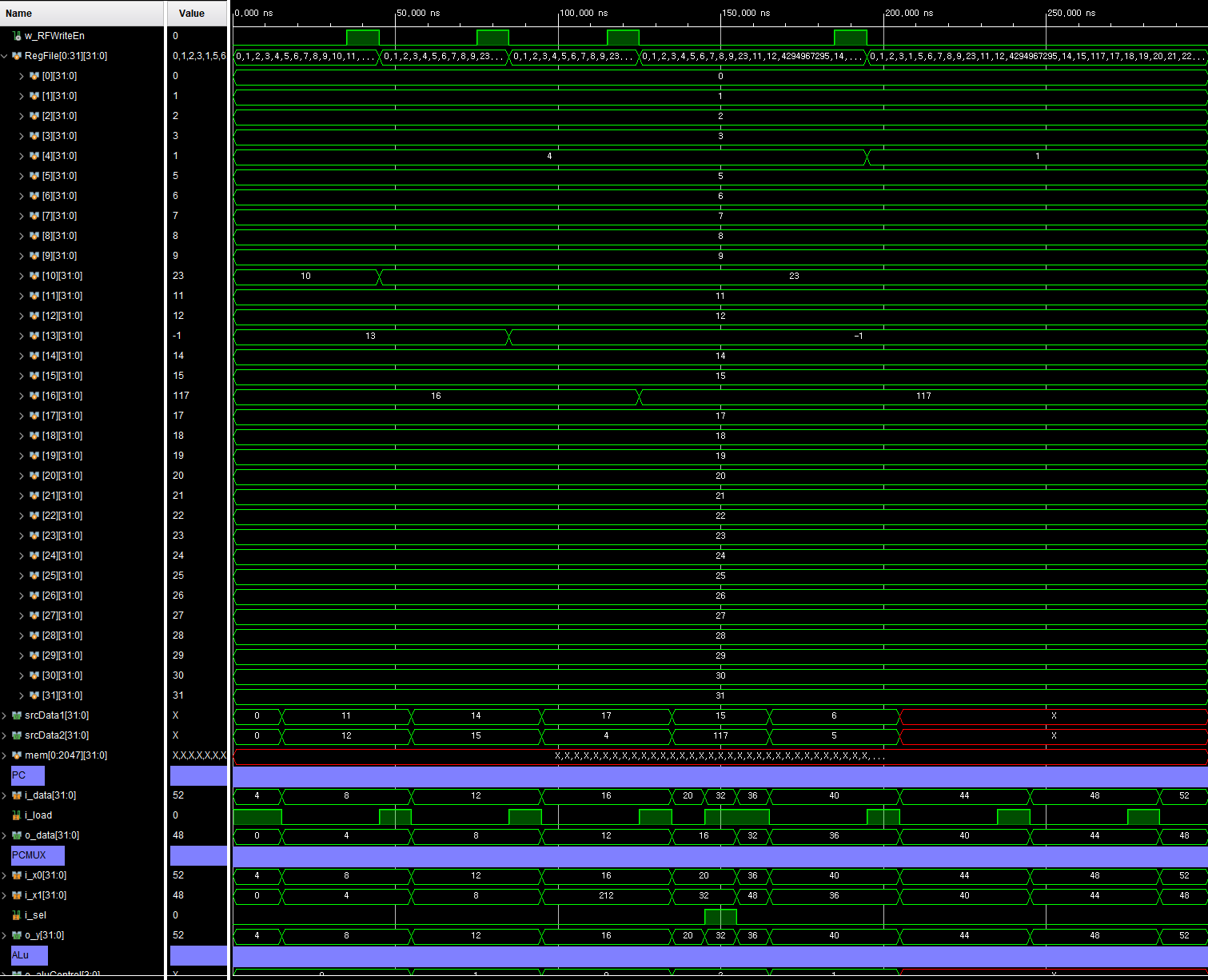

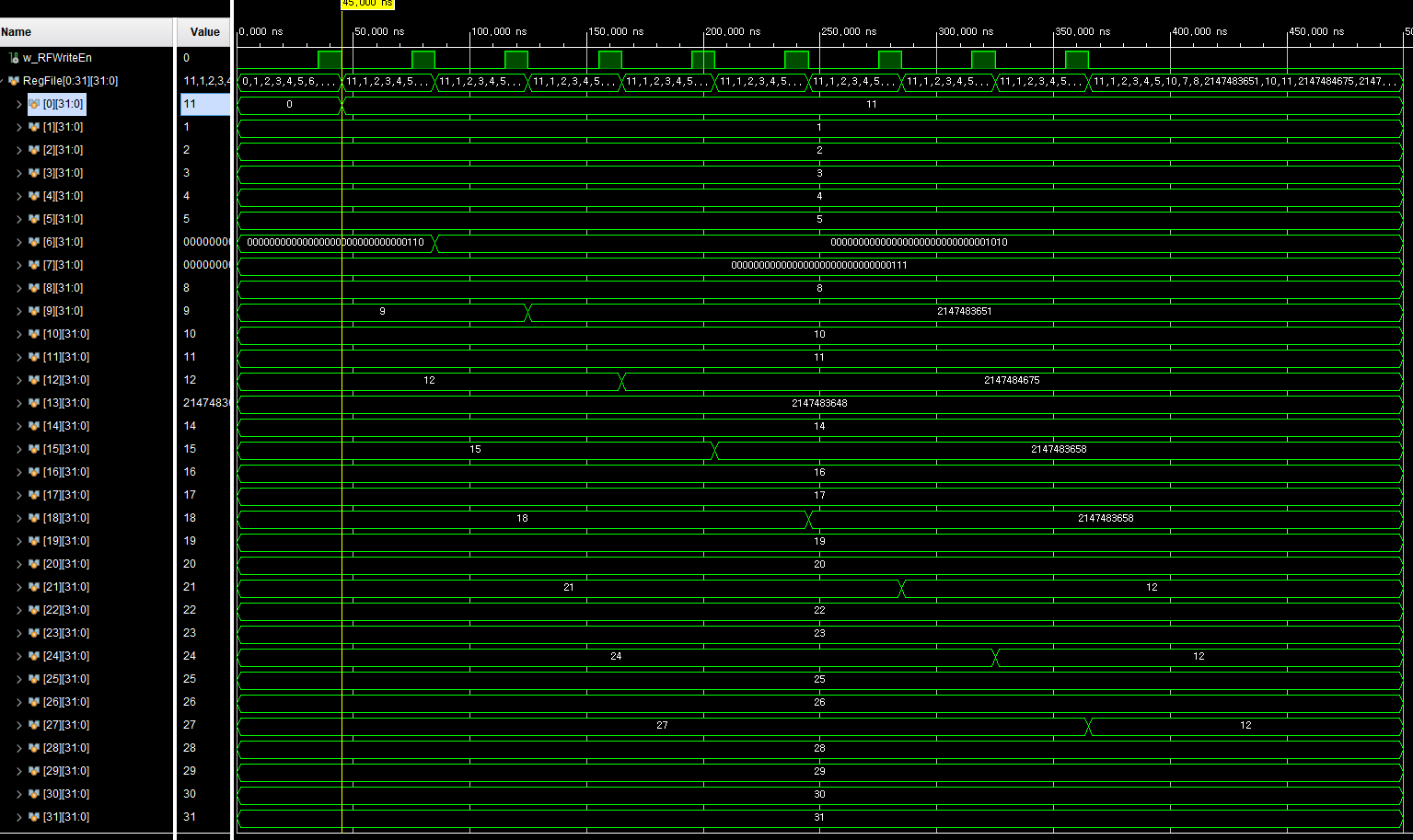

아쁄싸 IL과 I타입의 case를 반대로 적었다.

그러니 ADD동작 밖에 수행됐던 것이다.

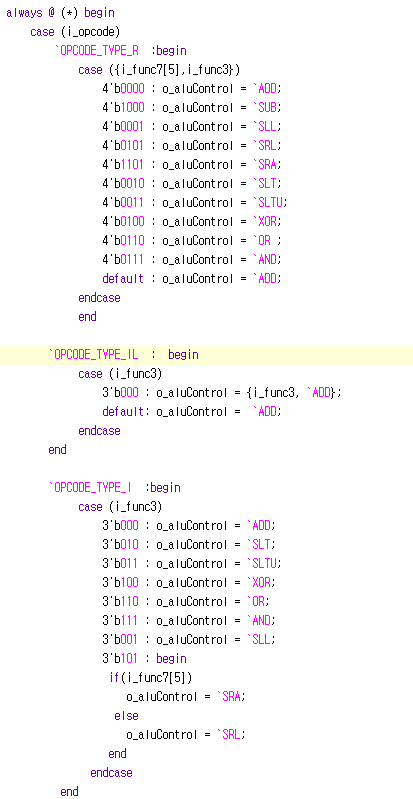

수정 후