Verilog 복습 6일차

Multi Cycle 형태의 CPU를 개발할 것이다.

내가 구현해야 할 것

-

instruction set

R type (Add, Sub제외)

I type (Addi 제외)

IL type (LB제외)

S type(SW제외)

B type(BEQ, BNE제외)

U type

J type

I type -

J type을 위한 PC Jump path

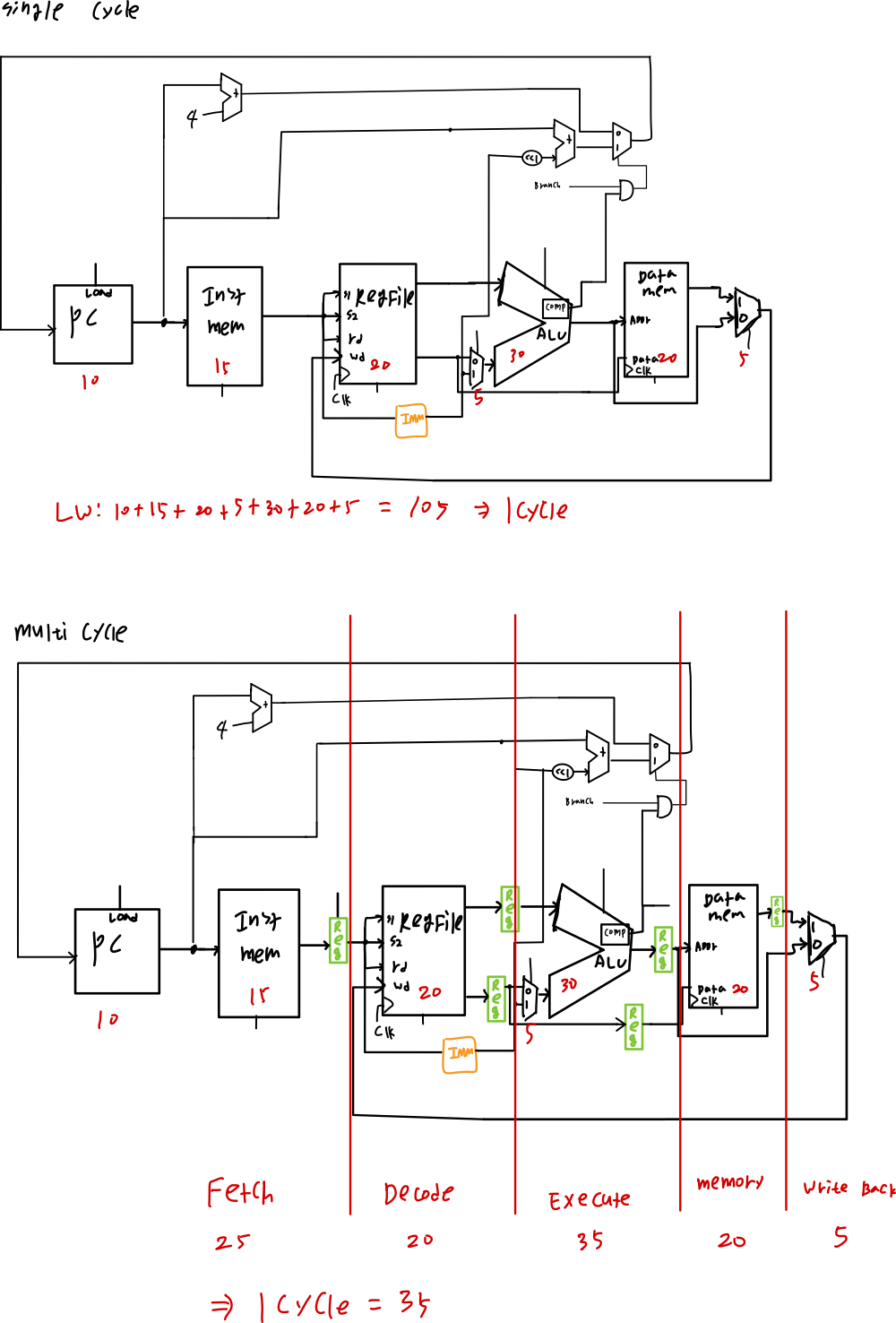

Clock 주기의 경우, 가장 느린 instruction을 기준으로 정한다.

때문에 Single cycle 구조에서는 가장 긴 cycle의 명령어의 속도를 따라야함으로 동작속도가 느리다.

Multi Cycle의 경우, Register를 통해 한 클럭당 하나의 동작을 수행하기 때문에 동작의 속도가 빨라진다는 장점이 있다.

-> single cycle의 경우, clock이 105s가 되겠지만 Multi cycle의 경우에는 35s면 된다.

일반적으로는 Low Reset을 사용한다. -> 나같은 경우, 버튼이 High일 떄 on이기 때문에 High Reset을 사용하였다.

문제발생

덧셈을 해야하는 상황에서 뺄셈이됨

원인

ALU control이 0(ADD)이 아닌 1(SUB)임을 확인

ALU control 뿐만 아니라 Control Unit에서 나오는 전반적인 신호들이 한 cycle 빨리 나와서 발생한 문제

Schematic 확인 결과 ROM에 저장된 instruction이 바로 Control unit으로 보내짐으로써 Data Path와의 sync가 맞지 않는 현상이 발생한 것 -> 이는 Data path에는 타이밍 통제를 위한 register가 존재하지만 Control Unit에는 없었기에 발생한 문제

해결법

Istruction memory 뒷단에 존재하는 Rgister에서 instruction을 Control Unit으로 전달되도록 코드를 수정하였다.

문제발생

연산한 값이 Register로 들어가지 않음

원인

ALU의 결과값은 정상적으로 나옴을 확인

ALU 다음으로 오는 코드를 확인 결과 ALU 결과값을 저장하는 Register가 고립되어 있음

해결법

도와준것

R타입을 확장했으나, add와 sub만 되는문제가 있었음

처음에는 ALU control의 bit수를 확인 -> 문제없음

case문에서 조건문을 확인했을 때, 최하위bit만 확인하여 경우의 수가 2가지 밖에 나올 수 없었음