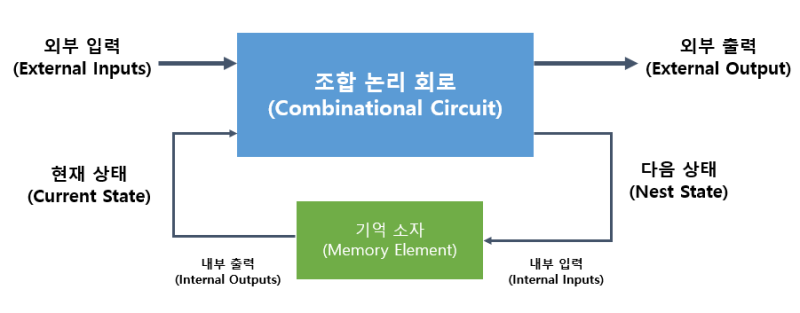

위 이미지와 같은 구조를 갖췄을때 순서논리회로라고 할 수 있다.(기억소자가 핵심)

순서논리회로란?

조합논리회로와의 비교

조합논리회로와 비교하였을때,

조합논리회로: 출력이 현재의 입력에 의해서만 결정되는 논리회로

순서논리회로: 현재의 입력과 이전의 출력상태에 의해서 출력이 결정되는 논리회로

이다.

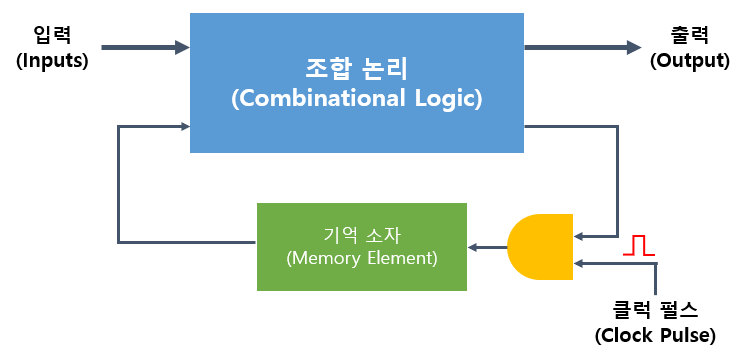

클록 펄스(clock pulse)

조합논리회로로만 회로를 구성하게되면 신호가 들어오고 나가는 타이밍을 조절할 수가 없다. 즉 동기화가 불가능하다. 컴퓨터는 동기화를 위해서 클록펄스라는걸 활용한다. 클록 펄스는 수정 발진자(crystal oscillator)의 규칙적인 진동에 의해 발생하는 일정한 간격을 갖는 전자적 펄스인데, 컴퓨터의 시스템 클록(CPU 클록)은 이 펄스를 타이밍 펄스 또는 디지털 신호로 사용하여 시스템 내의 각 장치와 회로의 모든 동작을 동기화한다.

동기순서논리회로/비동기순서논리회로

순서논리회로는 신호의 타이밍에 따라 동기순서논리회로/비동기순서논리회로로 비교된다.

동기순서논리회로: clock pulse를 활용하여 동작하는 논리회로 (플립플롭)

비동기순서논리회로: 시간과 관계없이 단지 입력이 변화는 순서에 따라 동작하는 논리회로 (래치)

둘은 순서논리회로이기에 모두 상태(이전의 입력값 or 기억소자의 값)에 영향을 받는다.

기억소자

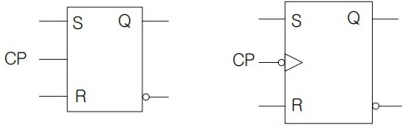

조합논리회로와 구분되는 순서논리회로의 특징인 상태는 기억소자를 활용하여 구현한다. latch와 Flip Flop은 모두 1비트 기억소자이며 Enable 입력으로 clock pulse가 없는 경우 래치 있는 경우 플립플롭이라고 한다.(구분없이 플립플롭이라고 하기도 한다)

Enable 신호가 존재하는 기억소자는 앞에 게이티드가 붙는다.

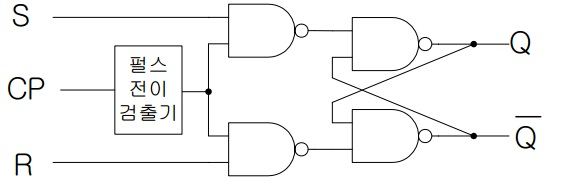

레벨트리거/에지트리거

이때 플립플롭에서는 펄스전이 검출기를 사용해 엣지 트리거 방식을 이용한다. 펄스전이 검출기가 붙으면 회로를 줄여서 삼각형의 형태로 표시한다. 이때 not이 붙어있다면 하강에지 트리거 not이 없다면 상승에지 트리거가 된다.

레벨 트리거 : enable 신호가 하이레벨이나 로우레벨일때 회로가 작동하는 방식

엣지 트리거 : (펄스전이검출기를 연결해) enable 신호가 하이->로우레벨(하강에지)로 가는 순간이나 반대(상승에지)의 경우에 작동시키는 방식 (순간적으로만 신호를 받기 때문에 훨씬 안정적)

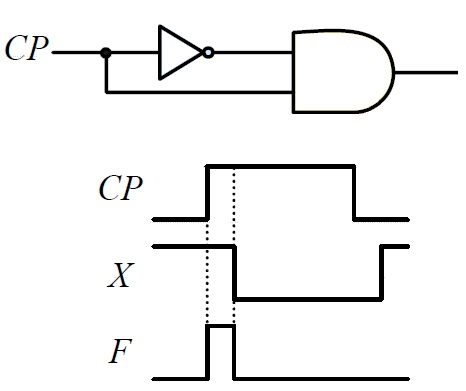

펄스 전이 검출기는 회로도가 위와 같으며 클락펄스가 0에서 1로 변하는 순간만 가로채 입력값을 출력해주는걸 볼 수 있다.(상승에지트리거)

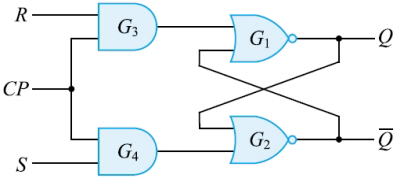

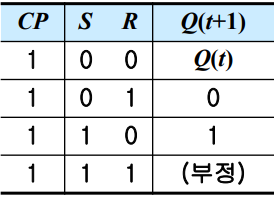

SR 래치(플립플롭)

가장 역사가 깊은 방식으로서 SET(1)-RESET(0)을 의미한다.

위 진리지표와 같이 Q(T) 현재의 상태에 따라 Q(T+1) 미래의 출력값이 변하는 것을 볼 수 있다. 이때 S와 R이 모두 1이 들어오게 되면 (부정)상태로서 어떤 값이 나올지 예측할 수 없다.

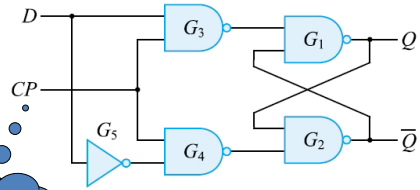

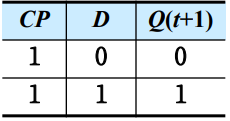

D 래치(플립플롭)

위는 D 게이티드 플립플롭의 회로도이다.

Data를 의미함으로서 데이터를 전달하는 것과 지연(Delay) 기능을 가진다. 입력신호가 EN에 동기화 되어 입력이 그대로 출력에 전달 된다.

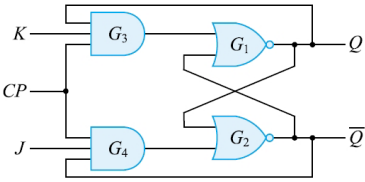

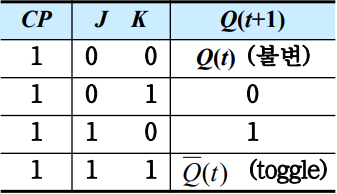

JK 래치(플립플롭)

JK는 이 회로를 고안한 사람들의 이름을 딴 것으로서 큰 의미는 없다. SR에서 (부정)이었던 1 1입력을 개선하여 toggle의 형태로 변환한 기억소자이다.

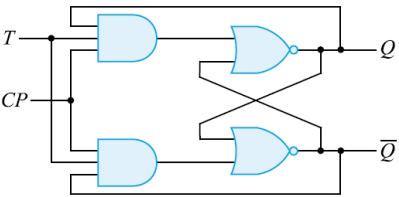

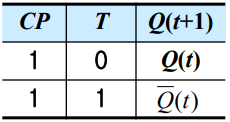

T 래치(플립플롭)

T는 toggle을 의미하며 이전상태를 계속해서 전환해주는 역할을 한다.