클럭

- 클럭속도는 헤르트로 측정함

- 클럭의 속도는 고성능을 요구할때는 높아지고 아닐때는 낮춤

- 오버클럭킹 : 최대 클럭 속도를 강제로 끌어올리는것

코어 📌선택미션

- 명령어를 실행하는 부품의 의미가 'CPU'에서 '코어'로 사용됨

- 명령어를 실행할수 있는 하드웨어 부품

- 오늘날의 CPU : 명령어를 실행하는 부품을 여러개를 포함하는 부품

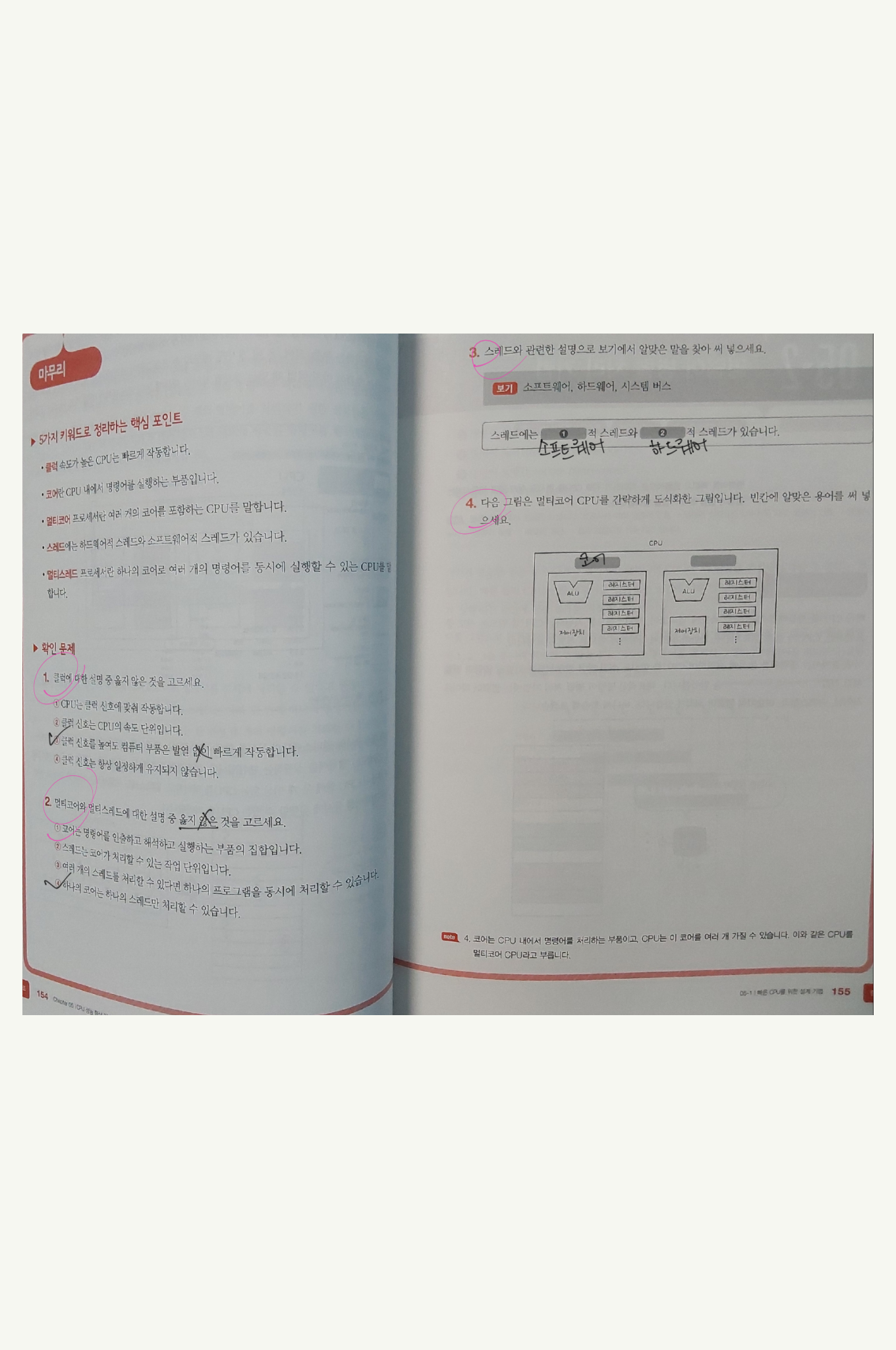

- 멀티코어 CPU(=멀티코어 프로세서) : 코어를 여러개 포함하는 CPU

- CPU의 연산속도가 코어수에 비례해서 증ㄱ사하지 않음

스레드 📌선택미션

- 사전적의미 : 실행 흐름의 단위

- 명령어를 실행하는 단위

- 스레드 종류

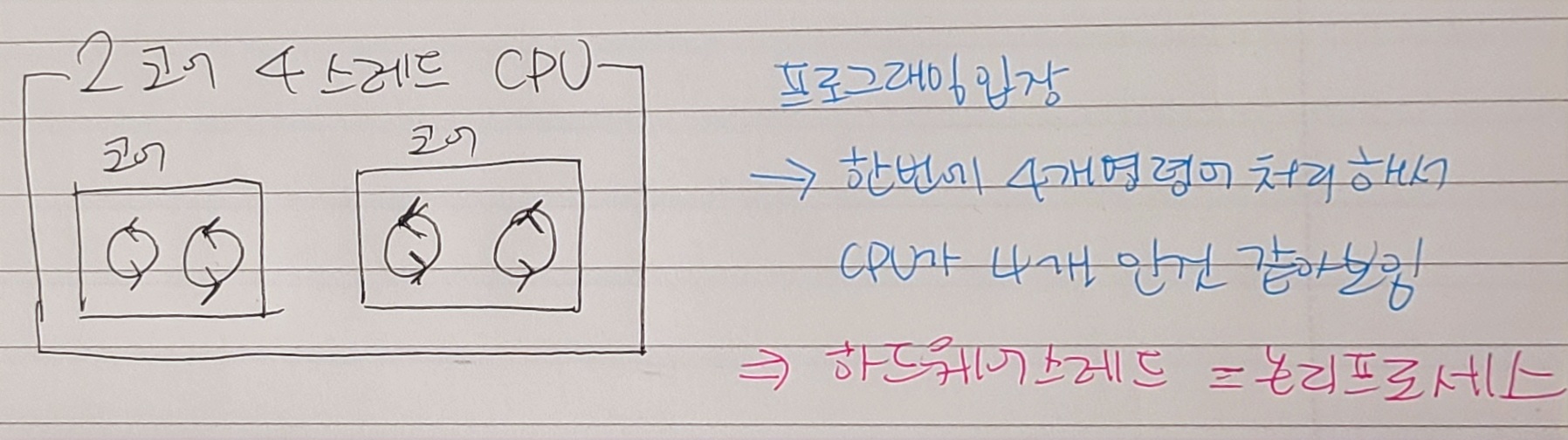

- 하드웨어적 스레드 : CPU에 사용되는 스레드

- 소프트웨어적 스레드 : 프로그램에서 사용되는 스레드

하드웨어적 스레드

- 하나의 코어가 동시에 처리하는 명령어 단위

- CPU에서 사용하는 스레드를 의미함

- 멀티스레드 프로세서(=멀티스레드 CPU) : 하나의 코어로 여러 명령어를 동시에 처리하는 CPU

- 8코어 16스레드 의미 : 명령어를 실행하는 부품이 8개. 한번에 16개 명령어를 처리할수 있는 CPU

- 하이퍼스레딩 : 인텔의 멀티스레드 기술을 의미함

소프트웨어적 스레드

- 하나의 프로그램에서 독립적으로 실행되는 단위

- 프로그래밍언어, 운영체제의 스레드를 의미함

멀티코어 프로세서 📌선택미션

- 명령어를 실행할수 있는 하드웨어 부품이 CPU안에 두 개 이상있는 CPU

멀티스레드 프로세서 📌선택미션

- 하나의 코어로 여러개의 명령어를 동시에 실행할수있는 CPU

명령어 파이프라인

- 명령어 처리과정

- 명령어 인출

- 명령어 해석

- 명령어 실행

- 결과 저장

→ 위의 과정을동시에 처리함 명령어 → 파이프라이닝 : 동시에 여러개의 명령어를 겹처 실행하는 기법

- 파이프라인 위협 : 특정상황에서 성능향상에 실패하는 경우

- 데이터 위험

명령어간 데이터 의존성에 의해 발생함

데이터 의존적인 두 명령어를 동시에 실행할때 제대로 작동하지 않는것을 의미함 - 제어 위험

프로그램 카운터(현재 실행중인 명령어의 다음 주소)의 갑작스러운 변화에 의해 발생함

프로그램 실행흐름이 갑자기 바뀜 → 명령어 파이프라인의 미리 가져온 명령어가 쓸모가 없어질때 발생함 → 해결을 위해 분기예측을 사용

분기예측? 프로그램이 어디로 분기할지 미리 예측하고 주소를 인출하는 기술 - 구조적 위험(=자원 위험)

명령어를 겹처 실행하는 과정에서 서로다른 명령어가 동시에 CPU부품을 사용할떄 발생 함

- 데이터 위험

슈퍼스칼라

- CPU 내부에 여러개의 명령어 파이프라인을 두는 기법

- 매 클럭 주기마다 동시에 여러명령어를 인출, 실행할수 있어야함

- 수퍼스칼라 프로세스(슈퍼스칼라 CPU) : 슈퍼스칼라 구조로 명령어 처리가 가능한 CPU

비순차적 명령어 처리(OoOE: out-of-order-execution)

-

오늘날 CPU성능 향상에 기여한 기법

-

명령어가 어떤 명령어와 데이터 의존성을 가지고 있는 생각해야 함

-

명령어의 순서를 바꿔 실행해도 괜찮은 명령어를 먼저 실행하여 명령어 파이프라인이 멈추는것을 방지하는 기법

1) M(100) ←1

2) M(101) ←2

3) M(102) ← M(100)+M(101)

4) M(150) ←1

5) M(151) ←2

6) M(152) ←3위의 코드와 아래의 코드는 수행결과에 같음 → 순서를 바꿔도 수행결과에 영향을 주지 않음 ▶ 비순처적 명령어 처리기법

1) M(100) ←1

2) M(101) ←2

4) M(150) ←1

5) M(151) ←2

6) M(152) ←3

3) M(102) ← M(100)+M(101)1) M(100) ←1

2) M(101) ←2

3) M(102) ← M(100)+M(101)

4) M(103) ← M(102)+M(101)

5) M(104) ← M(100)3번 1번 명령어는 순서를 바꿀수 없음

4번 1번 명령어는 순서를 바꿀수 없음

4번 5번 명령어는 순서를 바꿀수 "있음"

명령어 집합 구조(ISA: Instruction Set Architecture)

- CPU가 이해할수 있는 명령어 모음

- 같은 CPU까지는 서로 명령어를 이해할수 있고 다르면 이해할수 없음

- 하드웨어가 소프트웨어를 어떻게 이해할지에 대한 약속

CISC (complex instruction set computer)

- 복잡한 명령어 집합을 활용하는 컴퓨터/CPU 설계 방법

- x86, x86-64

- 가변 길이 명령어를 활용함

- 적은 수의 명령어만으로도 프로그램을 동작시킬수 있다

- 명령어가 복잡하여 명령어의 크기와 실행되지 전까지 시간이 일정하지 않음

- 복잡함 명령어의 사용빈도가 낮음

RISC(reduced instruction set computer)

- 명령어의 종류가 적고 짧고 규칙격화된 명령어(고정길이 명령어)를 사용함

- 파이프라이닝에 유리함

- 메모리의 접근하는 명렁어를 load, store로 제한함

- 레지스터를 많이 활용함

마무리 문제