제2장 CPU의 구조와 기능

CPU의 기능(기본적인 기능 2가지)

- 명령어 인출(Instruction Fetch): 기억장치로부터 명령어를 읽어온다.

- 명령어 해독(Instruction Decode): 수행해야 할 동작을 결정하기 위하여 명령어를 해독한다.

-> 모든 명령어들에 대하여 공통적으로 수행

- 데이터 인출(Data Fetch): 명령어 실행을 위하여 데이터가 필요한 경우에는 기억장치 혹은 I/O 장치로부터 그 데이터르 읽어온다

- 데이터 처리(Data Process): 데이터에 대한 산술적 혹은 논리적 연산을 수행

- 데이터 저장(Data Store): 수행한 결과를 저장

-> 항상 수행하는 것이 아니라 명령어에 따라 필요한 경우에만 수행

2.1 CPU의 기본 구조

- 산술논리연산장치(Arithmetic and Logical Unit: ALU)

- 레지스터 세트(Register Set)

- 제어 유니트(Cotrol Unit)

CPU 내부 구성요소

-

ALU

-각종 산술 연산들과 논리 연산들을 수행하는 회로들로 이루어진 하드웨어 모듈

-산술 연산:

-논리연산: AND, OR, NOT, XOR

-

레지스터(Register)

- 액세스 속도가 가장 빠른 기억장치

-CPU 내부에 포함할 수 있는 레지스터들의 수가 제한됨(특수 목적용 레지스터들과 적은 수의 일반 목적용 레지스터들) -

제어 유니트

-프로그램 코드(명령어)를 해석하고, 그것을 실행하기 위한 제어 신호들(Control Signals)을 순차적으로 발생하는 하드웨어 모듈 -

CPU 내부 버스(CPU Internal Bus)

- ALU와 레지스터들 간의 데이터 이동을 위한 데이터 선들과 제어 유니트로부터 발생되는 제어 신호 선드로 구성된 내부 버스- 외부의 시스템 버스들과는 직접 연결되지 않음며, 반드시 버퍼 레지스터들 혹은 시스템 버스 인터페이스 회로를 통하여 시스템 버스와 접속

2.2 명령어 실행

-

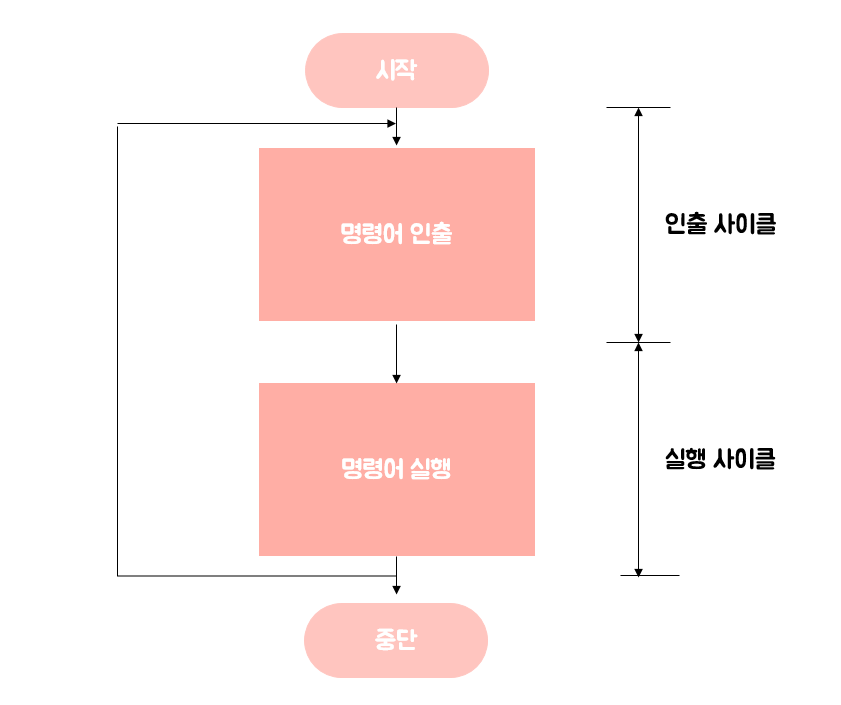

명령어 사이클(Instruction Cycle): CPU가 한 개의 명령어를 실행하는데 필요한 전체 처리 과정으로서, CPU가 프로그램 실행을 시작한 순간부터 전원을 끄거나 회복 불가능한 오류가 발생하여 중단될 때 까지 반복

-

두 개의 부사이클(Subcycle)들로 분리

-인출 사이클(Fetch Cycle): CPU가 기억장치들로부터 명령어를 읽어오는 단계

-실행 사이클(Execution Cycle): 명령어를 실행하는 단계

명렁어 실행에 필요한 CPU 내부 레지스터들

프로그램 카운터(Program Counter:PC)

- 다음에 인출할 명령어의 주소를 가지고 있는 레지스터

- 각 명령어가 인출된 후에는 자동적으로 일정 크기(한 명령어 길이)만큼 증가

- 분기(Branch) 명령어가 실행되는 경우에는 목적지 주소로 갱신

누산기(Accumulator:AC)

- 데이터를 일시적으로 저장하는 레지스터

- 레지스터의 길이는 CPU가 한 번에 처리할 수 있는 데이터 비트 수(단어 길이)와 동일

명령어 레지스터(Instruction Register: IR)

- 가장 최근에 인출된 명령어 코드가 저장되어 있는 레지스터

기억장치 주소 레지스터(Memory Address Register: MAR)

- PC에 저장된 명령어 주소가 시스템 주소 버스로 출력되기 전에 일시적으로 저장되는 주소 레지스터

기억장치 버퍼 레지스터(Memory Buffer Register: MBR)

- 기억장치에 쓰여질 데이터 혹은 기억장치로부터 읽혀진 데이터를 일시적으로 저장하는 버퍼 레지스터

2.2.1 인출 사이클

인출 사이클의 마이크로 연산(Micro-operation)

단, 는 CPU 클록(clock)의 주기

|첫번째 주기| 현재의 PC 내용을 CPU 내부 버스를 통하여 MAR로 전송

|두번째 주기| 그 주소가 지정하는 기억장치 위치로부터 읽혀진 명령어가 데이터 버스를 통하여 MBR로 적재되며, PC의 내용에 1을 더한다

|세번째 주기| MBR에 있는 명령어 코드가 명령어 레지스터인 IR로 이동

- ex) CPU 클록 = (클럭 주기 ) -> 인출 사이클: 소요