컴퓨터의 성능은 기본적으로

1.instruction 개수

2.clock cycle frequency

3.CPI(Cycle per Instruction)

에의해 결정된다.

프로그램에 필요한 instruction 수를 결정하는건 컴파일러와 명령어 집합구조(ISA) 이다.

나머지 clock cycle frequency와CPI를 결정하는건 프로세서의 구현 방법이다.

MIPS Overview

모든 명령어 실행은 PC를 사용하여 메모리에 있는 명령어를 읽어오는 것으로부터 시작된다.(fetch)

가져온 명령어로부터 어떤 레지스터를 읽어 와야하는지 알수있다.

이후에는 연산을 위해서 ALU로 간다.

산술/논리 명령어는 ALU 결과를 레지스터에 쓴다.

적재(lw)나 저장(sw) 명령어는 ALU 결과를 메모리 주소로 사용하여 레지스터 값을 저장하거나 레지스터에 적재할 값을 읽어 온다.

ALU나 메모리에서 나온 결과는 레지스터 파일에 넣는다.

분기 명령어의 경우는 ALU 출력을 사용하여 다음 명령어 주소를 결정한다.

이주소는 그림 위쪽에 덧셈 연산기에서(pc와 분기주소가 더해진 값)나오거나 그 왼쪽 덧셈기에서 나온다.

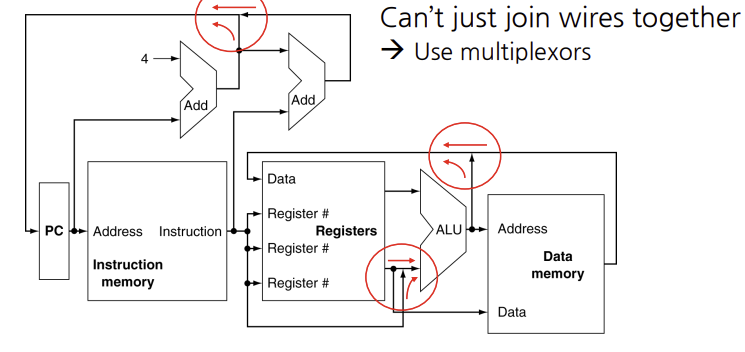

그런데 위 그림은 명령어 실행에 중요한 두가지를 빼고 있다.

-

서로 다른 근원지에서 나온 데이터가 같은 유닛으로 가는 곳이 몇군데 있다. 예를들면,PC에 들어갈 값은 두 덧셈기 중 하나에서 나오고, 레지스터 파일에 쓰일 데이터는 ALU나 데이터 메모리에서 나오며, ALU의 두번째 입력은 레지스터나 명령어 수치 필드서 나온다. 그런데 데이터 선들을 보면, 동시에 여러 곳을 데이터가 이동하는 것처럼 나와 있지만, 그럴수가 없다.

그래서 여러 이동 경로중 하나만을 선택할 수 있도록 하는 장치가 필요하다.

이것이 바로멀티 플렉서(multiplexor)이다.데이터 선택기라고 불리기도 한다. 멀티 플렉서는 제어선 값에 따라 여러개 입력중에서 하나를 선택한다. -

어떤 유닛들을 명령어 종류에 따라서 다르게 제어되어야 하는데, 이 부분이 빠져있다. 예를들어서, 데이터 메모리는 lw에서는 읽기, sw에서는 쓰기를 해야한다. 레지스터 파일은 lw, 산술/논리 연산에서는 쓰기를 한다.

ALU는 여러가지 연산중 하나만 해야하는데, 멀티플레서 처럼 명령어의 여러 필드값에 따라 정해지는 제어선에 의해 통제된다.

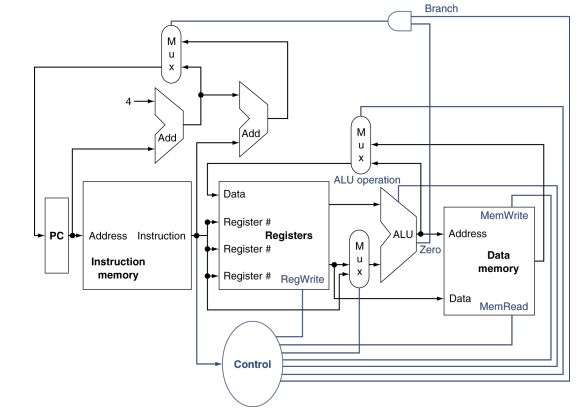

다음 그림은 멀티플렉서 세개를 추가한 그림이다.

control유닛은 기능 유닛들과 두 멀티 플렉서의 제어값을 결정하는데 사용하며, 명령어를 입력으로 한다.

덧셈 연산기 위에 있는 멀티플렉서는 PC+4와 분기 목적지 주소중 어느 것을 PC에 써야 할지 결정하는 것인데, ALU의 Zero 출력으로 제어된다.

이 출력은 beq에서 비교할때에 사용된다.

논리 설계

MIPS 구현에 쓰이는 데이터패스 요소는 두 가지 종류의 논리 소자들로 구성된다. 데이터 값에만 동작하는 element와 상태를 포함하는 element이다.

데이터값에만 동작하는 element는 combinational element이다.

이 element는 출력이 현재의 입력에만 의존한다. combinational element는 같은 입력이 주어지면 항상 같은 출력을 낸다.

ex) ALU

또다른 element는 state를 갖는다. element 내부에 기억장소가 있으면 상태를 갖게 된다. 이러한 element를 state element라고 부른다.

그 이유는 컴퓨터의 플러그를 빼도 플러그를 빼기전에 element가 가지고 있던 값들로 state element를 다시 load하면 다시 시작할 수 있다.

state element들을 저장했다가 다시 복원하면 컴퓨터가 꺼지지 않았던 것과 마찬가지다.

ex) 명령어 메모리, 데이터 메모리 및 레지스터

state element는 적어도 2개의 입력과 1개의 출력을 갖는다. 꼭 있어야 하는 입력은 clock과 기록할 data이다. clock입력은 데이터 값이 element에 기록되는 시점을 결정한다.

element의 출력은 이전 clock cycle에 기록된 값이다.

논리적으로 가장 간단한 state element중 하나는 D형 플립플롭인데 D형 플립플롭에는 두개의 입력(데이터 값과 clock)과 하나의 출력이 있다.

MIPS 구현에는 플립플롭말고도 두개의 state element가 더 사용된다.

바로 메모리 와 레지스터 이다.

state element에 언제 쓸 것인가는 clock이 결정하지만, 읽는것은 언제든지 할 수 있다.

state를 포함하는 논리소자들은 순차회로(sequential circuit) 라고 부른다.

이는 이들의 출력이 입력뿐만 아니라 내부 state에도 의존하기 때문이다.

EX) 레지스터 파일의 출력은 입력되는 레지스터 번호와 전에 레지스터에 기록된 값 모두에 영향을 받는다.

클러킹 방법론(clocking methodology)은 신호를 언제 읽을 수 있고 쓸 수 있는지를 정의한다. 이게 중요한 이유는, 만약에 신호를 읽고 있는데 동시에 누군가가 새로운 값을 쓴다면 읽은 값은 옛 값일 수도 있고, 새로 쓴 값일 수도 있다. 아니면 두 값이 뒤섞인 것이 될 수도 있다. clocking methodology는 이러한 것을 해결하고, 예측 가능성을 보장하기 위해서 고안되었다.

에지 구동 클러킹(edge-triggered clocking) 방법론은 순차논리소자(sequential logic element)에 저장된 값은 clock edge에서만 바꿀 수 있다는 것을 의미한다. clock edge란 낮은 값에서 높은 값 혹은 그 반대로의 빠른 변이를 말한다.(위그림 참고)

동기식 디지털 시스템에서는 state element가 내부 저장장치에 언제 값을 쓸 것인지를 clock이 결정하게 된다. state element의 모든 입력은 활성화된 clock edge가 상태를 바꾸기 전에 안정된 값(즉 clock edge 후까지 변하지 않을 값에 도달하였음을 뜻한다.)

ex) state element가 상향에지 구동이라면, 모든 state element는 상향 clock edge에서 값이 바뀐다.

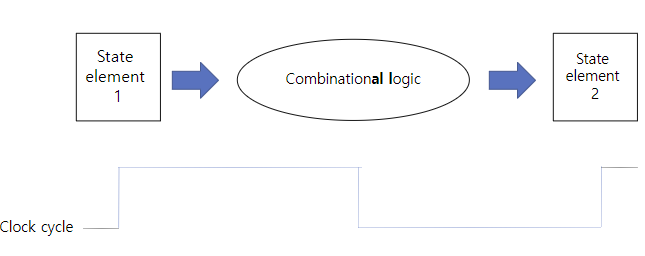

모든 combinational circuit은 state element에서 입력을 받고 state element로 출력을 내보낸다. 입력은 이전 state element에서 쓴 값이고 출력은 다음 clock cycle에서 사용할 수 있는 값이다.

위의 그림처럼 신호가 state element1에서 나와 combinational logic state element2까지 도착하는데 필요한 시간이 clock cycle의 길이를 정의하게 된다.(1 cycle)

clock신호와 쓰기 제어 신호는 state element의 입력이며, 쓰기 제어신호가 인가(assert)되고 활성화 clock edge일때만 state element가 변하게 된다.

asserted(인가된) 이란 용어는 논리적으로 높은 신호를 표시하며 assert(인가)라는 용어는 신호를 높은 값으로 만든다는 뜻이다. 논리적으로 낮은 값을 표시하기 위해서는 비인가(deassert)또는 비인가된(deasserted)라는 용어를 사용한다.

assert 혹은 deassert라는 용어를 사용하는 이유는 하드웨어를 구현할때 때때로 1이 높은 값을 표현하기도 하고, 낮은 값으로 표현되기도 하기 때문이다.

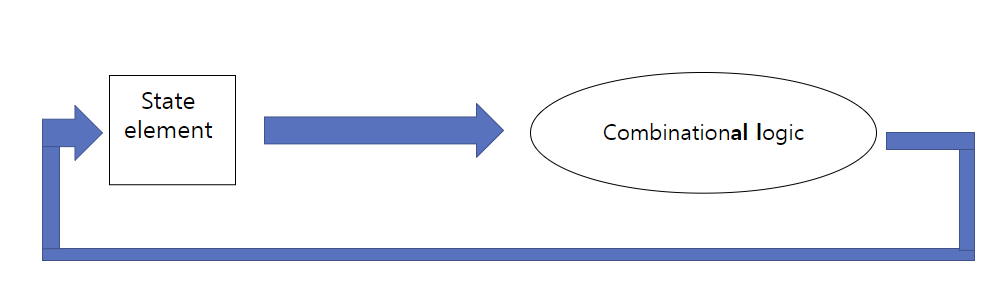

위 그림과 같이 에지 구동 방법은 레지스터 내용을 읽고 그값을 조합회로로 보내고 같은 레지스터에 쓰는 작업 모두가 한 클럭 사이클에 일어나는 것을 허용한다. 쓰기가 하향 clock에서 일어나던지 혹은 상향 clock 이던지 상관없다. 왜냐하면, combinational logic에 대한 입력은 선택된 clock edge에서만 변하기 때문이다.