예외: branch나 jump 명령어가 아니면서 명령어 실행의 정상적인 흐름을 바꾸는 사건, 예외 인터럽트 라고도 불리며 프로그램 실행을 방해하는 계획되지 않은 사건, 오버플로우 검출에 사용

(예외와 인터럽트를 구분하지 않고 사용하기도 한다. 하지만 여기서는 제어흐름에서의 예기치 못한 변화를 지칭하는데 예외, 사건이 외부적인 요인으로 일어날 경우에만 인터럽트라는 용어를 사용한다.)

예외는 처음에 프로세서 내부로부터의 예상치 못했던 사건을 처리하기 위해 만들어졌다.

모든 프로그램을 모든 가능한 우연에 대한 계속적인 체크(a.k.a polling)와 함께 쓴다.

사용 불가능한 일이 없는 최선의 경우를 위한 normal 프로그램을 쓴다.

- 하지만 하드웨어에서 예외적인 상태를 검출해야 한다.

- 제어를 exception handler로 이동시킨다. exception handler는 상태를 해결하고 프로그램으로 다시 돌아가는 방법을 알고있다.

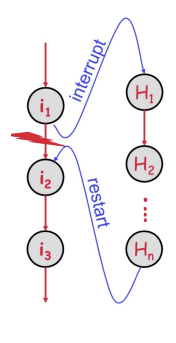

interrupt Control transfer

위의 그림처럼 interrupt는 unplanned fuction call(system routine을 call한다.)이 일어난다.the interrupt handler라 부름

normal function call은 control transfer를 예상하고 준비하고 있지만 interrupt function call은 그렇지 않다.

Control은 main thread로 돌아간다.

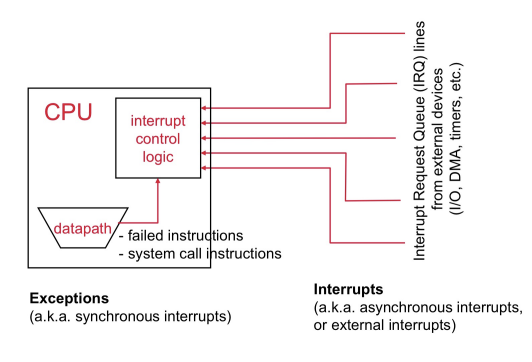

Types of interrupts

synchronous Interrupts(a.k.a. exceptions)

- Exceptional condition들은 특정 instruction과 관련이 있는데

예를들어, illegal opcode,illegal operand, virtual memory management faults - instruction이 잘못 되어서 불러오지 못했을 경우

Asynchronous Interrupts(a.k.a interrupts)

- 외부사건으로 인함, instruction과 관련 없다.

ex. I/O events, timer events - 다룰때 좀더 유연하다.

조금의 지연은 허용, 하지만 영원히 미룰수는 없다.

3.System Call/Trap Instruction

- 이것들의 목적은 오직 raise an exception (예외 발생) 이다.

Virtualization and Protection

modern OS는 time-shared multiprocessing을 지원하지만 process는 하나만 작동한다.

OS는 여러 기능 set을 관리하고 실행한다.

- user-level process 밖에서 low-level details를 유지한다. e.g. HW device handler, thread scheduler

- user-level process를 다른 누군가나, 자신으로부터 보호한다.(예를들어 한 컴퓨터에 여러 유저가 있을 수 있는데, 다른 유저가 내 컴퓨터에 침입하지 못하게 보호)

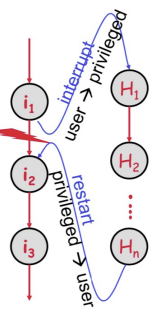

control and Privilege Transfer

- user-level code는 privileged mode에서는 실행되지 않는다.

- processor는 interrupts 에서만 privileged mode로 들어간다.

- handler는 다시 privileged mode에서 user mode로 돌아가게 한다.

Implementing Interrupts

Handling Exception in MIPS

MIPS에서는 exception이 System Control Coprocessor(CP0)(보조 CPU)에 의해서 관리된다.

예외가 일어난다면

예외가 일어났을때 컴퓨터가 해야되는 기본 동작은 문제를 일으킨 명령어의 주소를 예외 프로그램 카운터(Exception Program Counter:EPC)에 저장하고 어떤 특정 주소에 있는 운영체제로 제어를 옮기는 것이다.

그러고나면, 운영체제는 알맞는 행동을 할 수 있다. 이러한 행동은

1. 사용자 프로그램에 어떤 서비스를 제공한다든지

2. 오버플로에 대하여 미리 정의된 행동을 취한다던지

3. 프로그램의 실행을 중지하고 오류를 보고한다.

예외 때문에 필요로 했던 행동들이 끝난후 운영체제가 프로그램을 끝내든지 아니면 실행을 계속 할 수 있다.

실행을 계속할 경우에는 어느 곳에서 실행을 재개해야 하는지를 판단하기 위해서 EPC 를 사용한다.

예외의 원인 찾기

-

Cause register라 불리는 상태 register를 이용한다. 이 상태 레지스터는 예외 원인을 나타내는 필드를 가지고 있다. -

vectored interrupt를 사용한다. 이방법은 control이 옮겨져야 되는 주소가 예외의 원인에 의해 결정된다.

예를들면,

| 예외 종류 | 예외 벡터 주소 |

|---|---|

| undifined opcode | 8000 0000(hex) |

| overflow | 8000 0180(hex) |

이런식으로 예외 종류에 따른 예외 벡터 주소가 정의 되어 있다.

운영체제는 예외가 시작되는 주소를 보고 그 원인을 안다. 주소는 32바이트씩 떨어져 있으며 운영체제는 예외의 원인을 기록해야 하고 제한된 처리를 차례대로 해야한다. 예외가 벡터화가 안되어 있으면 모든 예외에 대해 하나의 시작점이 사용될 수 있으며 운영체제는 이유를 알아내기 위해 상태를 해독해야 한다.

EPC(Exception Program Counter): 예외가 일어났던 명령어의 주소를 보관하기 위해 사용되는 32비트 레지스터

Cause:예외의 원인을 기록하는 데 사용되는 레지스터

Precise Interrupt/Exception

- PC 이전의 instruction은 모두 실행이 끝난상태(fully executed)

- PC 이후의 instruction은 아직 실행이 되지 않음.

- interrupted handling 편의성 때문에 OS 개발자들에게 유리

Imprecise Interrupt

- instruction에서 병렬적으로 실행되는 상황

- CPU에서 이미 처리중인 instruction중 하나가 펑크가 나면, 이미 CPU에 올라간 다른 모든 instruction에 대해 handling을 진행해야 함.(비용이 많이 든다.)

- interrupt가 발생하면 속도가 크게 저하

- interrupt handling을 위해 OS가 복잡해짐.

- interrupt가 잘 발생하지 않는 환경에서는 performance가 좋다.

- interrupt 또는 exception의 원인인 명령어와 정확히 연관되지 않은 파이프라인(어떤 명령어가 문제를 일으켰는지 결정하는 것은 OS에 맞긴다.)

Exception Sources in Different Stages

- IF: Instruction memory address/protection fault

- ID: Illegal opcode

- EX: overflow,divide-by-zero

- MEM: Data memory address,protection fault(사용자가 메모리에 접근하려고 하지만 접근권한이 없어서 접근하지 못하는것 )

- WB: instruction을 멈출수있는게 아무것도 없다.

Exception in a pipeline

- 파이프라인 구현은 exception을 control hazard의 다른형태로 취급한다. 예를 들어 add 명령어가 산술 overflow를 가진다고 생각하자. branch가 일어났을때 했던 것처럼 add 명령어의 다음 명령어들을 파이프라인에서 쓸어버리고 새로운 주소에서 명령어를 가져와야 한다.

branch가 일어났을 때 사용했던 것과 같은 방법을 사용할 예정이지만, Exception에서는 인가를 해제한다.

MIPS 예외주소인 8000 0180(hex)로부터 명령어를 인출하기 위해서는 PC 멀티플렉서에 입력을 추가하여 8000 0180(hex)값을 PC로 보낼 수 있게 한다.

Multiple Exceptions

- 한 clock cylcle에서 여러개의 예외가 동시에 일어날 수 있다.

보통의 해결책은 예외에 우선순위를 두어서 어떤 것이 먼저 서비스되어야 하는지 결정하기 쉽도록 만드는 것이다.

대부분 MIPS에서는 가장 앞선 명령어가 인터럽트 되도록 하드웨어가 예외를 정렬해 준다.