10 Edge-Triggered D-Latch

😊 Edge-Triggered 이란?

-> C가 rising/falling 하는 그 순간에만 동작하는 방식이다.

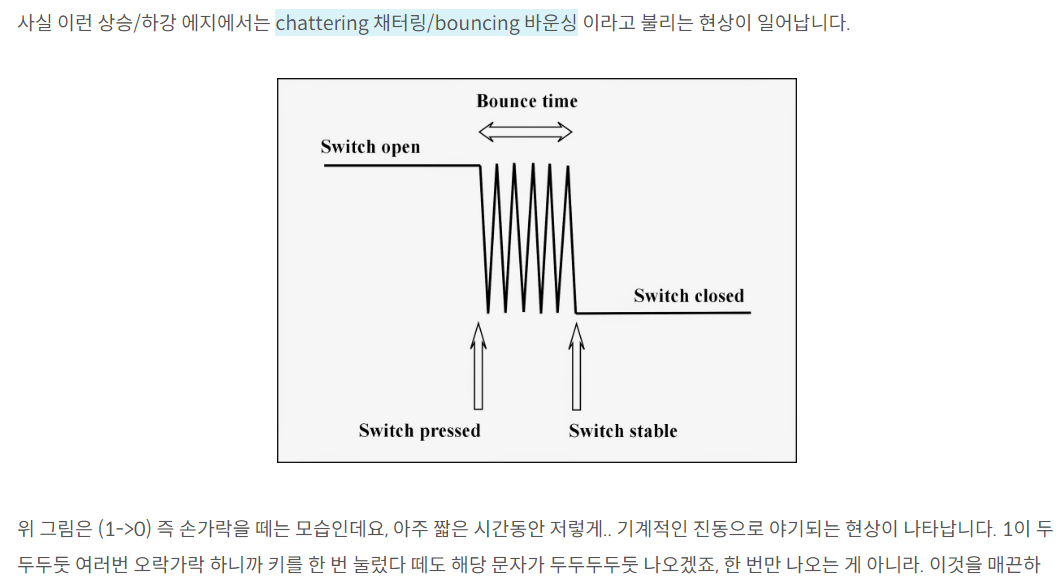

"edge"를 타자로 치는데, e 잠깐 쳤는데도 ee가 쳐지면 굉장히 불편할 것이다.

만약, Edge-Triggered 를 사용한다면 e 잠깐 치면 한번 나오고, e를 길게 누르면 연속적으로 eeee.. 나오게 할 수 있을 것이다.

한마디로, 특정 조건에서 한 단계만 동작하도록 D-Latch를 설계한 것이다.

😊 Flip-Flop 이란?

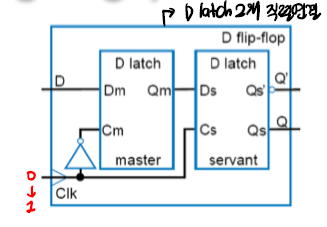

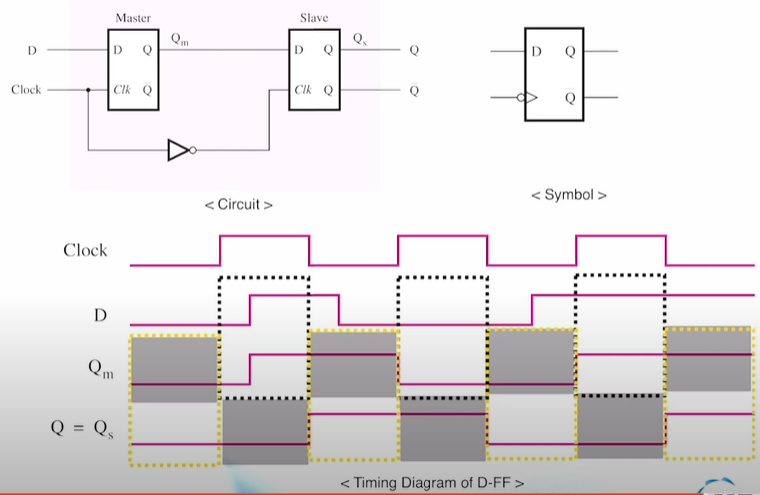

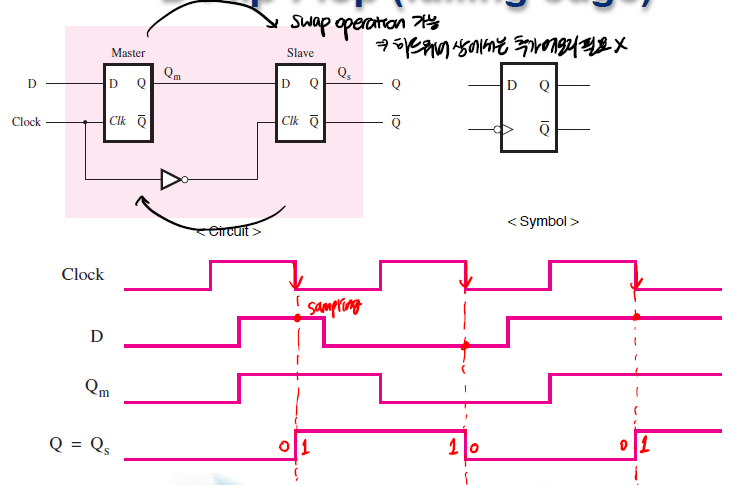

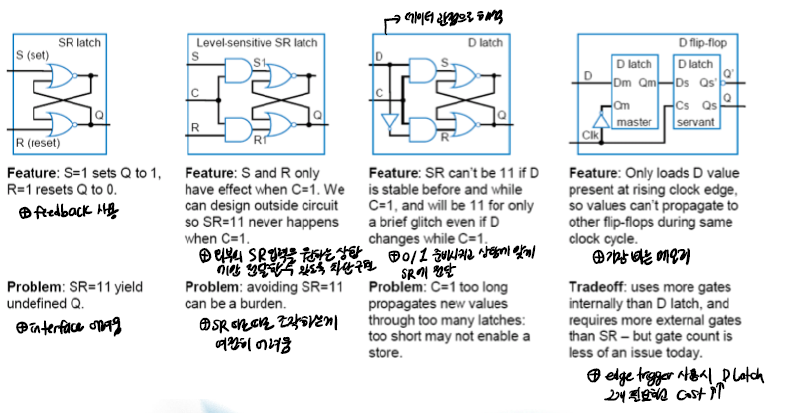

Edge-triggered 중 한 디자인은 master-slave 라고 부른다.

D Latch 가 2개 필요하다.

C=0 일 때, master가 켜지고 D로부터 값을 복사한다.

C=1 일 때, slave가 켜지고 master의 값을 복사한다.

⭐ slave의 출력이 진짜 출력이라고 보면 된다.

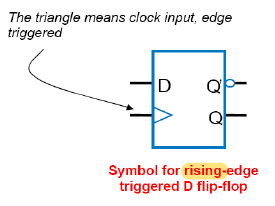

Rising Edge

C가 0에서 1로 변화하는 순간을 나타낸다.

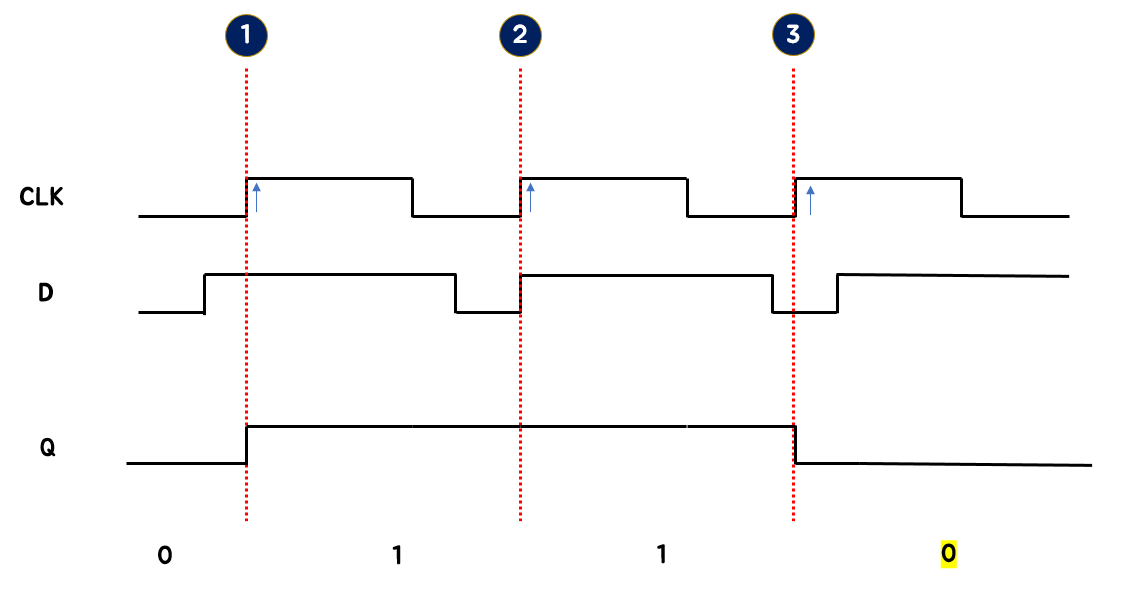

다음과 같이 C가 rising 하는 순간의 D만 출력 Q에 반영된다.

Falling edge

C가 1에서 0로 변화하는 순간을 나타낸다.

No More Unknown Propagation

Solves problem of not knowing through how many latches a signal travels when C=1.

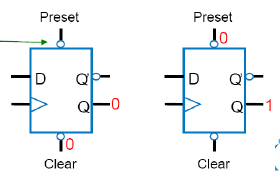

Preset and Clear

Flip-Flop에 preset과 clear을 추가할 수 있다.

preset과 clear은 C와 상관없이 입력되는 비동기 신호이다. preset에 1이 입력되면 1이 출력된다. 일종의 초기화 동작이라고 볼 수 있다.

C보다 우선하는 비동기식 입력단자로, 처음 전원을 켰을 때 Flip-Flop의 상태를 원하는 데이터로 초기화 할 수 있다.

- Preset: Flip Flop을 1로 set 하는 input 이다.

- Preset=1, no effect- Preset=0, Q=1

- Clear: Flip Flop을 0으로 reset 하는 input 이다.

- Clear=1, no effect- Clear=0, Q=0

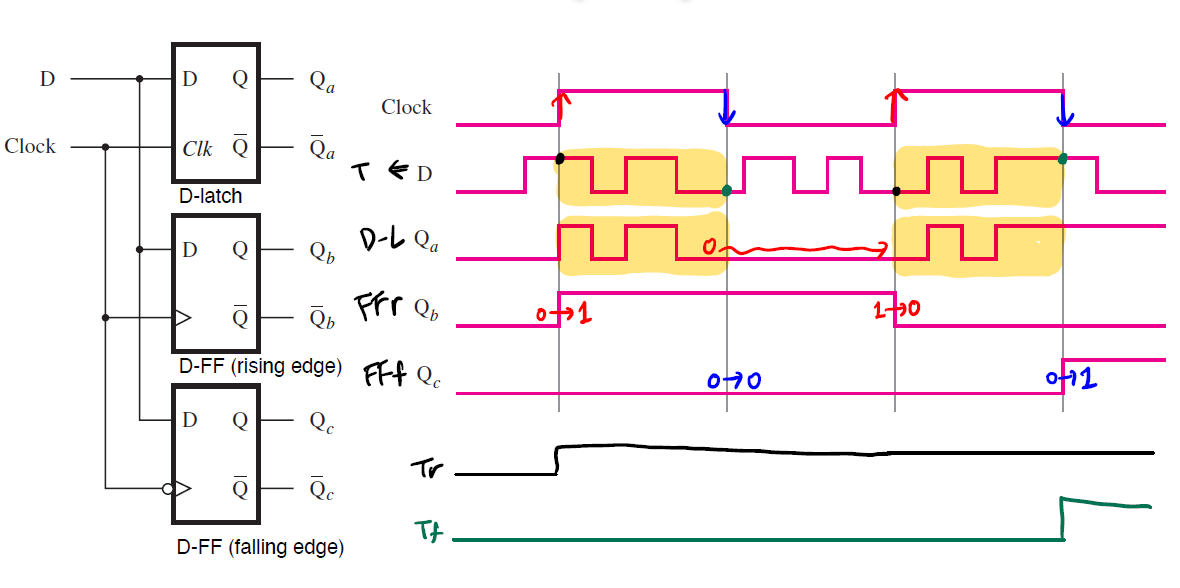

D Latch vs. D-FF

rising edge 순간의 D를 보면 1 이므로 FF-r 쭈우우욱 1