09 Level-Sensitive D-Latch

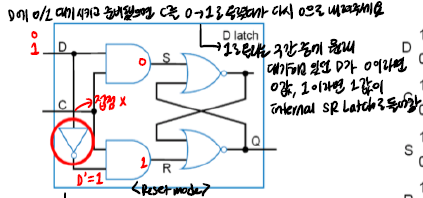

SR Latch 에서 조작이 더 쉽고, 인터페이스를 좀 더 간단히 바꾼 것이라고 보면 된다.

특히, R이 항상 S의 inversion이 되도록 D라는 inverter를 넣어준 것이다.

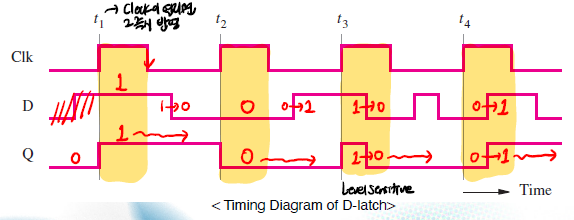

위 그림을 보면 D라는 inverter를 넣어주고, D에 0이나 1을 대기시킨다.

C를 0에서 1로 올리는 구간 중에 대기하고 있던 D가 0이라면 0값을, 1이라면 1값을 internal SR Latch로 보낸다.

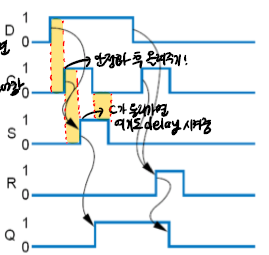

하지만, 안타깝게도 이 D-inverter 조차 delay가 존재한다.

따라서, 위와같이 D가 안정화 된 후에 C를 올려준다.

전에 언급했듯이 C에도 delay가 있기 때문에 SR에 늦게 도착한다.

Problem

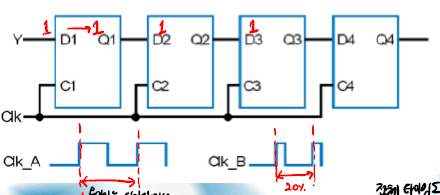

'C=1일 때, 몇개의 latch를 지날 것인가?' 에 대한 문제이다.

올라가는 타이밍에서 다시 올라가는 타이밍이 나오는게 한 주기라고 할 때, 다시 올라가기 전까지 값이 나오는 주기를 설정하기 어렵다는 것이다.

Clk_A의 경우 주기가 길지만, Clk_B의 경우 주기가 짧다.

따라서, 전체 타이밍도 흔들리고, 폭도 미세하게 흔들릴 수 있다. 통제하기 굉장히 까다롭다는 뜻이다.

위 그림처럼 전달되는 과정에서 정밀한 통제가 불가능하고, SR Latch 내부적으로도 순간적으로 S=1, R=1이 들어갈 수 있는 위험이 존재한다.