03 MUX, DEMUX

XOR/XNOR Gates

- XOR gate: 1의 갯수가 홀수면 1, 짝수면 0 이다.

- XNOR gate: XOR gate 결과의 반대이다.

이렇게 하다보면 cost 가 너무 비싸다는 것을 알 수 있다.

Multiplexers (MUX)

여러 입력 신호 중 하나를 선택하여 선택된 입력을 하나의 출력선에 전달하는 장치이다. 복잡한 회로를 조건에 따라 나눈다면 각각의 sub-circuit은 훨씬 간단하게 디자인 할 수 있다.

또한, 'N개의 input:1개의 output MUX' 형태이다.

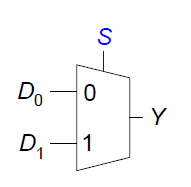

- 2:1 MUX

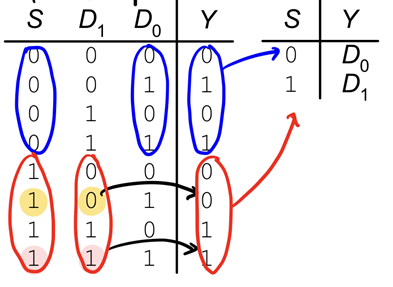

여기서 S는 Select Signal 이다.

패턴을 살펴보면 S가 0일 때 Y가 D0 이라는 것을 알 수 있고, S가 1일 때 Y가 D1 과 같다는 것을 알 수 있다.

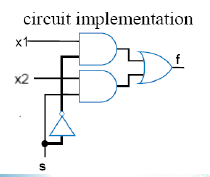

이것을 circuit implementation 한다면, 다음과 같은 형태를 띈다.

- f = s'x1 + sx2

NOT gate 를 사용하여, s가 0이면 x1만 살아남고, s가 1이면 x2만 살아남도록 설계했다.

⭐ 참고로, MUX는 larger designs 로 확장될 수 있는데, 2:1에서 3:1로 넘어가면 낭비가 심하므로 짝수번으로 넘어간다.

이때, 2:1 MUX는 1 select signal, 4:1 MUX는 2 select signal, 8:1 MUX는 3 select signal 을 필요로 한다.

-> 패턴을 보면, n:1이라고 했을 때, select signal 은 log2n 인 것을 알 수 있다.

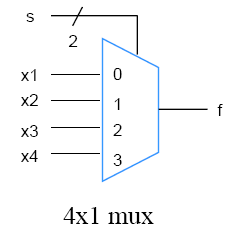

4:1 MUX의 2 select signal 을 표현하기 위해서는 다음과 같이 표기한다.

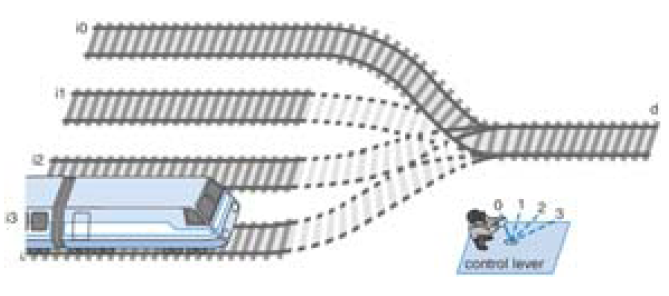

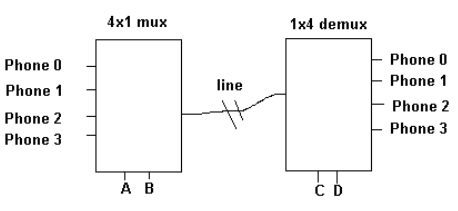

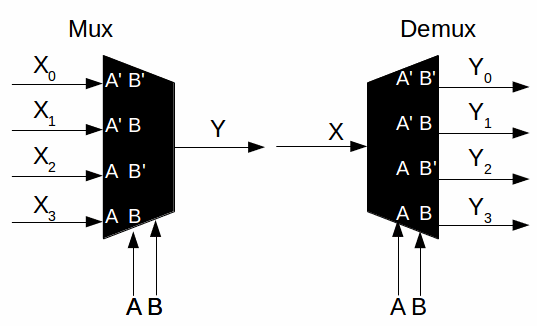

DEMUX

반대로, DEMUX는 하나의 입력 신호를 받아서 수많은 데이터 출력선 중 하나를 선택하는 장치를 말하며 단일 입력으로 연결된다.