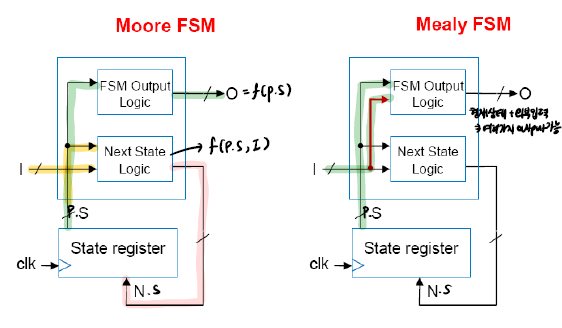

14 Mealy Machine

Mealy vs. Moore

무어의 경우 output이 현재 상태만 보면 결정됐다. 다른 말로 현재 상태가 결정되면 표현할 수 있는 output이 딱 정해져버린다.

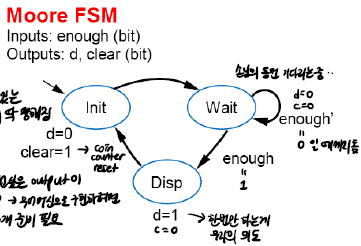

그래서 내가 표현하고 싶은 output이 10종류 일 때, 무어머신으로 구현하려면 상태도 10개가 필요해진다.

Init과 Wait을 강제로 합쳐본다면?

-> clear를 0으로 통일하면 잔돈이 랜덤으로 떠있을 수 있다.

😊 하지만, 밀리머신으로 구현한다면 현재 상태 + 현재 들어오는 입력을 둘 다 고려해서 조건부 출력이 가능해진다 !

이처럼 상태 개수를 하나 줄일 수 있다.

외부 입력을 / 앞에 적는다. 아무것도 없다는 것을 입력을 안보겠다는 뜻이다. (입력 구분 x)

enough' 는 입력 조건인데, enough'/c=0, d=0 과 마찬가지이다.

enough 가 1일 때, d=1과 c=0이 가능해진다.

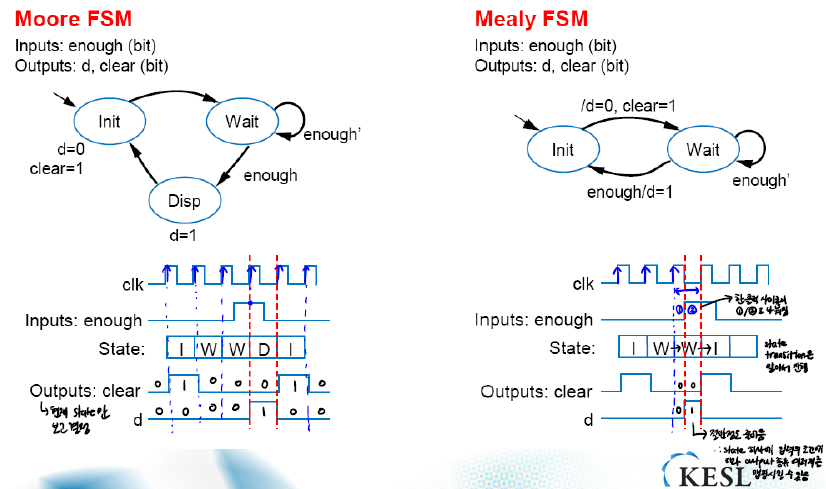

밀리머신을 보면, 한 clock cycle 중간에 enough가 올라간다.

결국 한 clock cycle이 1번과 2번으로 나누어지는데, 이때 1번은 enough=0 이다.

이때 clear와 d를 0, 0으로 쏴준다. 이후 enough 가 올라갔으면 즉시 d에 반영해준다.

🤔 이렇게 하면 문제 생기는거 아닌가?

-> enough 안에서 흔들릴 수 있기 때문에 가급적이면 enough 로 들어오는 signal 들이 다른 D-FF을 거쳐서 안정화 된 상태여야한다.

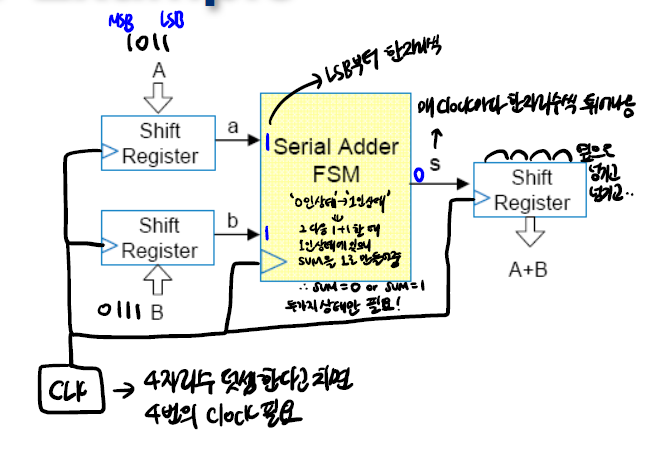

Example 1: Serial Adder

n-bit 덧셈을 하기 위해서 n clock cycle 이 필요하게 된다.

clock cycle 일 때마다 1-bit 짜리를 옆으로 계속 넘기고 넘기고 한다.

이때, 모두 같은 clock 을 share 한다. 4-bit + 4-bit 의 경우 각각 4번의 clock cycle (총 8번) 이 필요할 것이다.

FSM 에서는 한번에 LSB 부터 한자리씩 입력을 받는다.

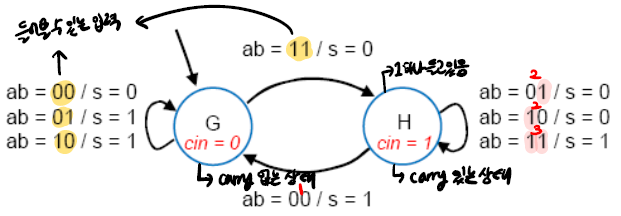

FSM 에서 어떤 상태가 필요할까?

-> 덧셈할 때 carry를 고려해야한다. carry 를 기억하고 있어야 한다.

위 그림과 같이 1011과 0111을 더하는 경우를 생각해보자.

처음에 a=1, b=1 이 들어오면 s=0 이 된다. 그렇다면 여기서 carry는 어떻게 되는걸까?

-> carry 상태가 0 에서 1로 바뀐다 !

-> 다음에 또 a=1, b=1 이 들어오면 carry 상태가 0이 아닌 1에 있으므로 s=1 이 된다 !

오른쪽의 경우 carry가 1 있는 상태라 오른쪽 입력조건을 고려했을 때 1이 총 2, 2, 3개가 된다.

이렇게 되면 carry가 또 발생한 꼴이니 다시 H로 돌아와서 그 상태 (carry=1) 를 유지한다.

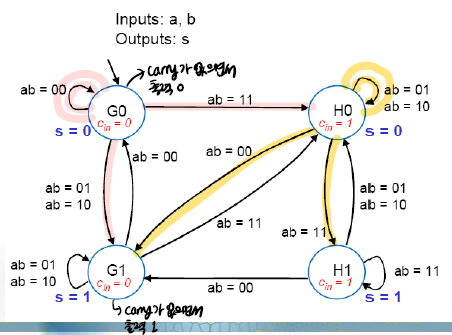

⭐ 따라서, 상태 2개만 정의하면 된다.

이거를 무어머신으로 구현하려면 다음과 같이 된다.