07 SR Latch

Bit Storage

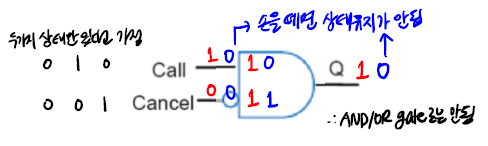

Combination logic 에서는 입력에 바로 반응한다.

입력에 변화가 감지되면 출력도 combination logic 자체의 delay 후에 업데이트 된다. -> 결국, 쉬운 solution 은 없다.

위 그림을 봤을 때, 손을 떼면 상태유지가 되지 않는다. AND gate 로는 쉽사리 해결되지 않는다.

🐣 따라서, 출력을 입력으로 넣는 "feedback" 기능이 필요하다.

-> OR gate 에서 feedback 사용 시 상태유지가 일부분 구현은 된다.

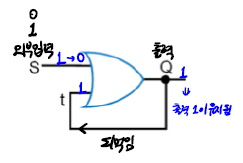

Feedback (되먹임)

하지만, feedback 에는 문제가 있다. 바로 "OTP ROM" 이라는 것이다.

다시 끄려고 0을 넣어도 출력에 변화가 없다.

😨 이 말은 즉슨, 한번 1을 넣은 이상 0으로 돌아갈 수 없다 !!

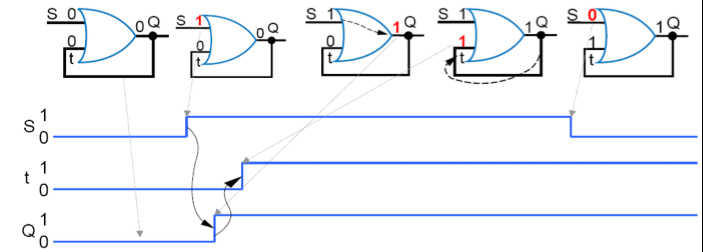

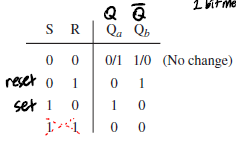

SR Latch

Latch는 1-bit 정보를 보관/유지할 수 있는 회로이고, sequential logic의 기본요소이다. combinational logic과 다르게 이전 상태를 유지하여 저장할 수 있다.

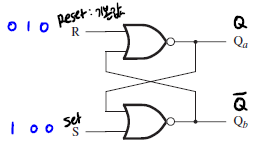

🐣 OTP를 극복하기 위해 NOR gate 2개를 사용해서 SR Latch를 만든다. 추가로 feedback을 사용해서 되먹임 시키면, 1-bit memory를 만들어서 제어할 수 있다 !

엑셀과 브레이크라고 가정했을 때, 동시에 밟으면 안된다는 특성을 가졌다.

입력이 0과 1이거나, 1과 0이거나, 0과 0이어야 한다. 하지만 1과 1은 안된다.

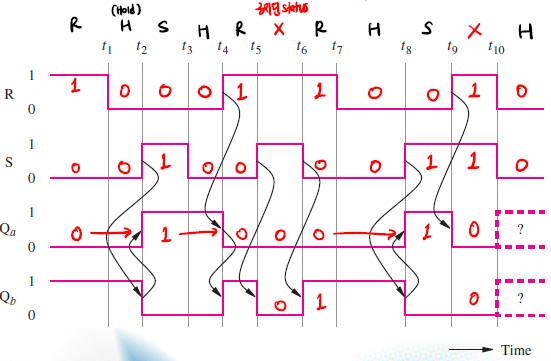

No change 라는 것은 S와 R이 0이면, 출력 상태를 변경하지 않고 그대로 둔다는 것이다. (Hold) -> Q와 Q'은 Inversion 관계이다.

처음에 R=1, S=0 이니까 Reset 돼서 0 되고, R=0, S=0 이니까 H로 상태유지 했다가, 다음에 R=0, S=1 돼서 Set 돼서 1 되고 .. 이런 의미이다.

마지막에 금지된 status 사용해서 다시 Qa가 0이 되는데, 그 다음에 H 될 때 뭔가 문제가 생긴다 !

⭐ 참고로 Qb는 Qa의 inversion 이다.

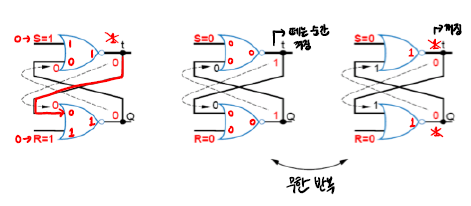

Problem

S=1, R=1 을 넣으면 t와 Q가 0으로 출력된다. 그래서 문제 없는 것처럼 보이지만 ..

그 다음에 S=0, R=0 을 넣었을 때 t와 Q가 둘 다 1로 바뀌어버린다.

이게 되먹임 돼서 t와 Q가 0으로 바뀐다.

또 이게 되먹임 돼서 t가 0에서 1로 바뀌고, Q가 0에서 1로 바뀐다 ... (반복)

😨 이 NOR gate의 delay가 완전히 똑같다면 손을 떼도 두 상태가 무한 반복되어 발진이 될 것이다 !

하지만 회로가 완전히 똑같진 않기 때문에 delay 가 누적돼서 예측할 수 없게 된다. (Out of 통제)