2-1 에러 검출 코드

1. 패리티 비트

에러검사를 위한 추가 비트

짝수 패리티, 홀수 패리티

*원래 무선통신에는 에러가 많이 일어나기 때문에 단일패리티는 현실에서 사용하기 어려움

2. 병렬 패리티

- 패리티 블록데이터에 적용

- 에러 검출 및 정정 가능 (에러 위치 파악 가능)

2-2 게이트

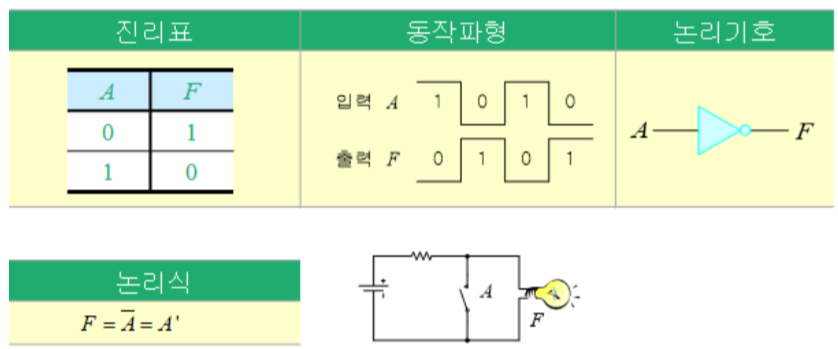

1. NOT 게이트

1입력 1출력

입력 받은 반대 형태 출력

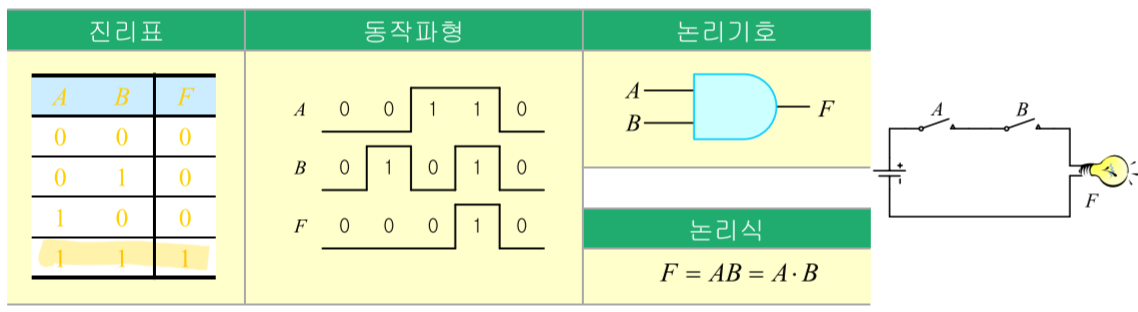

2. AND 게이트

2입력 1출력

입력이 모두 1이면 1출력

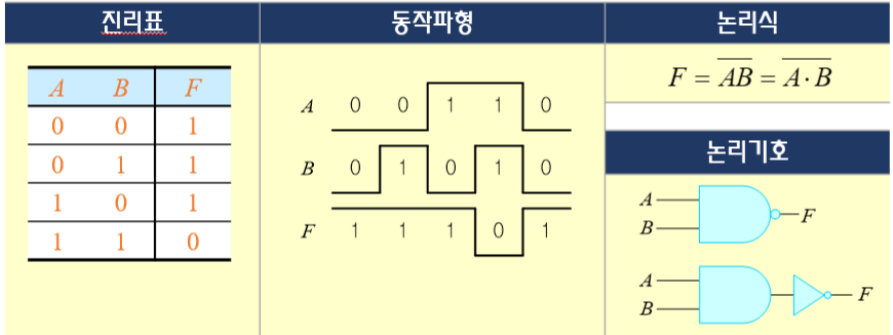

3. NAND 게이트

입력이 모두 1이면 0출력

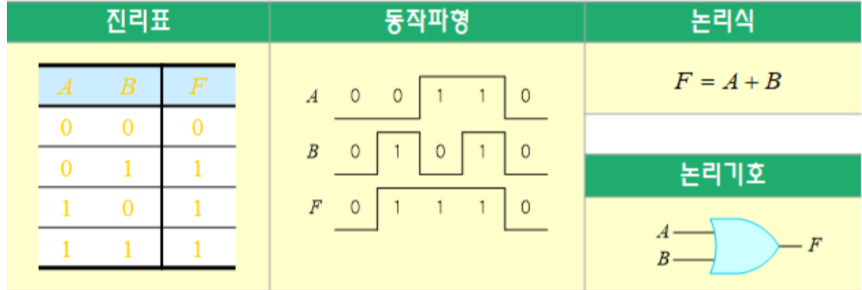

4. OR 게이트

입력이 모두 0이면 0출력

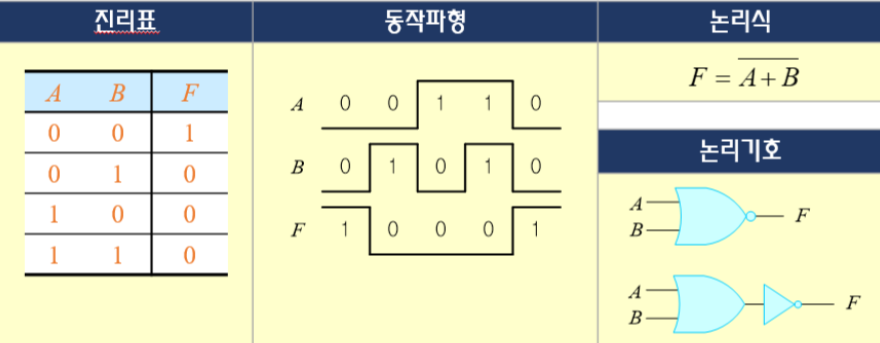

5. NOR 게이트

입력이 모두 0이면 1출력

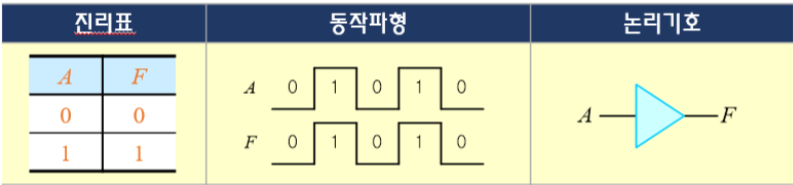

6. 버퍼 게이트

입력된 신호 그대로 출력

3상태버퍼: High, Low, 하이 임피던스

하이 임피던스: 회로가 끊어진 것과 비슷한 효과, 저항을 높게 해 데이터를 받지 못하는 상태

[활용법]

하나의 버스에 여러 장비가 물려 있을 경우, 여러 장비에서 동시에 출력을 내보내면 버스에서 데이터 충돌이 발생하기 때문에

이를 막기 위해 데이터를 내보내야할 장비 외에는 모두 고저항(하이 임피던스)를 걸어 그 순간 버스에 하나의 장비에서 나온 데이터만 흐르게 함

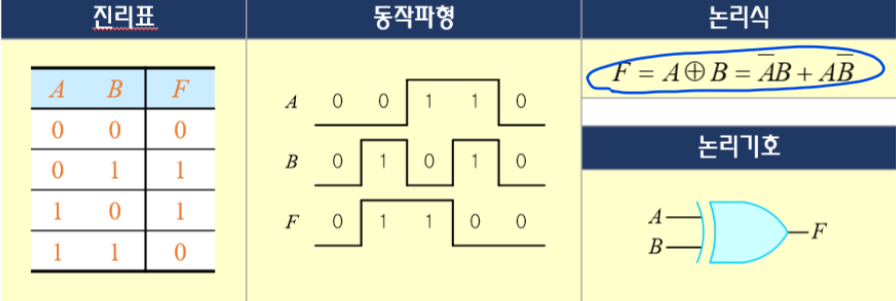

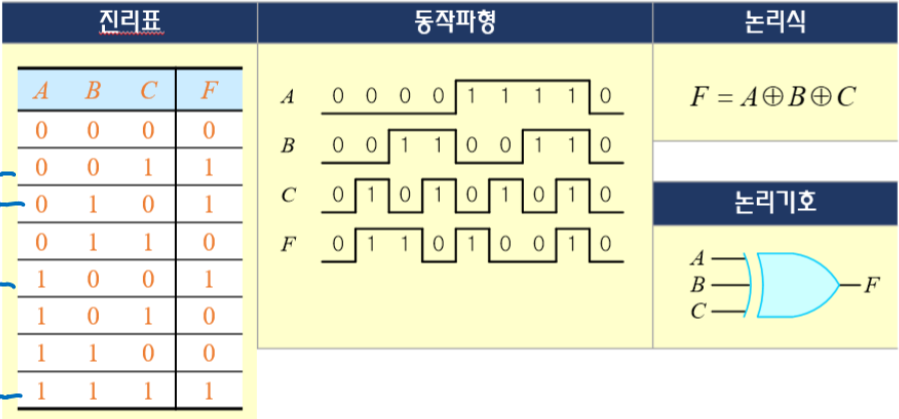

7. XOR 게이트

입력 중 홀수 개의 1이 입력되면 1출력

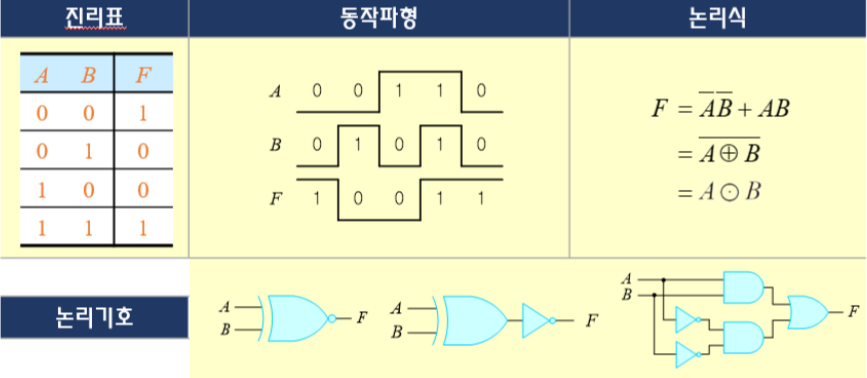

8. XNOR 게이트

입력 중 짝수 개의 1입력되면 1출력

2-3 가산기

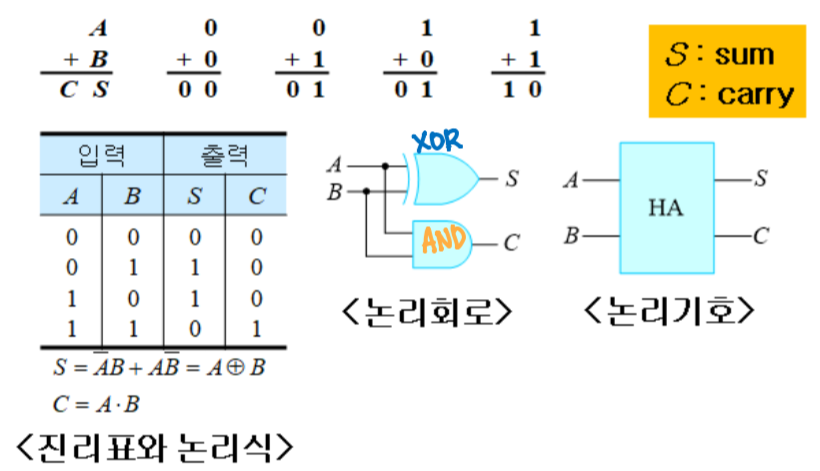

1. 반가산기

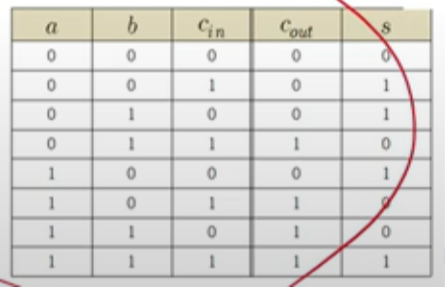

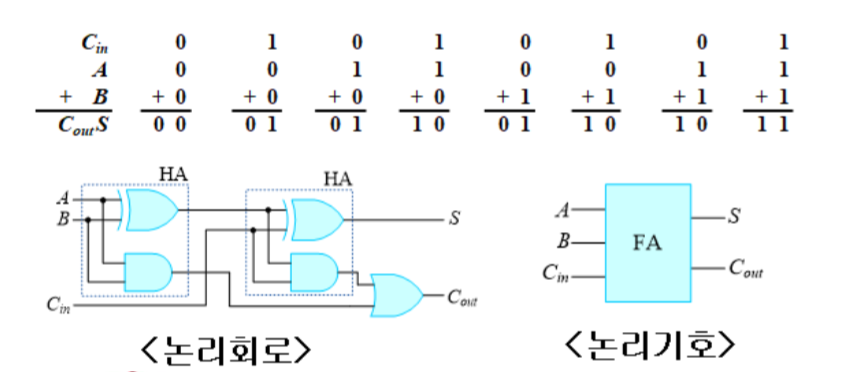

2. 전가산기

Carry 고려

3. 병렬가산기

전가산기 여러 개 병렬로 연결

2-4 감산기

2-5 가감산기

1. 병렬 가감산기

뺄셈: 보수를 이용한 덧셈기능 활용 -> 감산기를 따로 만들지 X

2의 보수 활용

https://life-is-potatoo.tistory.com/19

2-6 플립플롭

1비트 기억소자

- 플립플롭 : 입력이 들어왔을 때, clock 동기신호에 의해 입력 반영

- 래치: 입력이 들어왔을 때, 조건이 맞으면 바로 반영(과거의 데이터가 영향을 줌)