Design Compiler Background

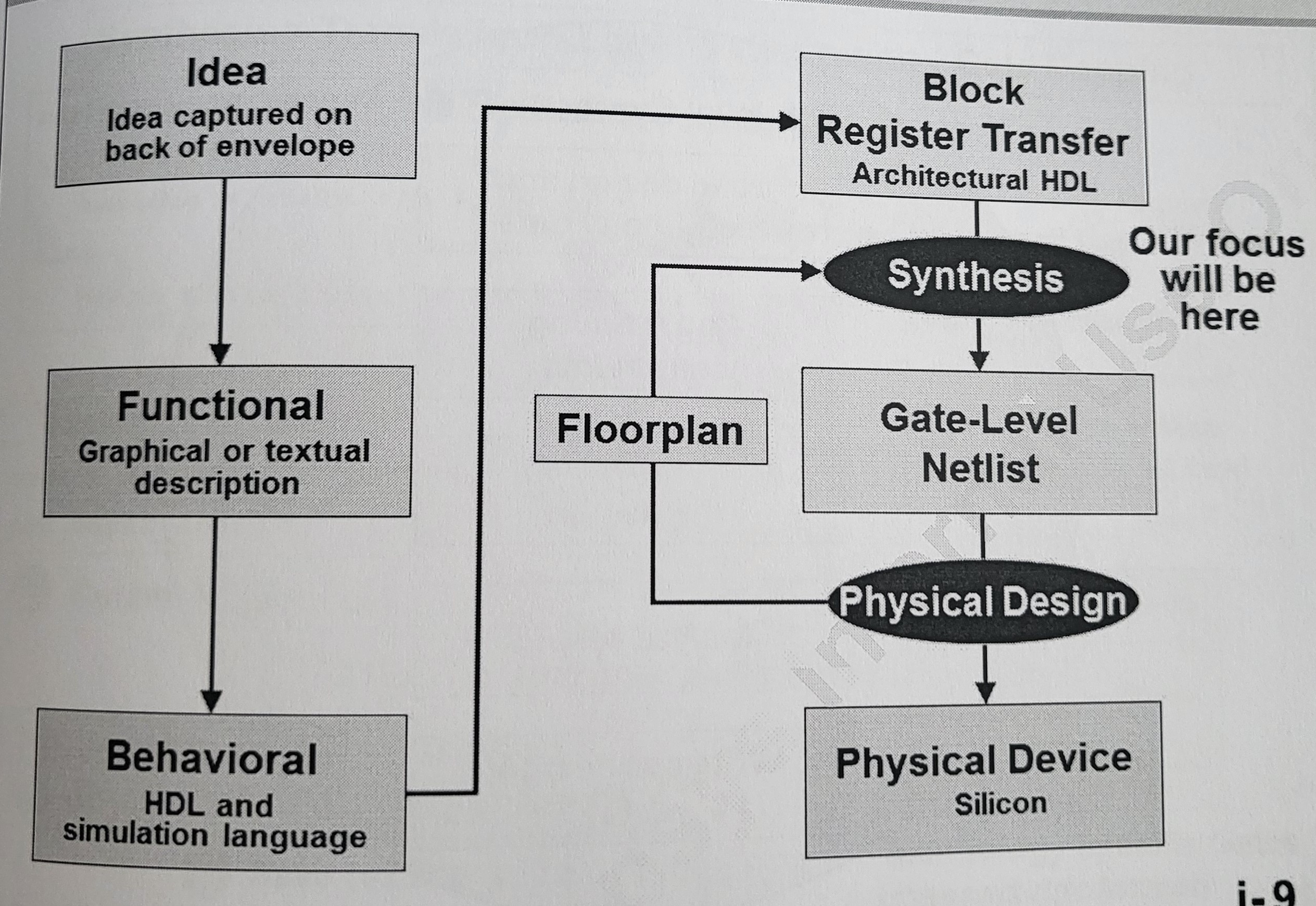

Synthesis

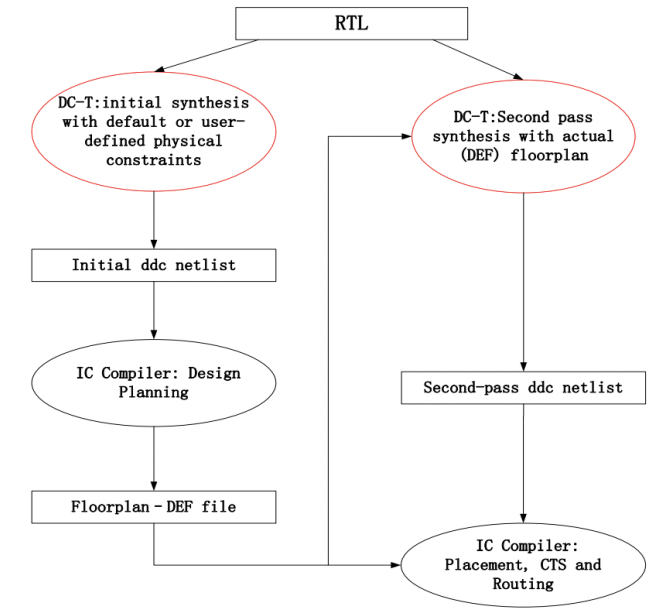

| Synthesis Flow |

|---|

|

PD 팀에서 Floorplan 이후 다시 PI로 보내줌

| Synthesis Transformations |

|---|

|

- DC에 필요한 3가지

- Design(RTL Source)

- Constrain(Timing Constraints)

- Library(Technology-specific Gates)

Timing Constraints는 Optimize 하려면 필수.

-

Translate :

read

RTL Source로 GTECH 만듦 = unmapped ddc format ←read만 하고compile안 한 상태 -

Optimize + Mapping :

compile_ultra

netlist가 생성됨 = mapped ddc format

-

read_vhdl: .vhdl 읽음 -

read_verilog: function을 기술한 verilog -

read_sverilog: test 용 verilog (system verilog)

-

write_icc2_files: icc2용으로 저장

Two Modes for RCs

- WLM(Wire Load Model) mode

Fan Out 기준으로 모든 net delay에 같은 RC 값 계산.

단점 : over- and under-estimated 될 가능성 높음

하지만 어차피 PD에서 Floor Plan 하고 다시 해야하니까 빨리 해야할 때 margin 많이 주고 돌린 다음에 다시 함.

- Topographical mode ← DC_Ultra만 있으면 된다.

dc에서 coarse placement 하여 congestion-aware routing 하고 이를 기반으로 RC 계산- timing과 area가 pre-layout에 비해 좋아진다.

- physical library와 technology file이 필요하다.

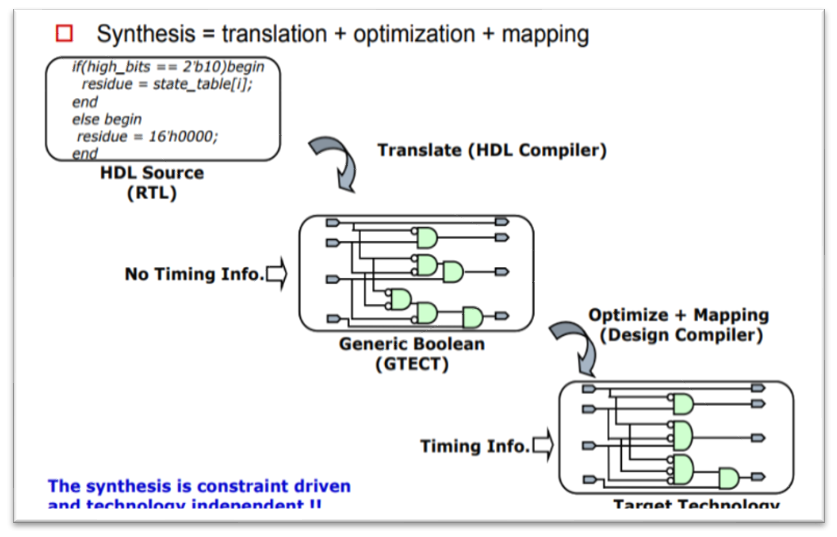

Two-pass Topographical Synthesis Flow

| two-pass synthesis flow |

|---|

|

DC-T : Topographical

DC-G : graphical

SPG = Synopsys physical guidance ← 명령어의 옵션으로 자주 나옴

Design Partitioning

Best Result : top-level design에서 합성하는거

- 단점 : 오래걸림

그래서 partitioning 한다.

DC_Shell commands

- linux-like commands

pwdcdlshistory

- repeat commands

!!!7: 방향키 못 쓰는 환경에서!rep

- linux commands

sh <UNIX_command>get_unix_variable <UNIX_env_variable>