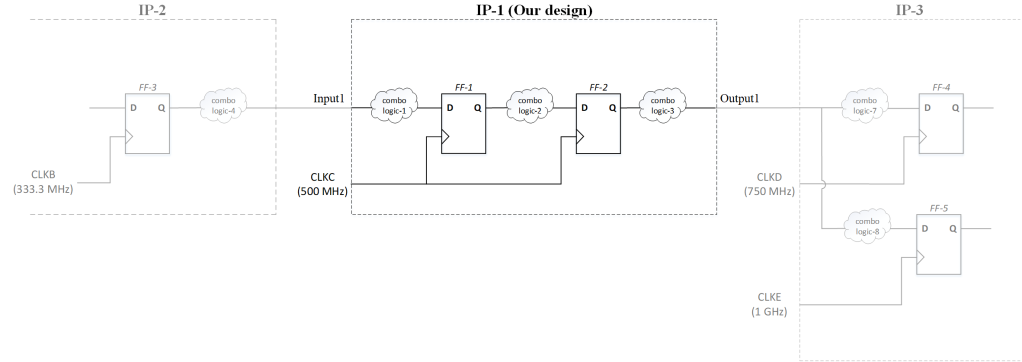

Multiple Synchronous Clocks

Multiple Clock

Input Dealy

| multiple clock input delay |

|---|

|

create_clock -period 2.0 [get_ports CLKC]

create_clock -period 3.0 -name CLKB

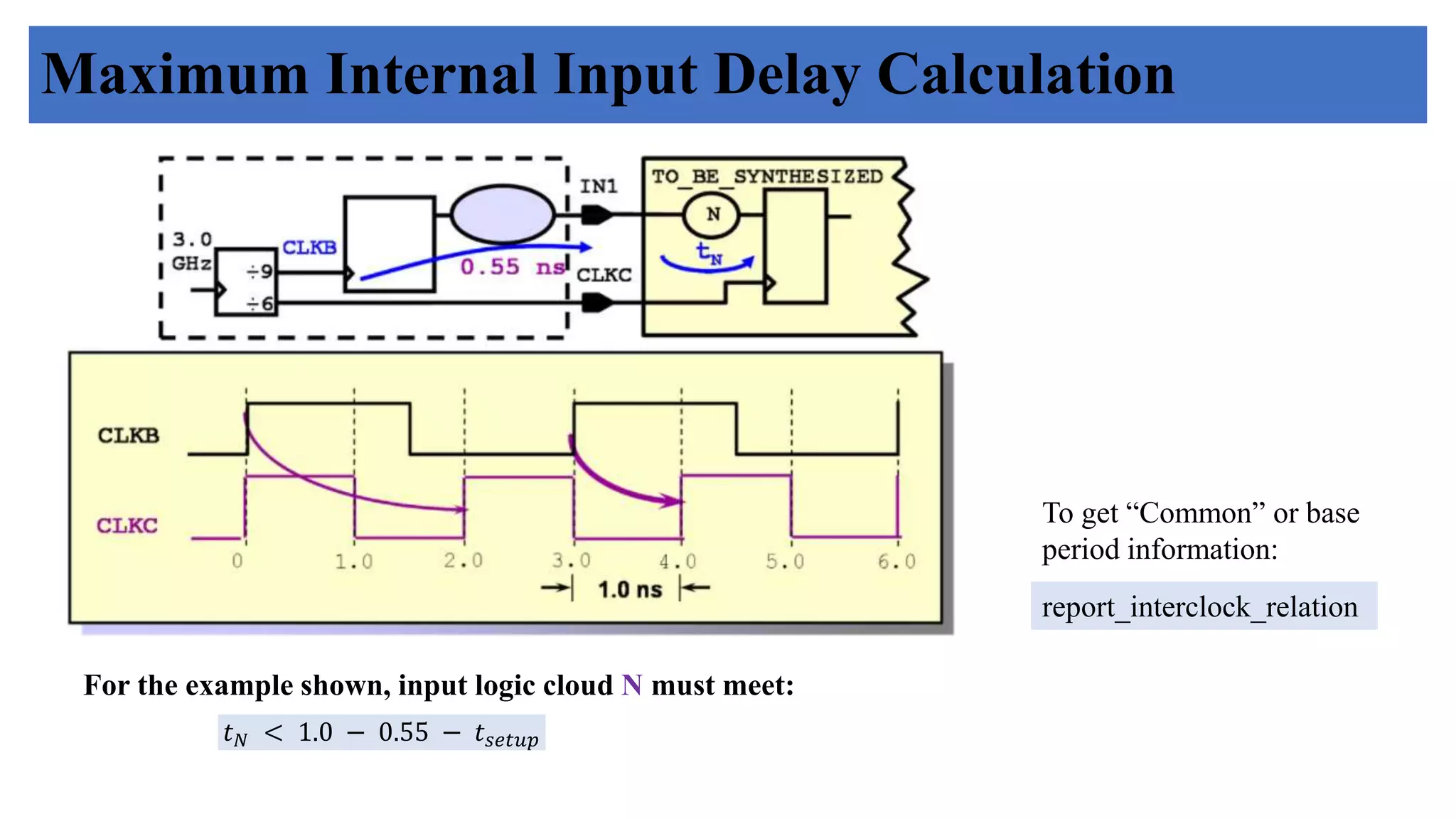

set_input_delay 0.55 -clock CLKB -max [get_ports IN1]Maximum Internal Input Dealy

CLKC은 4ns에서 set, CLKB는 3ns에서 set → 4ns - 3ns = 1ns

report_interclock_relation

같이 set 되는 "common" 시간 확인 가능

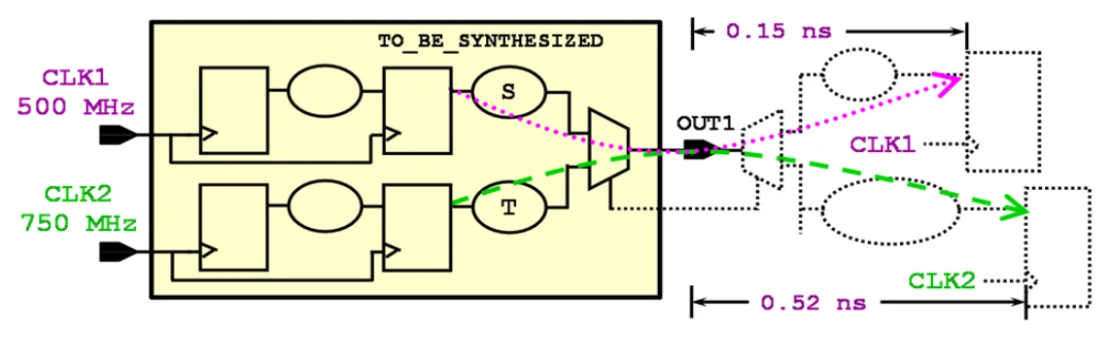

Output Delay

| multiple clock output delay |

|---|

|

create_cloc k-period 2.0 [get_ports CLKC]

create_clock -period 1.0 -name CLKE

create_clock -period [expr {1000/750.0}] -name CLKD

set_output_delay -max .15 -clock CLKD [get_ports OUT1]

set_output_delay -max .52 -clock CLKE -add_Delay [get_ports OUT1]Maximum Internal Output Delay

CLKC는 0ns에서 set, CLKE는 1ns에서 set → 1ns - 0ns = 1ns

CLKC는 2ns에서 set, CLKD는 2.67ns에서 set → 2.67 - 2ns = 0.67ns

Uncertainty

create_clock -period 3 [get_ports Clk1]

create_clock -period 2 [get_ports Clk2]

set_clock_uncertainty -setup 0.10 [get_clocks Clk1]

set_clock_uncertainty -setup 0.18 [get_clocks Clk1]

set_clock_uncertainty -setup 0.15 \

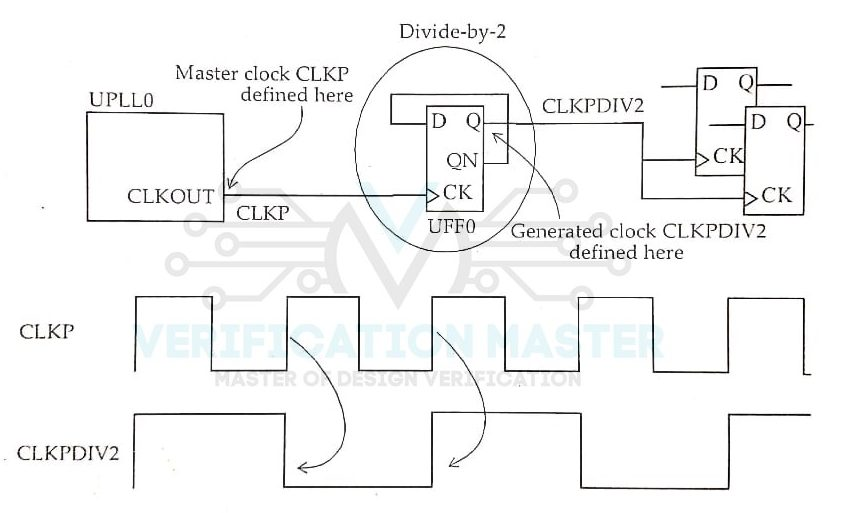

-from [get_clocks Clk1] -to [get_clocks Clk2]Generated Clocks

| 분주회로 |

|---|

|

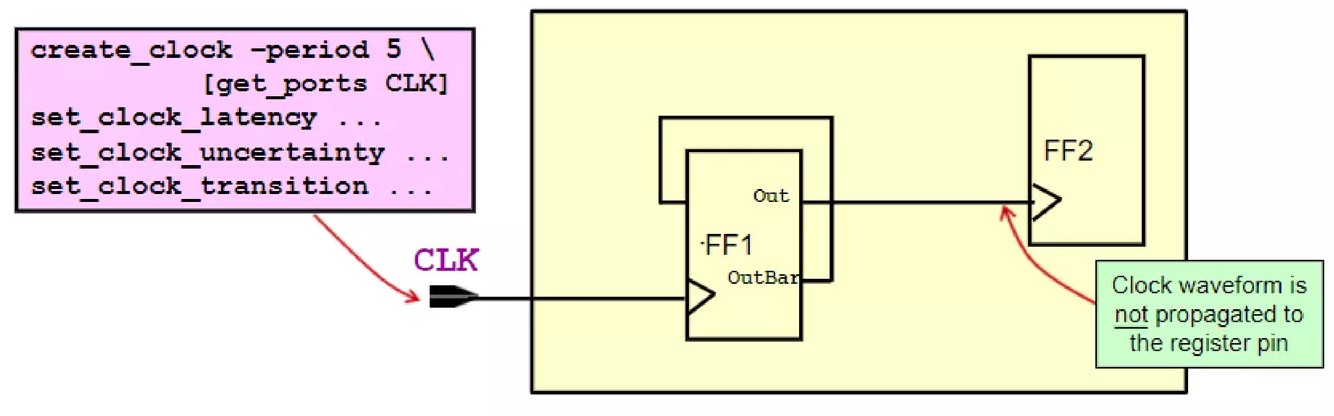

Instatiated Register

| instantiated clock |

|---|

|

create_clock -p 5 [get_ports CLK]

create_generated_clock -devide_by 2 -name CLK_SLW \

-source [get_ports CLK] [get_pins FF1/Out]RTL Register

code로만 있고 instantiated 안되어 있을 때

create_clock -p 5 [get_ports CLK]

create_generated_clock -devide_by 2 -name CLK_SLW \

-source [get_ports CLK] [get_pins DIV_CLK_reg/Q]RTL code 에서 작성된 signal(reg) 이름을 사용

Register cell name : <OUTPUT_SIGNAL_NAME>_reg

Clock pin : clocked_on

Data pin : next_state

Q output pin : Q

Q-bar output pin : QN

Asynch reset : clear

Asynch set : preset

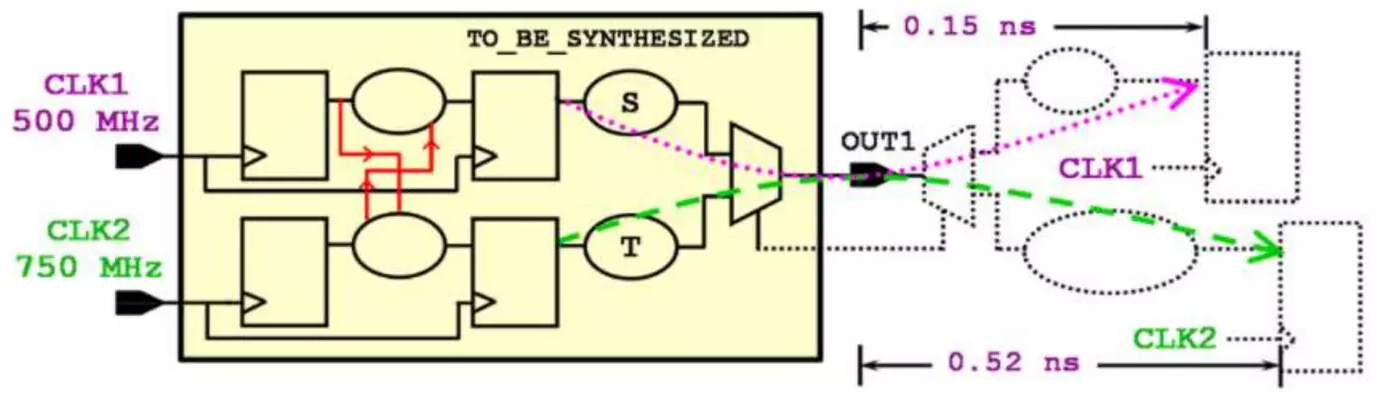

Mutually Exclusive Synchronous Clocks

Logically Exclusive Clocks

| logically exclusive clock #1 |

|---|

|

create_clock -period 2.0 [get_ports CLK1]

create_clock -period [expr {1000/750.0}] [get_ports CLK2]

set_output_delay -max .15 -clock CLK1 [get_ports OUT1]

set_output_delay -max .52 -clock CLK2 -add_delay [get_ports OUT1]

set_false_path -from [get_clocks CLK1] -to [get_clocks CLK2]

set_false_path -from [get_clocks CLK2] -to [get_clocks CLK1]

# OR

set_clock_groups -logically_exclusive -group CLK1 -group CLK2Example #2

| logically exclusive clock #2 |

|---|

|

create_clock -period 2.0 [get_ports CLK1]

create_clock -period [expr {1000/750.0}] [get_ports CLK2]

set_output_delay -max .15 -clock CLK1 [get_ports OUT1]

set_output_delay -max .52 -clock CLK2 -add_delay [get_ports OUT1]

set_false_path -from [get_clocks CLK1] \

-through [get_ports OUT1] -to [get_clocks CLK2]

set_false_path -from [get_clocks CLK2] \

-through [get_ports OUT1] -to [get_clocks CLK1]Example #3

| logically exclusive clock #3 |

|---|

|

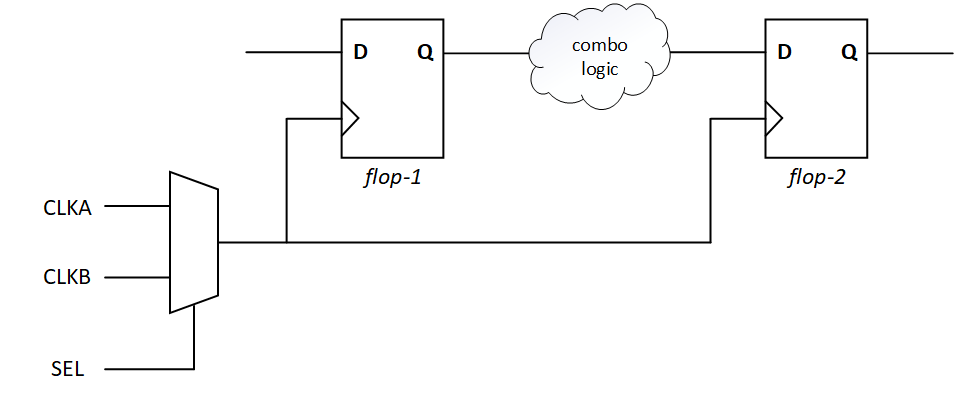

create_clock -p ... [get_ports CLKA]

create_clock -p ... [get_ports CLKB]

set_clock_groups -logically_exclusive -group CLKA -group CLKBExample #4

| logically exclusive clock #4 |

|---|

|

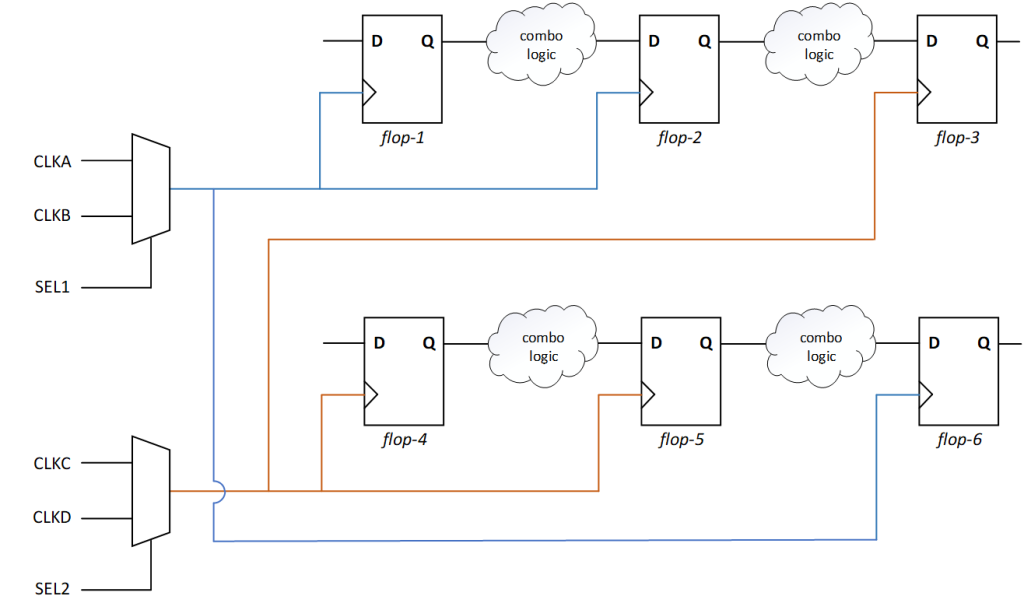

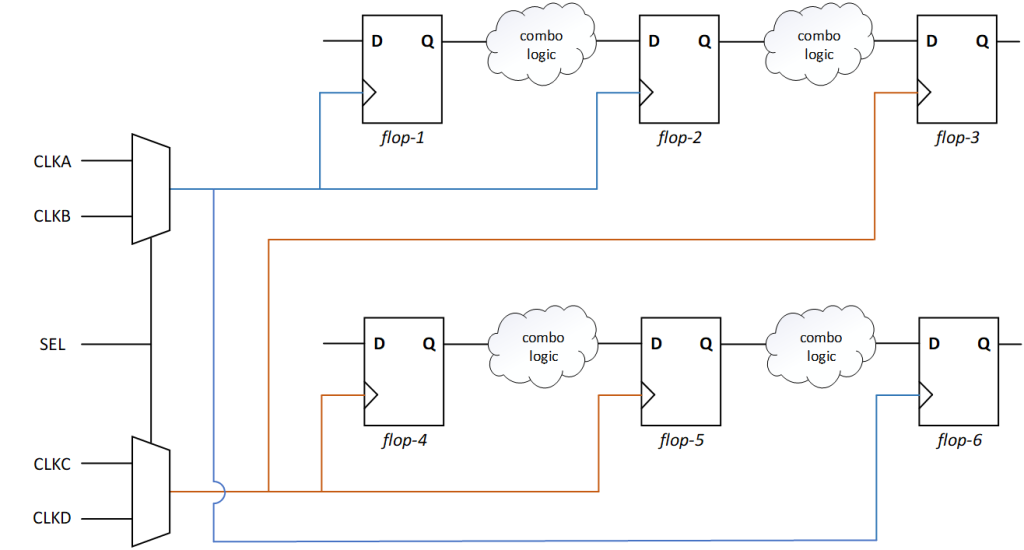

create_clock -p ... [get_ports CLKA]

create_clock -p ... [get_ports CLKB]

create_clock -p ... [get_ports CLKC]

create_clock -p ... [get_ports CLKD]

set_clock_groups -logically_exclusive -group CLKA -group CLKB

set_clock_groups -logically_exclusive -group CLKC -group CLKDExample #5

| logically exclusive clock #5 |

|---|

|

create_clock -p ... [get_ports CLKA]

create_clock -p ... [get_ports CLKB]

create_clock -p ... [get_ports CLKC]

create_clock -p ... [get_ports CLKD]

set_clock_groups -logically_exclusive \

-group "CLKA CLKC" -group "CLKB CLKD"Physically Exclusive

DC에서는 logically나 physically나 똑같이 clock끼리 서로 검사 안함

PT에서 Crosstalk 계산할 때 사용

create_clock -period 3 -name CLK1 [get_ports CLK]

create_clock -period 4 -name CLK2 -add [get_ports CLK]

set_clock_groups -physically_exclusive -group CLK1 - group CLK2Example

| Example |

|---|

|

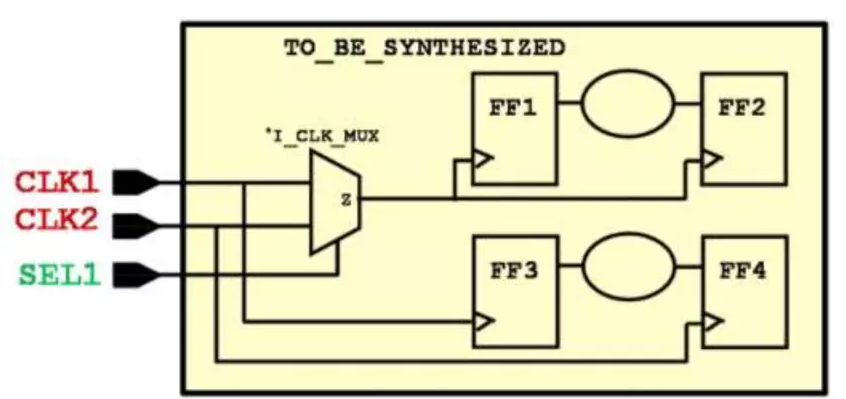

create_clock -period 5 -name FST_CLK [get_ports CLK1]

create_clock -period 8 -name SLW_CLK [get_ports CLK2]

create_generated_clock -devide_by 1 -name MCLK1 \

-source CLK1 [get_pins I_CLK_MUX/Z]

create_generated_clock -devide_by 1 -name MCLK2 -add \

-source CLK2 [get_pins I_CLK_MUX/Z]

set_clock_groups -physically_exclusive -group MCLK1 -group MCLK2Asynchronous Clocks

create_clock -period 3 [get_ports CLKA]

create_clock -period 2 [get_ports CLKB]

set_clock_groups -asynchronous -group CLKA -group CLKBMulti-Cycle Paths

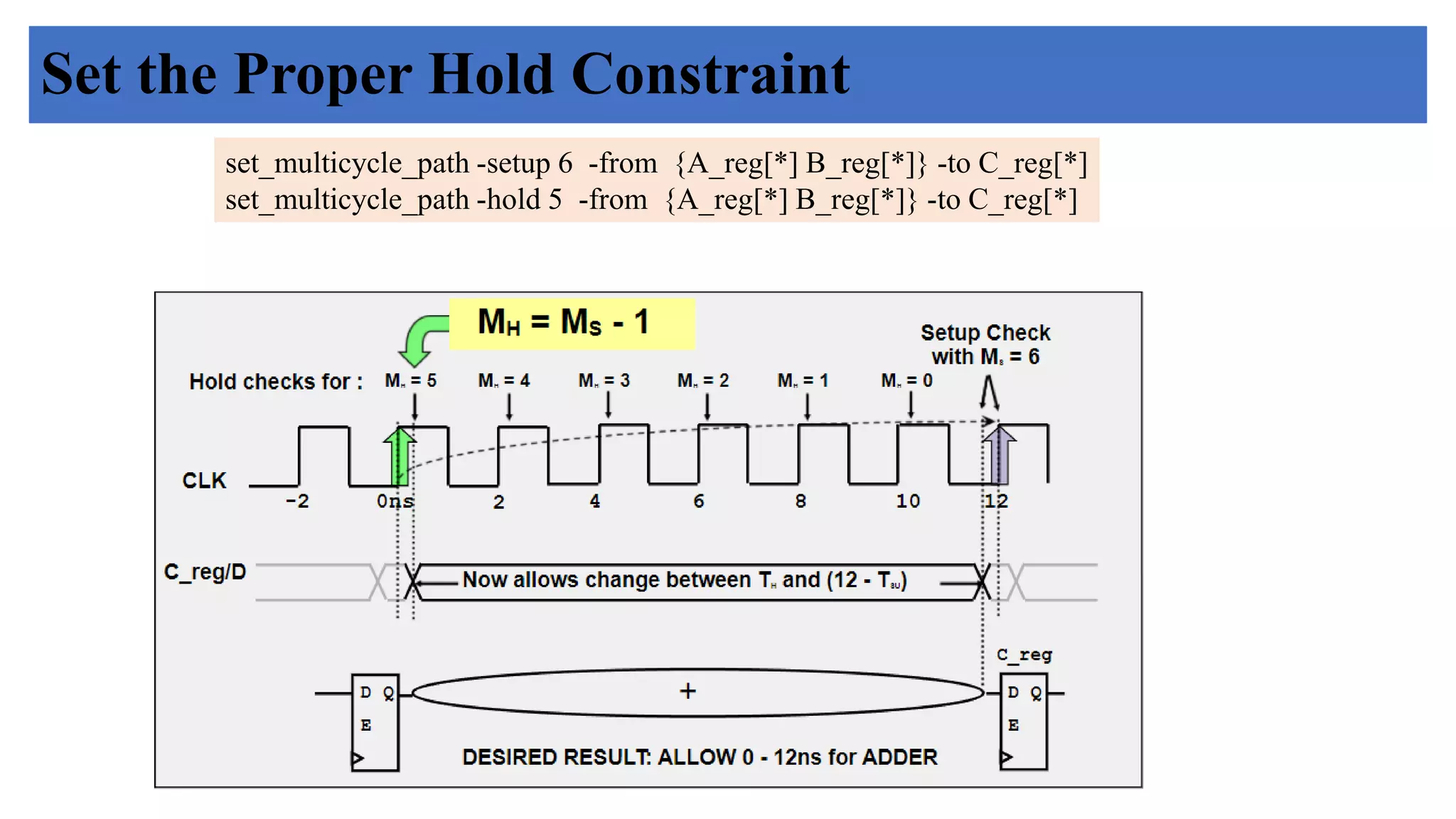

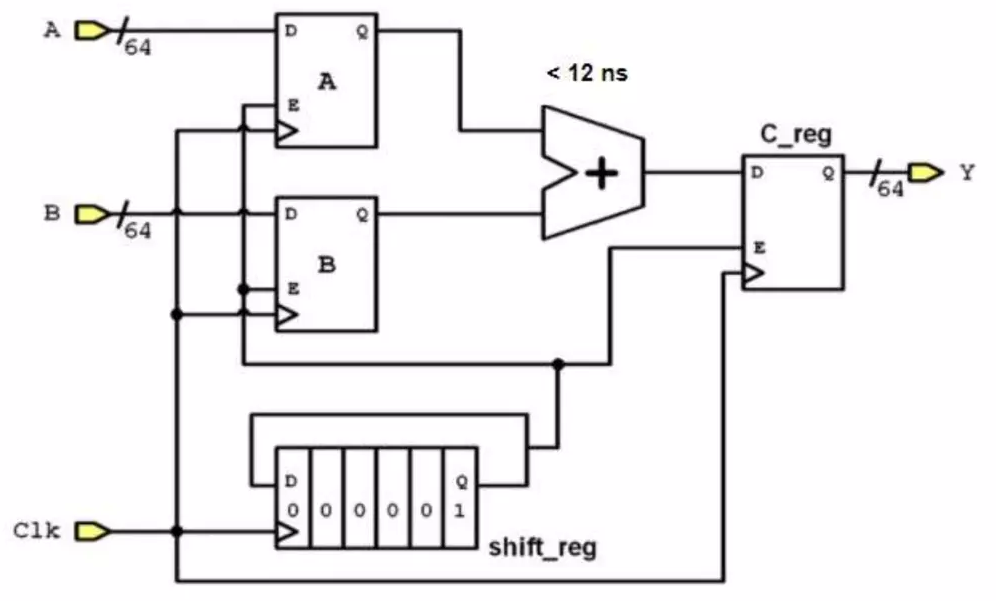

| Multi-cycle Constraints |

|---|

|

create_clock -period 1 [get_ports CLK]

set_multicycle_path -setup 6 -from {A_reg[*] B_reg[*]} -to C_reg[*]

set_multicycle_path -setup 5 -from {A_reg[*] B_reg[*]} -to C_reg[*]

0ns 에서 CLK의 Launch edge, 6ns에서 CLK의 Capture edge 발생

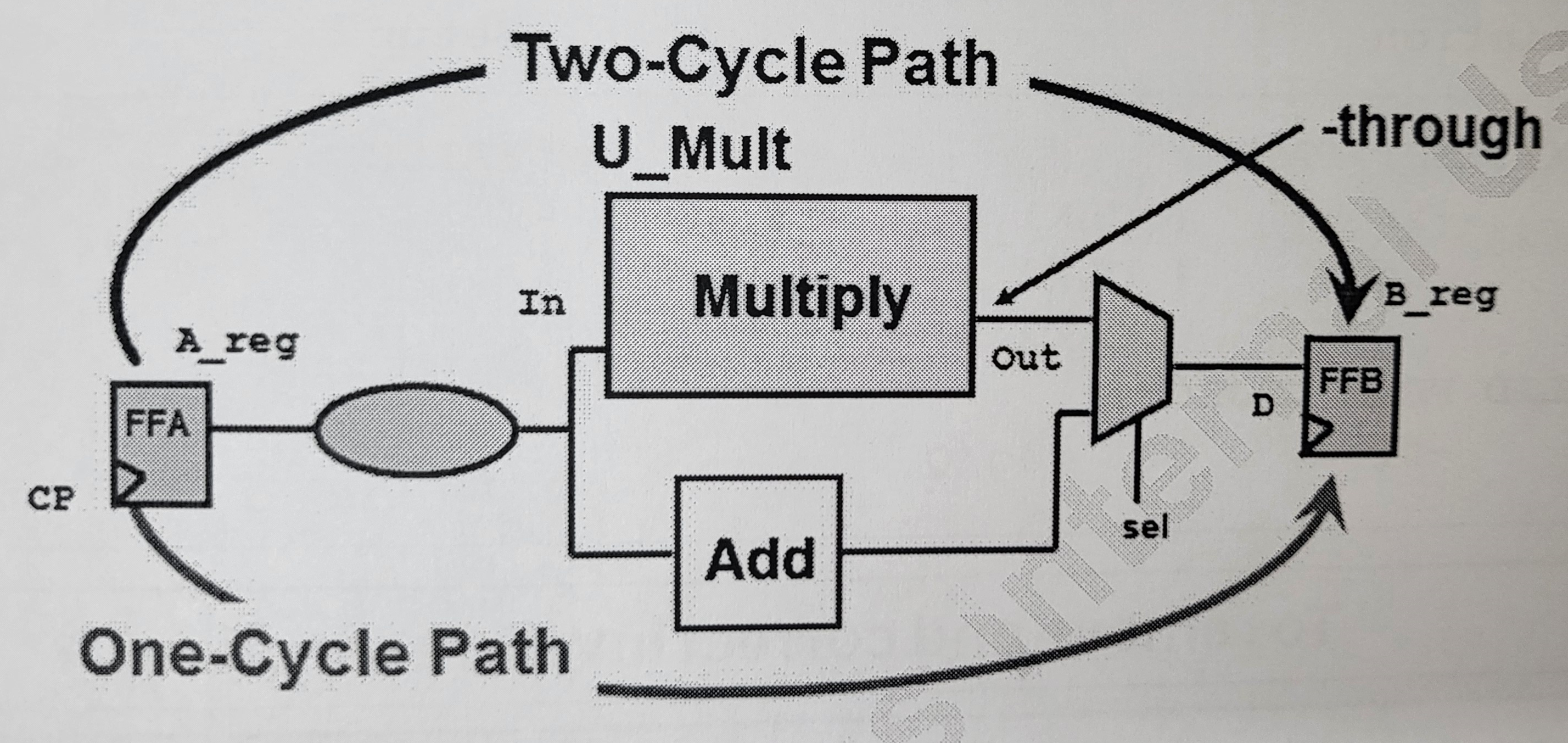

Example

| multi-cycle clock |

|---|

|

set_multicycle_path -setup 2 -through U_Mult/Out

set_multicycle_path -hold 1 -through U_Mult/Out

# OR

set_multicycle_path -setup 2 -from A_reg/clockd_on \

-through U_Mult/Out -to B_reg/next_state

set_multicycle_path -hold 1 -from A_reg/clockd_on \

-through U_Mult/Out -to B_reg/next_state