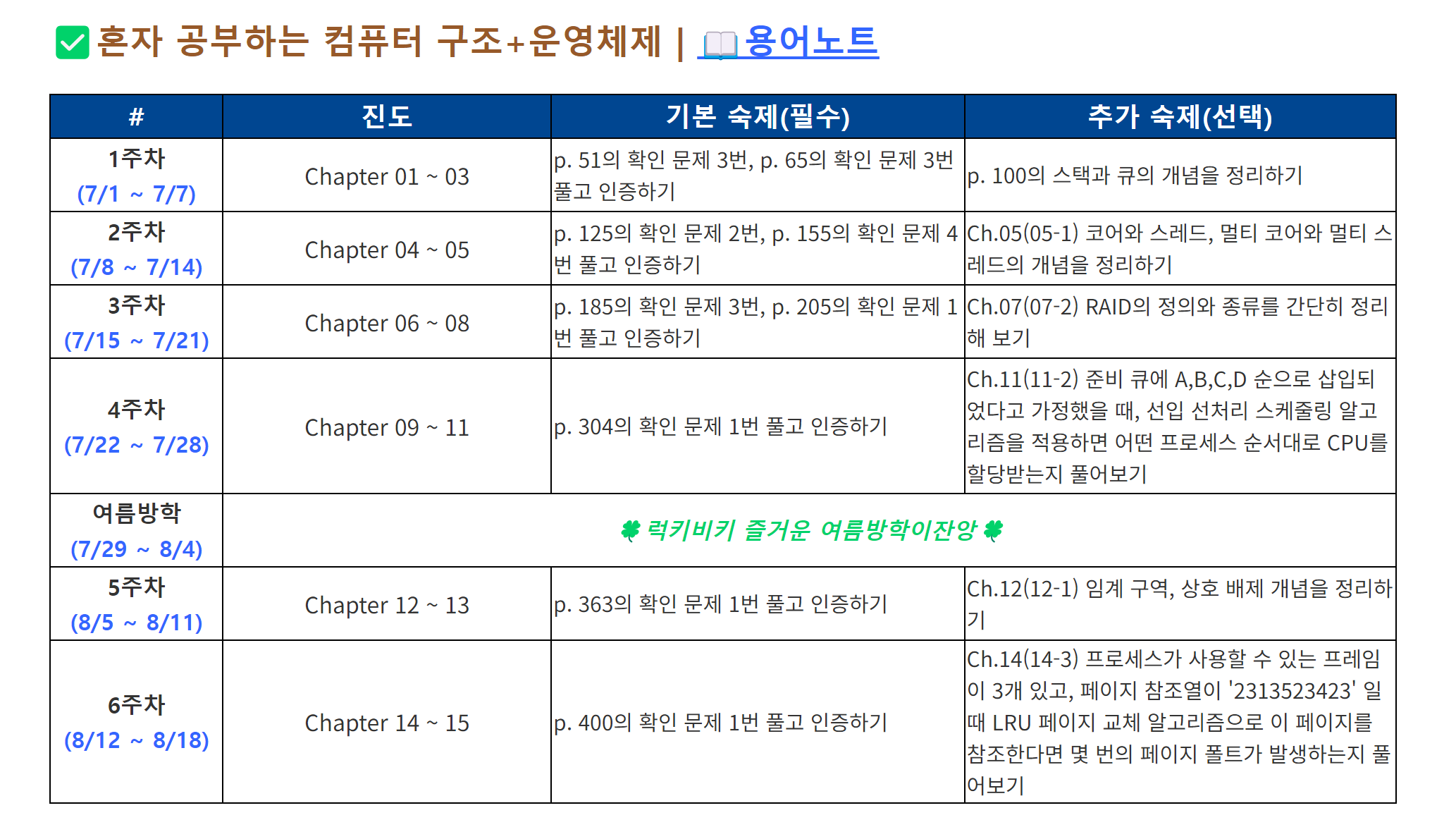

Ch04. CPU의 작동 원리

CPU 구성 요소

-

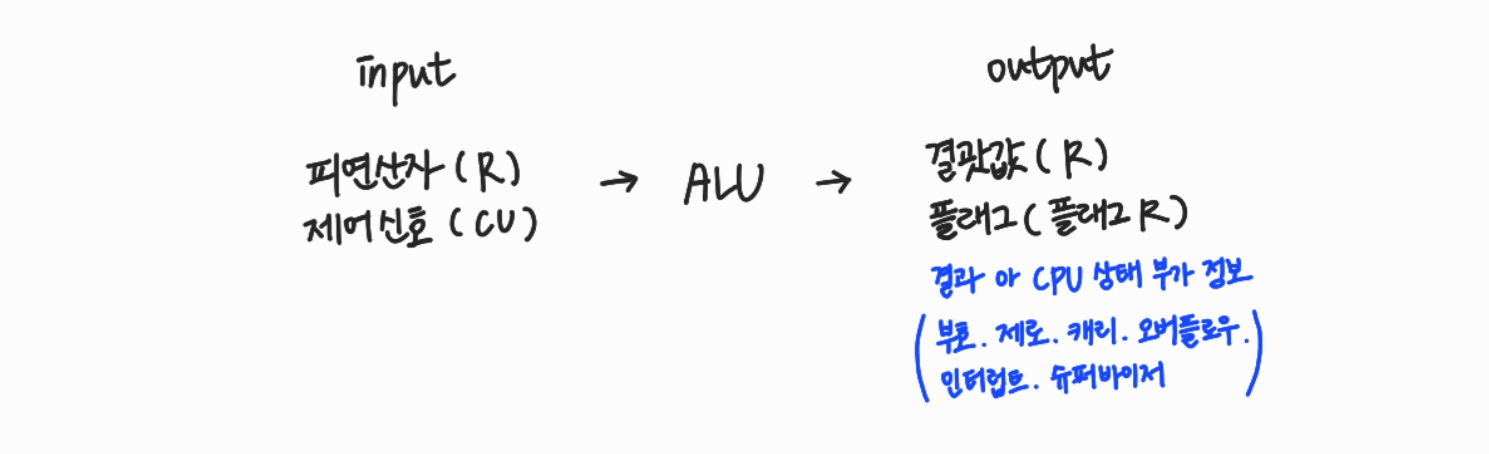

ALU

-

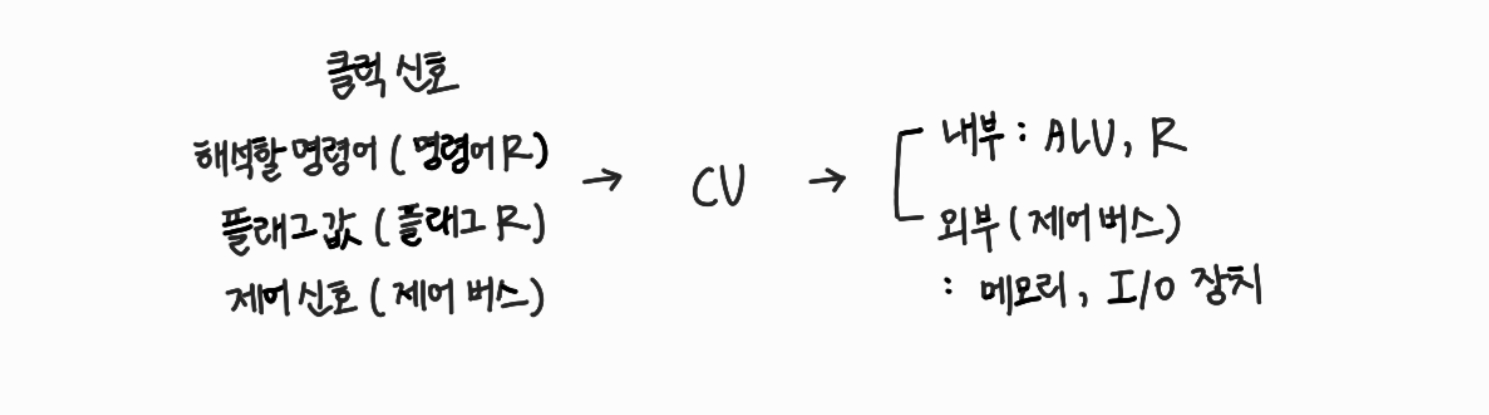

제어장치(CU)

-

레지스터: 임시 저장 장치

- 프로그램 카운터(PC): 메모리에서 읽어올 명령어의 주소 저장

- 명령어 레지스터(IR): 방금 읽은 명령어 저장

- 메모리 주소 레지스터(MAR): 메모리 주소 저장

- 메모리 버퍼 레지스터(MBR): 메모리와 주고 받을 데이터 저장

- 범용 레지스터: 데이터, 주소 모두 저장 가능

- 플래그 레지스터: 연산 결과나 CPU 상태 부가 정보 저장

- 스택 포인터: 스택의 최상단(top)을 가리키는 포인터 (* 스택: 메모리 안 스택 영역)

- 베이스 레지스터: 기준이 되는 주소

주소 지정 방식

- 스택 주소 지정 방식: 스택과 스택 포인터 이용

- 변위 주소 지정 방식: 오퍼랜드 필드 값(변위) + 레지스터 값 => 유효 주소

- 상대 주소 지정 방식: 오퍼랜드 + PC 값

- 베이스 레지스터 주소 지정 방식: 오퍼랜드 + 베이스 레지스터 값

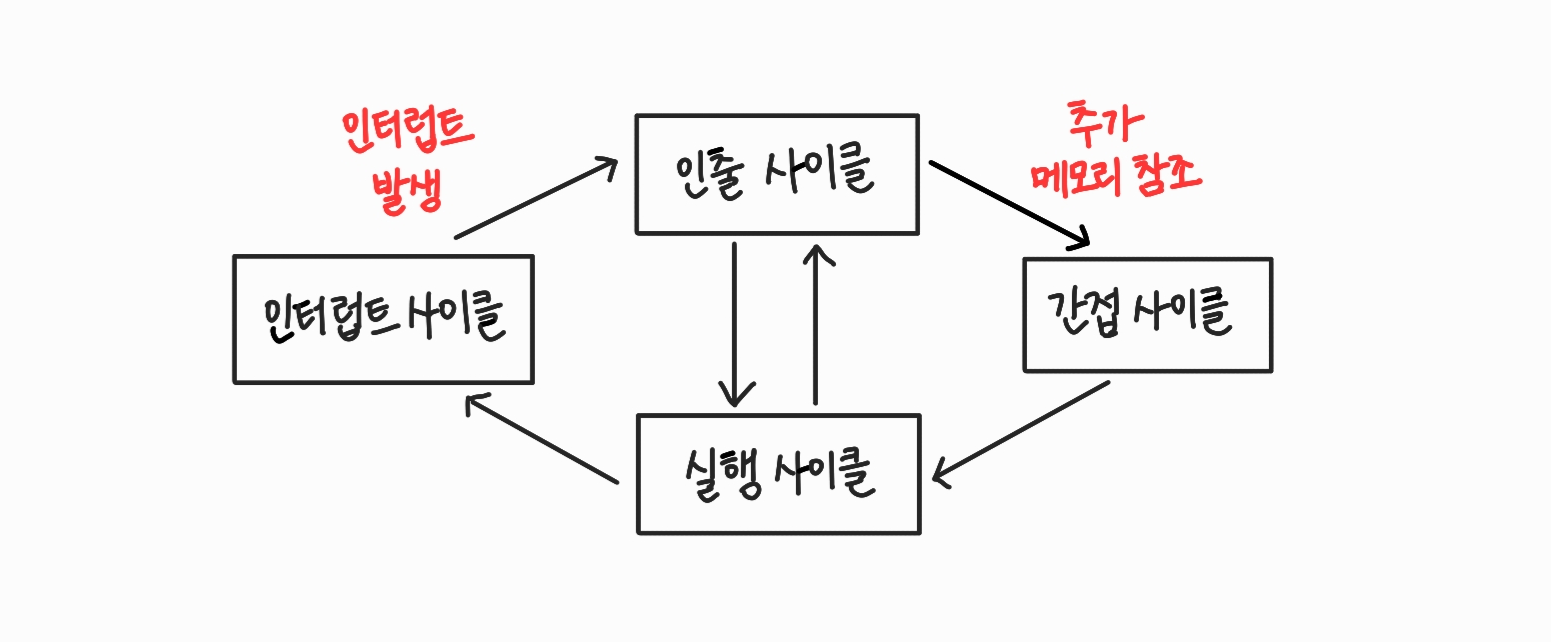

명령어 사이클

하나의 명령어 처리 과정

1. 인출(Fetch): 메모리에 있는 명령어를 CPU로 가져오는 단계

2. 간접(Indirect): 간접 주소 지정 방식을 사용하는 명령어의 경우, 실제 데이터를 얻기 위해 추가 메모리 참조 수행

3. 실행(Execution): CPU로 가져온 명령어 실행하는 단계

4. 인터럽트(Interrupt): 인터럽트를 처리하는 단계

인터럽트

CPU 작업을 방해하는 신호

- 동기 인터럽트: CPU에 의해 발생. ex) 오류 등 => 예외(execption)

- 비동기 인터럽트: 주로 I/O 장치에 의해 발생. ex) 입력 알림, 입출력 완료 알림

Ch05. CPU 성능 향상 기법

클럭 속도

명령어 사이클 내의 각 단계는 클럭 신호에 맞추어 진행되므로, 클럭 속도가 높을수록 주기가 짧아져 빠르게 명령어를 처리할 수 있음.

클럭 속도는 헤르츠(Hz) 단위로 측정. (1초에 몇 번 반복되는지)

ex) 2.5GHz => 1초에 클럭이 2.5 * 10^9번 반복

코어와 멀티코어

코어(core): 명령어를 실행하는 하드웨어 모듈

멀티코어 프로세서: 여러 개의 코어들을 하나의 PCU에 포함시킨 프로세서

각 코어는 독립적으로 작업을 처리할 수 있음.

| 코어 수 | 프로세서 명칭 |

|---|---|

| 1 | 싱글코어 |

| 2 | 듀얼코어 |

| 3 | 트리플코어 |

| 4 | 쿼드코어 |

| 6 | 헥사코어 |

| 8 | 옥타코어 |

코어 수에 비례하여 속도가 증가하지 않음. 코어들에 작업이 적절히 분배되는 것이 중요.

스레드와 멀티스레드

스레드(thread): 하나의 코어가 동시에 처리하는 명령어 단위 (하드웨어적 스레드)

독립적으로 실행되는 최소 크기의 프로그램 단위 (소프트웨어적 스레드)

멀티스레드 프로세서: 하나의 코어로 여러 개의 명령어를 동시에 처리하는 프로세서

각 스레드가 독립적으로 실행될 수 있도록 여러 레지스터 세트를 보유함.

하이퍼스레딩: 인텔의 멀티스레딩 기술

명령어 병렬 처리 기법

- 명령어 파이프라이닝: 명령어 처리 과정을 클럭 단위로 나누어 병렬로 처리하는 기술

- 명령어 인출(fetch) - 명령어 해독(decode) - 명령어 실행(execute) - 결과 저장(store)

- 파이프라인의 각 단계는 독립적으로 수행될 수 있음.

- 슈퍼스칼라: 여러 개의 파이프라인 구조

- 비순차적 명령어 처리: 순서가 바뀌어도 무방한 명령어를 먼저 실행하여 파이프라인이 멈추는 것을 방지하는 기법. 순차적으로 실행하지 않는 기법.

CISC와 RISC

명령어 집합 구조(ISA; Instruction Set Architecture): CPU가 이해할 수 있는 명령어들의 모음

CPU마다 ISA는 다를 수 있음.

CISC

CISC (Complex Instruction Set Computer) ex) x86, x86-4

- 복잡하고 다양한 명령어

- 가변 길이 명령어

- 다양한 주소 지정 방식

- 조건 분기가 많아 파이프라인에 비효율적임

- 메모리 접근이 빈번함

-> (개선안) 단순한 명령어를 빠르게 수행하며, 메모리 접근을 최소화하는 구조

RISC

RISC (Reduced Instruction Set Computer) ex) ARM

- 단순하고 적은 명령어

- 고정 길이 명령어

- 클럭 사이클당 하나의 명령어 실행 -> 파이프라인에 최적화

- 단순한 주소지정 방식 -> 메모리 접근 단순화, 최소화

- 레지스터 적극 활용 -> 범용 레지스터 많음

기본 숙제

p.125 확인 문제 2번

플래그 레지스터: 연산 결과 혹은 CPU 상태에 대한 부가 정보를 저장하는 레지스터

명령어 레지스터: 메모리에서 가져올 명령어의 주소를 저장하는 레지스터

범용 레지스터: 데이터와 주소 모두 저장할 수 있는 레지스터

프로그램 카운터: 해석할 명령어를 저장하는 레지스터

p.155 확인 문제 4번

코어