27. 다중 단계 페이징

다중 단계 페이징 시스템

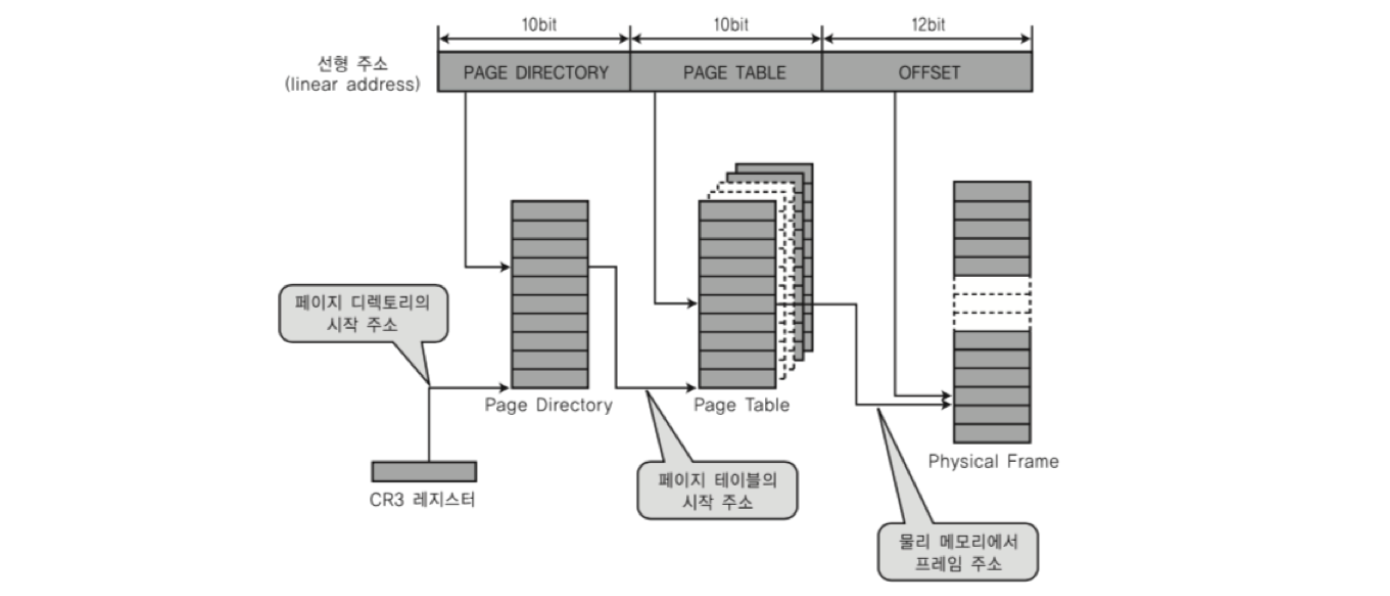

32bit 시스템에서 4KB 페이지를 위한 페이징 시스템은 하위 12bit는 오프셋이며 상위 20bit가 페이징 번호이므로 2의 20승 개의 페이지 정보가 필요하다.

이 때 페이지 정보를 단계를 나누어 생성하면 필요없는 페이지는 없애고 공간 절약이 가능하다.

다중 단계 페이징 시스템 구조

페이지 번호를 나타내는 bit를 구분해 단계를 나눈다. (리눅스 기준, 최근 4단계)

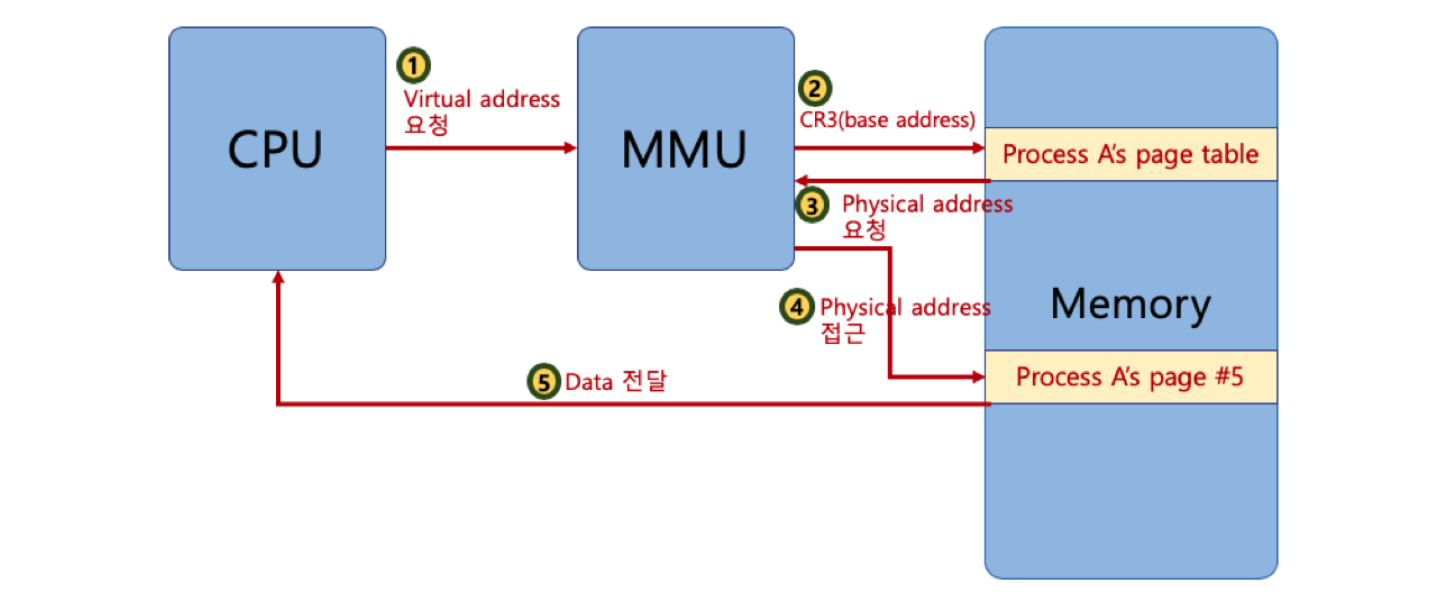

MMU와 TLB

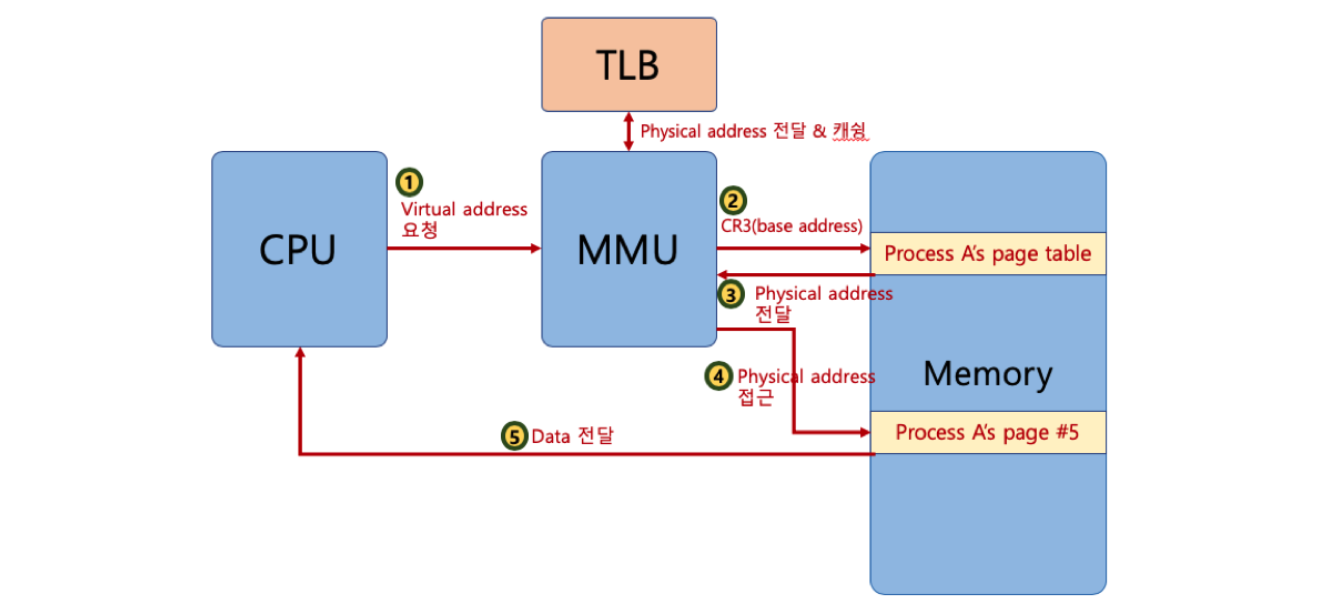

MMU가 물리주소를 확인하기 위해 메모리를 거쳐야 한다. 하지만 레지스터나 캐시에 비해 메모리를 거치는 것이 더 많은 시간을 소요하기에 TLB가 등장하였다.

TLB는 Translation Lookaside Buffer로 페이지 정보 캐시라고 한다. 다음과 같이 MMU에 TLB가 위치하고 있으며 기존의 2, 3번 동작과 같이 가상/물리 주소에 대한 정보를 습득하게 되면 이를 TLB에 저장하여 추후 활용한다.

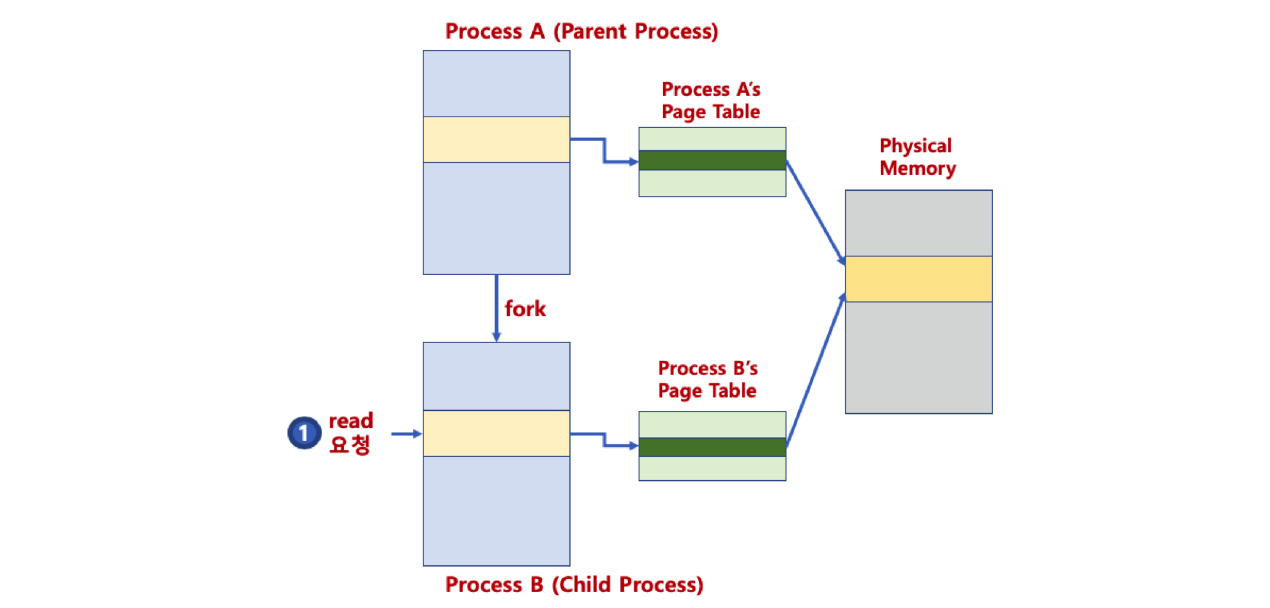

페이징 시스템과 공유 메모리

페이지 테이블에서 프로세스 간 동일한 물리 주소를 가리킬 수 있으며 이를 통해 공간 및 시간을 절약할 수 있다. 다음과 같이 부모 프로세스로부터 fork()하여 자식 프로세스를 생성할 때 페이지 테이블의 내용이 동일한 물리 주소를 가리켜 복사하는데 크게 시간 절약하는 모습이다.

안녕하세요. 패스트캠퍼스 입니다.

패스트캠퍼스에서 유료로 판매중인 영상 내용을 허락없이 블로그에 게제하는 행위는 저작권법이 위배됩니다. 금주까지 관련 블로그를 모두 삭제하지 않을시에, 법적인 조치를 진행하도록 하겠습니다. 확인부탁드립니다.