08. 조합/기억 논리회로

조합논리 회로

조합회로는 입력과 출력을 가진 논리 게이트의 집합으로 출력은 현재의 입력(0, 1)과 조합의 합수이며 순차 논리회로는 게이트 뿐 아니라 기억능력이 있는 플립플롭(Flip-Flop)으로 구성된다.

조합회로 설계 절차

- 문제 제시

- 입력/출력 변수에 문자 기호 할당

- 입력/출력 사이 관계 정의 진리표 유도

- 각 출력에 대한 간소화된 부울 함수 도출

- 논리도 작성

대표적 조합회로

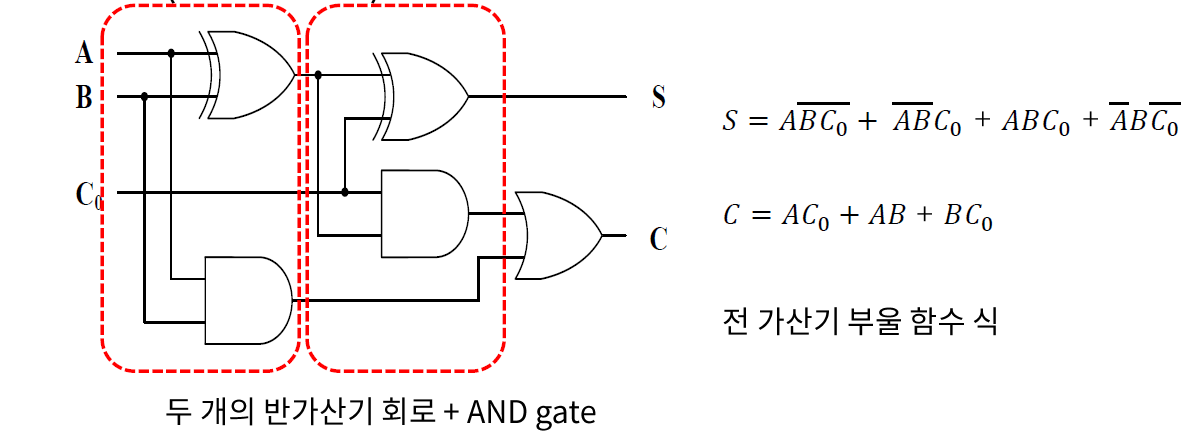

Adder

가산기는 대표적인 조합회로이며 두 개(혹은 그 이상)의 입력을 받아 결과물을 출력하는 조합논리회로이다. 반 가산기(Half Adder)와 전 가산기(Full Adder)로 나눈다.

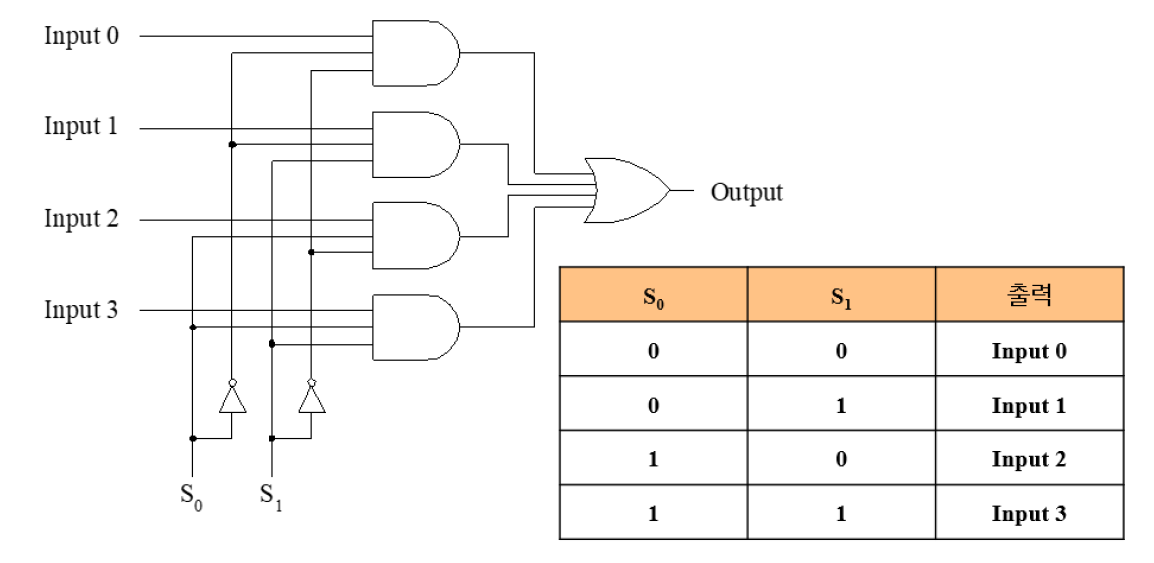

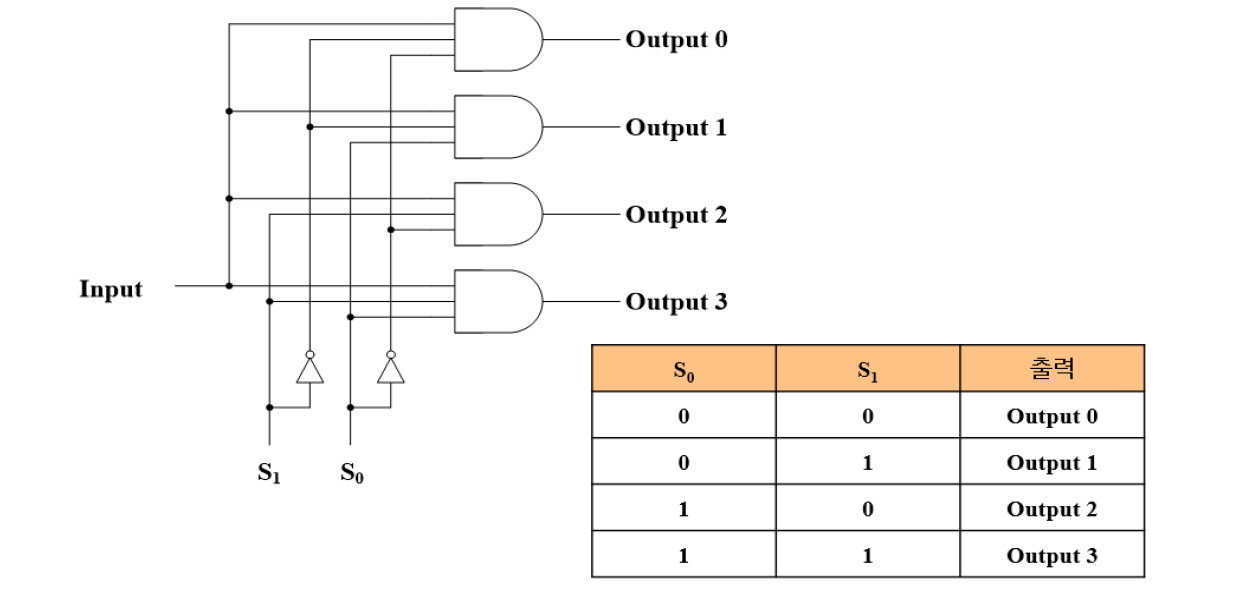

Multiplexer

멀티플렉서는 다수의 입력 중 하나만을 선별적으로 출력하도록 하는 조합논리회로이다.

Demultiplexer

디멀티플렉서는 하나의 입력을 통해 다수의 출력으로 분해하는 기능의 조합회로이다. 예를 들면 10진수를 2진수로 분해하는 것이 해당된다.

기억회로

기억회로의 구성 및 작동원리

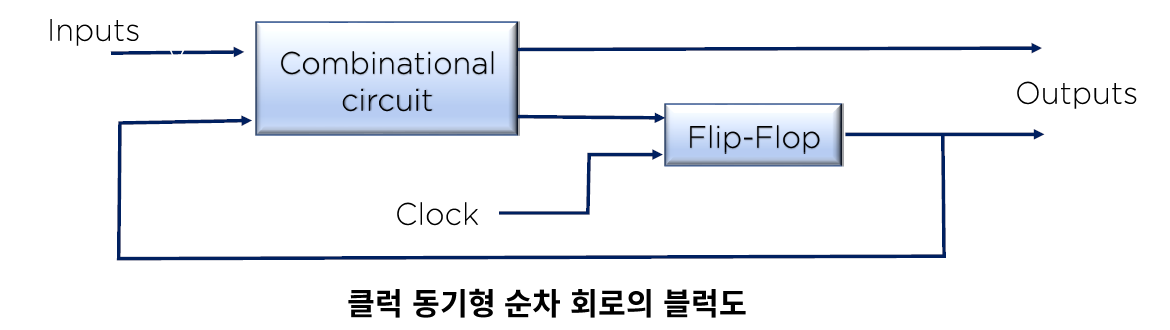

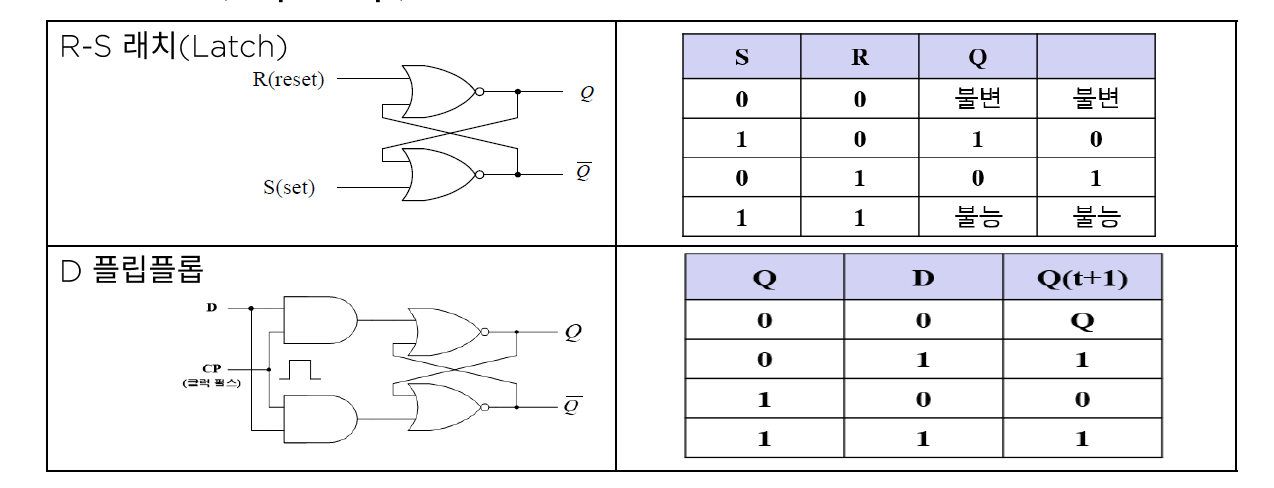

대부분의 디지털 시스템들이 조합회로를 가지고 있지만 순차회로로 구현되는 저장요소를 필요로 한다. 이러한 종류의 회로를 플립플롭이라고 한다.

Flip-Flop의 종류

순차회로

순차회로는 플립플롭과 게이트를 연겨한 것이다. 게이트들로만 이루어진 회로는 조합회로이지만 플립플롭이 포함되면 순차회로가 된다.

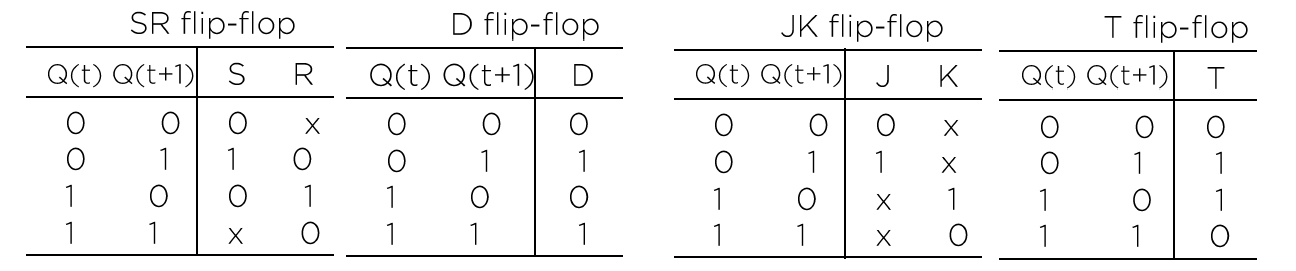

네가지 플립플롭에 대한 표

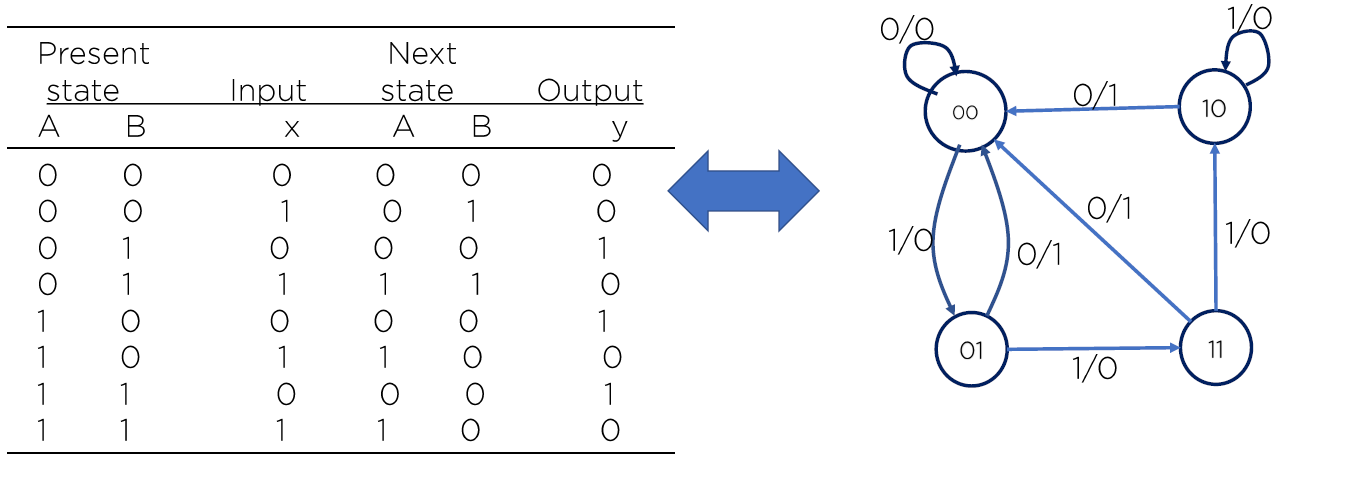

순차회로의 상태표와 상태도

순차회로의 특성은 입력/출력 및 플립플롭의 상태로부터 특정지어진다. 출력과 다음 상태는 모두 입력과 현 상태의 함수이다. 이 사이의 관계를 상태표라하며 상태표를 그림으로 도시한 것이 상태도이다.