24. 입출력 연결과 주소 지정

입출력 주소 지정

입출력 주소 지정

컴퓨터 시스템에는 다양한 입출력 장치 및 통신 포트 등이 연결되며 원칙적으로는 개별적으로 고유한 주소가 할당되나 I/O 장치에 대해서는 용도에 따라 다수의 주소 할당이 가능하다.

- Memory mapped I/O : 메모리에 부여된 주소 공간의 일부를 입출력 주소 공간으로 활용

- I/O mapped I/O : 독립된 메모리 주소 공간과 입출력 주소 공간을 구분하여 할당

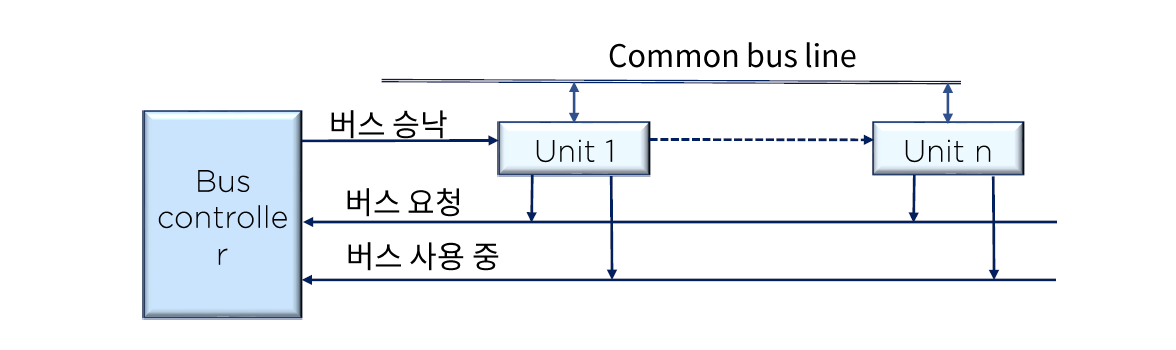

입출력 버스 할당

중앙 제어 버스 vs 분산 제어 버스

중앙 제어 버스 시스템

구현 및 관리가 용이 하나 제어기의 이상 발생 시 버스 중재 및 활용에 결함 발생

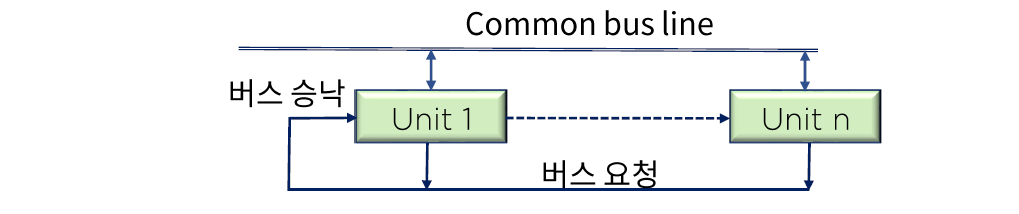

분산 제어 버스 시스템

버스 상의 모든 장치가 제어 기능을 나누어 실행

I/O 버스는 주로 중앙 제어 버스 시스템을 적용하며 시스템 버스는 분산 제어 방식을 선호

동적 중재 알고리즘

정적 우선 순위 알고리즘에 대해 시스템이 동작하고 있는 동안 장치들의 우선 순위를 변경 시킬 필요가 있을 경우 적용 가능한 알고리즘을 동적 우선 순위 알고리즘이라 한다.

- Time slice algorithm

- 연속적으로 주어지는 버스 시간을 고정된 길이의 시간 분할로 나누고 이를 round-robin 방식으로 각 프로세스에 할당, 버스에서의 위치에 관계없이 모든 요소들이 동등한 서비스 받음

- Polling

- 폴 라인으로 버스 승인 신호를 대체하여 모든 장치에 연결

- Least recently used algorithm

- 가장 오랫동안 버스 서비스를 사용하지 못한 장치에게 우선권 부여

- 모든 프로세스가 버스에 접근할 수 있는 기회를 동등하게 부여 받음

- First-com & first-serve

- 버스 제어기는 각 프로세스의 버스 요구 도착시간 별 저장이 가능한 큐를 이용해 도착한 순서대로 서비스 제공

- Rotating daisy chain

- 모든 장치를 연결 하여 차례로 버스 서비스를 제공하는 방식

입출력 수행의 분류

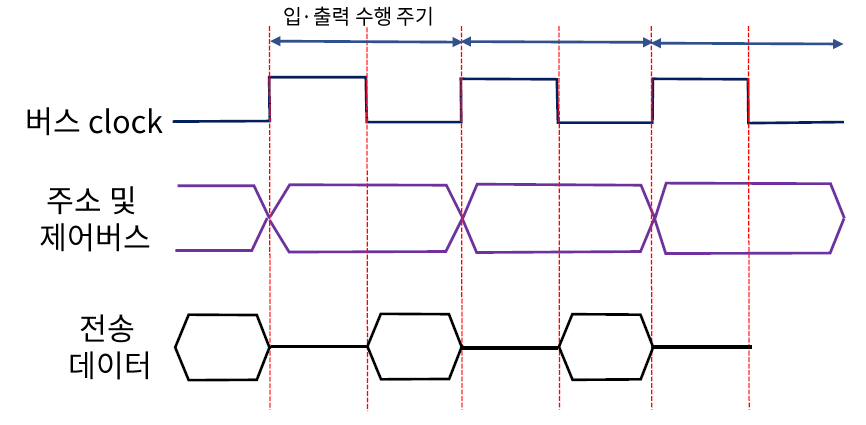

동기 버스에 의한 수행

버스에 연결된 모든 장치들에 동일하게 적용하는 버스 클락이 있고 주소와 자료 및 다른 제어선들은 버스 클락을 기준으로 전송된다.

- Bus clock(0 → 1) : 필요 장치의 주소 및 제어신호를 버스로 발송

- Bus clock(1 → 0) : 식별 후 데이터 전송 시작

버스의 연결된 모든 장치는 클락에 맞춰 입출력이 진행되도록 설계되어야 함

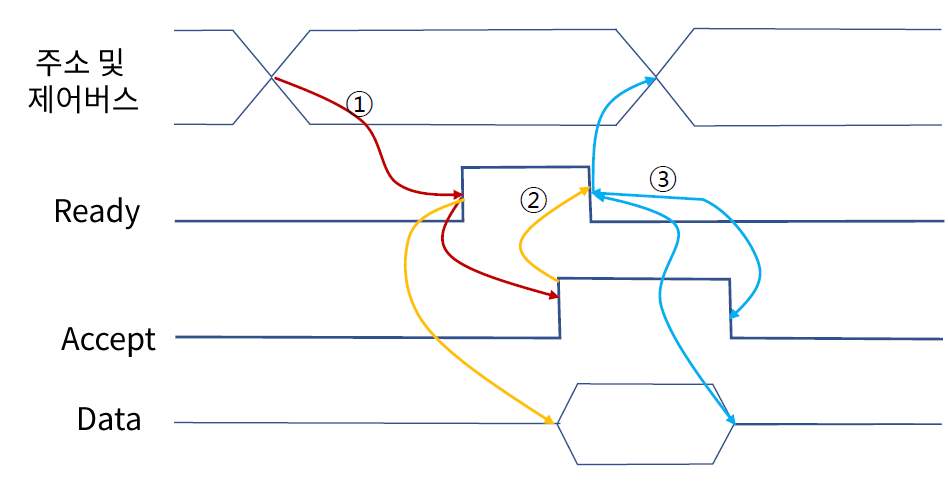

비동기 버스에 의한 수행

-> 주소선에 지정된 I/O 장치 주소를 전송한다.

-

CPU로부터 I/O 제어기를 통해 해당 장치의 Ready 신호 활성

-> I/O 전송 요구 Ready 신호 활성화

-> Ready 신호에 대한 응답으로 Accept 신호 전송 -

응답/자료 전송

-> Data 전송

-

작업 종료 신호의 비 활성화