25. 입출력 수행과 인터럽트

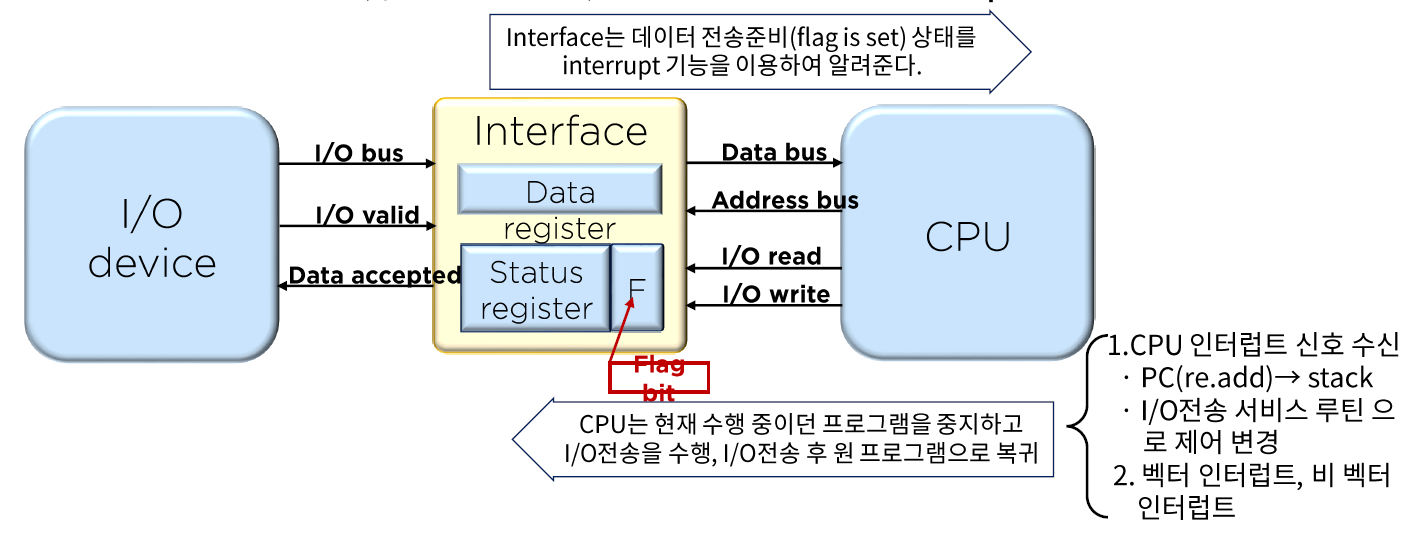

인터럽트에 의한 I/O

입출력 장치와 CPU간 전송 모드 측면

입출력 전송 구조 상 CPU의 인터럽트 활용모드

입출력 장치와 CPU간 전송에 대한 SW적 고찰

- 컴퓨터는 주변 장치와의 인터페이스를 위한 H/W 못지 않게 S/W 루틴을 가져야 한다.

- I/O 루틴은 주변 장치의 활성화를 위한 제어 커맨드의 발송 및 데이터 전송을 위한 준비 상태 체크 로직을 보유해야한다.

- 입출력 소프트웨어는 시스템에 인터럽트 제어를 줄 수 있어야 하며 이를 실행할 주변장치에 커맨드를 내려야 한다.

- Direct Memory Access 전송 시 I/O SW는 DMA 채널을 개시할 수 있어야 한다.

우선 순위 인터럽트

입출력 장치와 CPU간 인터럽트 논리

- CPU와 I/O 장치 사이의 데이터 전송은 CPU에 의해 시작

- 프로세서가 서비스 루틴으로 분기 주소를 선택하는 방법

- Vectored interrupt

- Non-vectored interrupt

- 수 많은 장치 중 인터럽트를 발생한 장치의 선별, 동시 발생한 다수의 인터럽트의 우선 순위를 결정해야 하는 문제 존재

따라서 우선 순위 인터럽트는 동시 다발적으로 발생한 인터럽트에 대한 서비스 순서를 겨정하기 위해 각 소스에 우선 순위를 부여한 인터럽트 시스템을 이르는 용어이다.

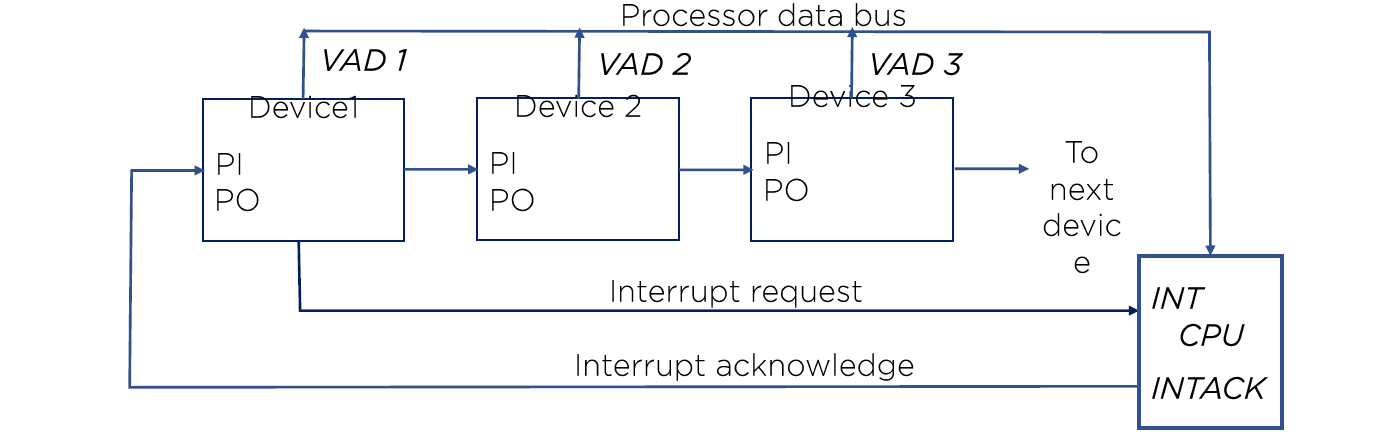

데이지 체인 우선 순위 인터럽트

인터럽트를 발생시키는 모든 장치를 직렬로 연결 함으로 이루어지는 구성

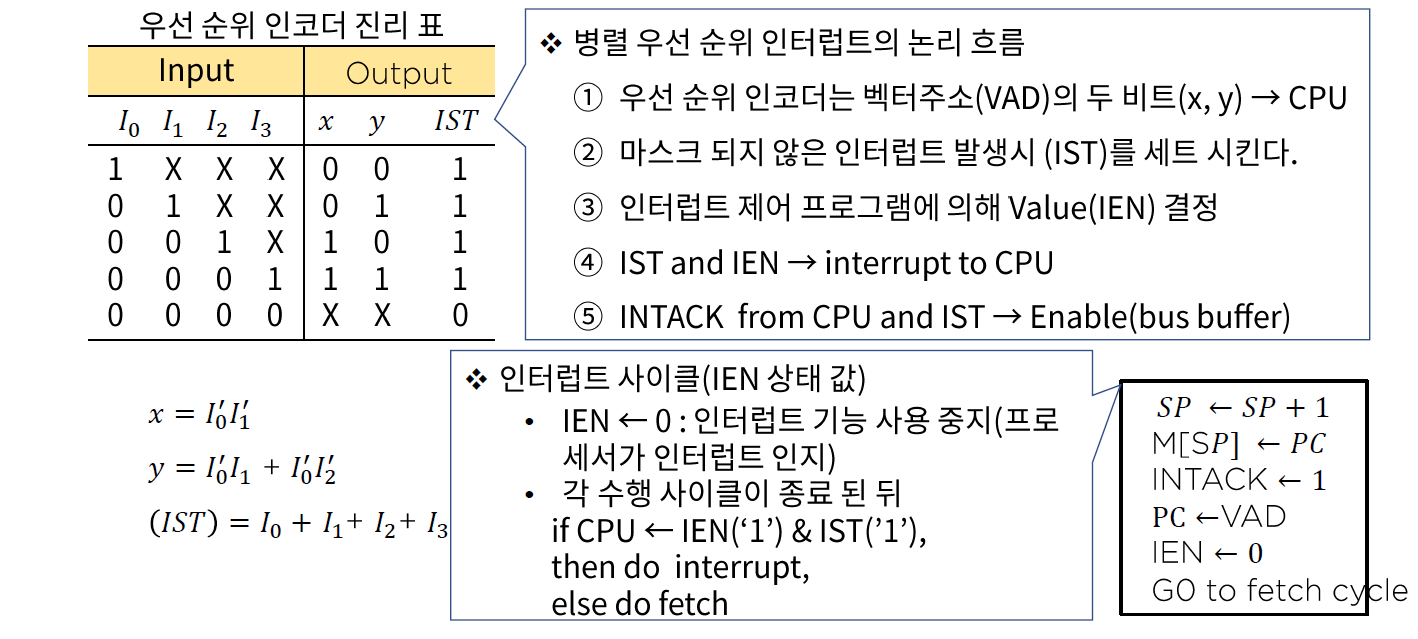

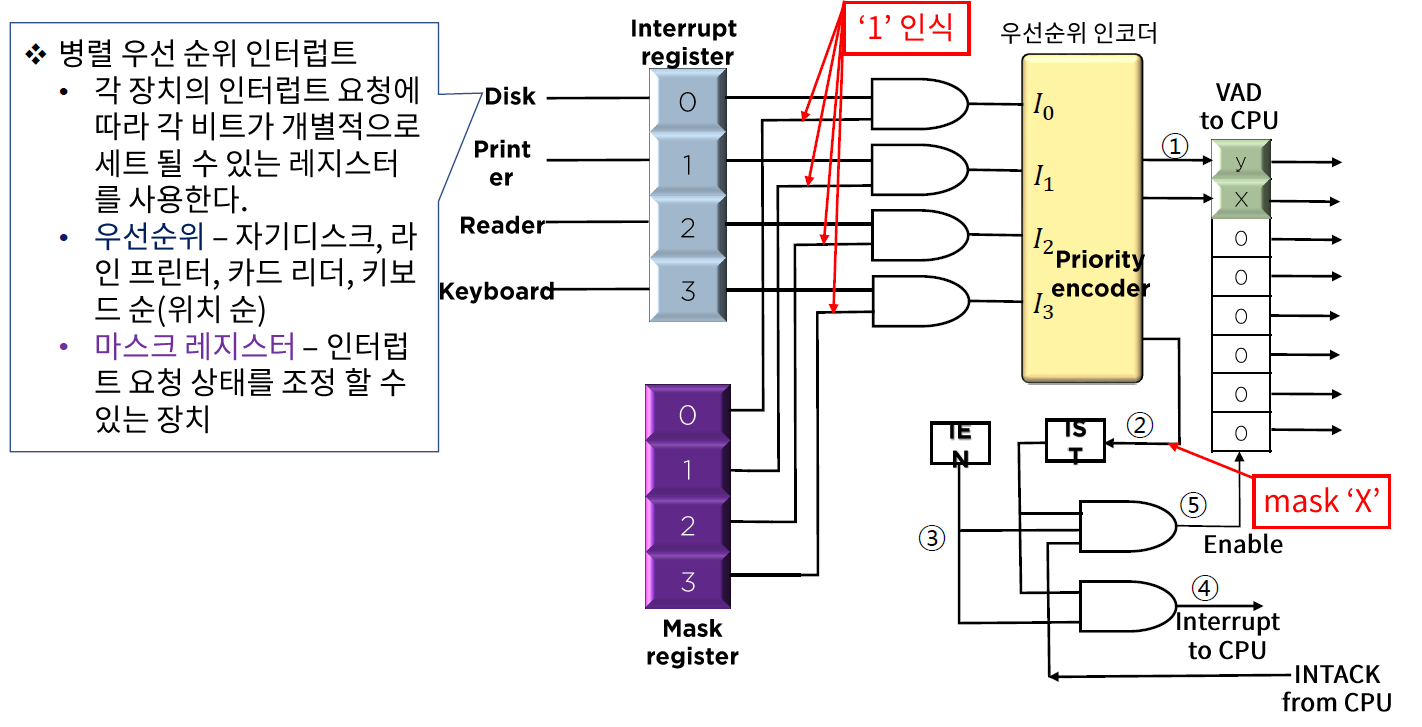

병렬 우선 순위 인터럽트

우선 순위 인코더 & 인터럽트 사이클