26. 시스템 성능 분석과 개선

프로세서 간 중재

시스템 버스 vs 로컬 버스

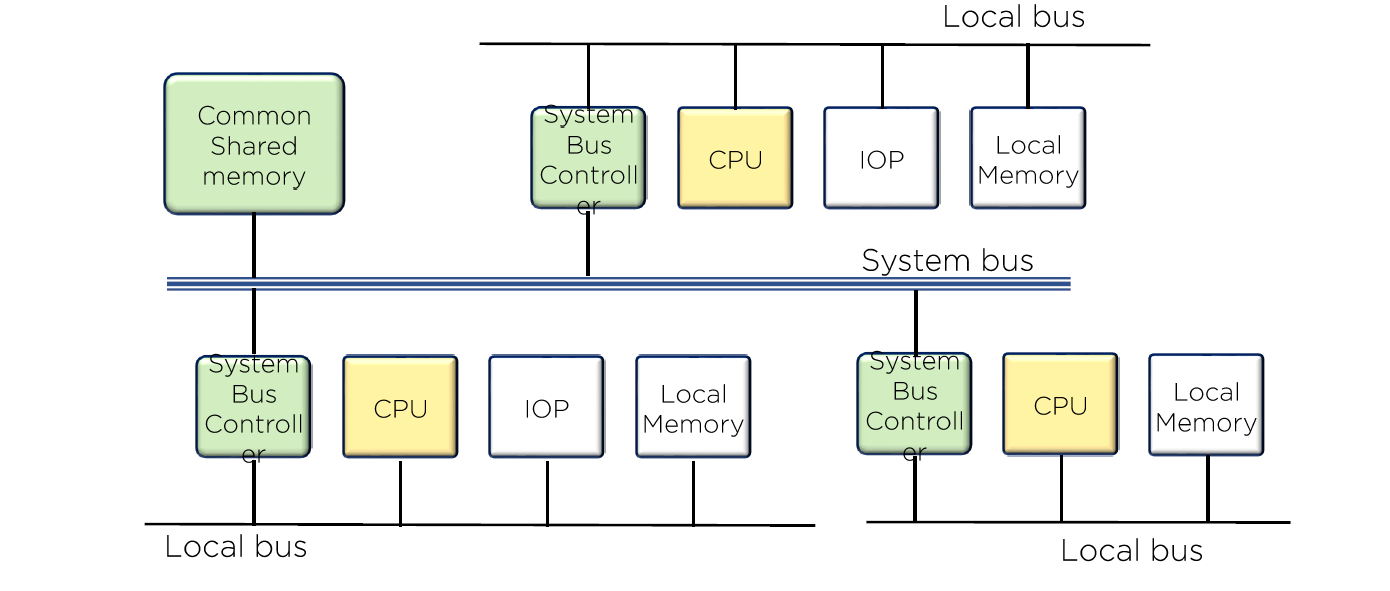

컴퓨터 시스템에는 각 요소들 사이의 정보 전송을 위한 다양한 단계의 여러 버스가 존재하며 CPU 내에서도 레지스터와 ALU 사이의 정보 전송을 위한 여러 내부 버스가 존재한다.

- System bus : CPU, I/O Processor, Memory와 같은 주요 요소를 연결하는 연결 체계

- Local bus : 메모리 버스, I/O 버스, 통신 전용 버스

공유 메모리 멀티 프로세서 시스템에서 각 자원의 효율적 분배와 상호 충돌을 배제할 수 있는 중재 프로세스는 전체 시스템 성능 향상에 지대한 영향을 미친다.

메모리 공유 멀티 프로세서를 위한 시스템 버스 구조

프로세서 간 통신과 동기화

프로세서 간 통신

멀티 프로세서 시스템에 있는 다양한 프로세서들은 공통의 입출력 채널을 통하여 서로 통신한다. I/O Processor에 연결된 자기 디스크 등 공통 메모리의 역할은 다음과 같다.

- 메모리의 일부를 모든 프로세서가 접근할 수 있도록 할당된 공간

- 인터럽트 신호를 통해 송신 프로세서 -> 수신 프로세서 로 가는 흐름

멀티 프로세서를 위한 운영체제의 종류는 다음과 같다.

- Master-slave mode

- Separate OS

- Distributed OS

프로세서 간 동기화

멀티 프로세서의 명령어 집합에는 함께 동작하는 프로세서와의 통신과 동기화를 구현하는 기본 명령어가 포함된다. 멀티 프로세서 시스템에서 자원의 동기화를 위해 가장 많이 활용되는 기법은 하드웨어적 접근 방법인 이진 세마포어를 이용하는 방법이다.

캐시의 일관성

캐시 관련 정책

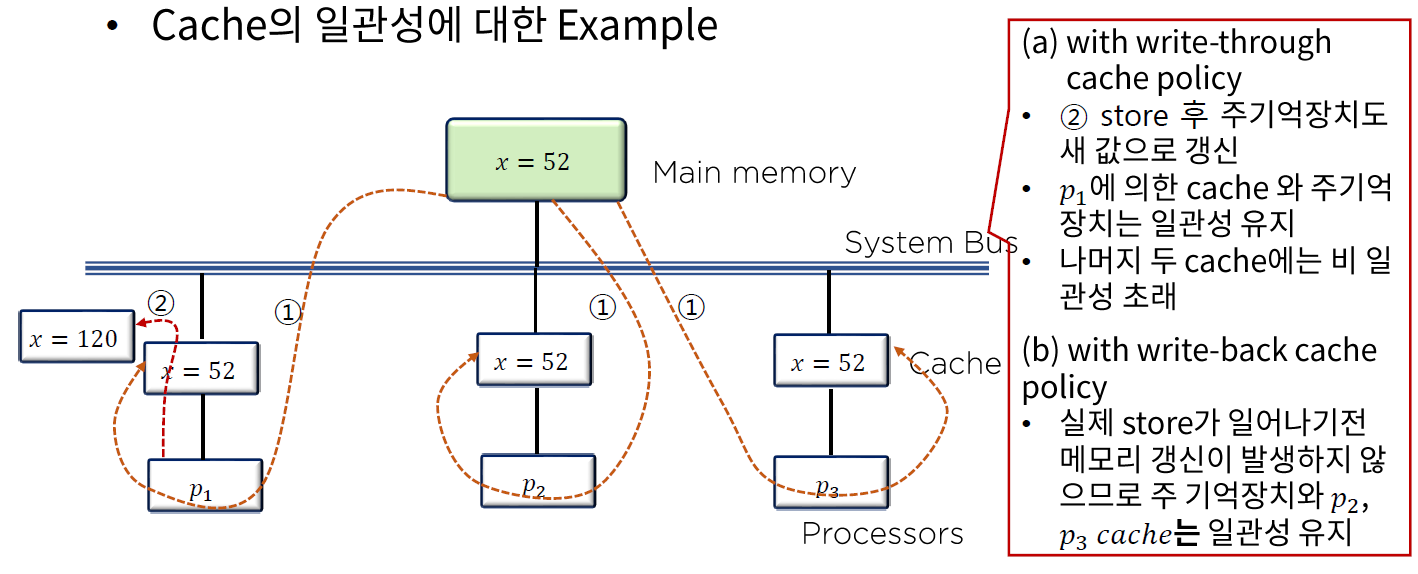

공유 메모리 멀티 프로세서 시스템에서도 각 프로세서는 로컬 메모리를 운영한다. 여러 개의 동일한 내용이 주 기억장치나 각 로컬 메모리에 복사본으로 중복되어 저장되는 경우가 발생할 수 있고 정확한 메모리 동작을 위해 이 내용들이 모두 동일하게 유지되어야 하는 정책이 Cache coherence(일관성)이다.

메모리 쓰기 동작 시 메모리 갱신 정책은 두 종류가 있다.

- Write-through : 쓰기 동작 발생 시 캐시와 주 기억장치 모두 갱신

- Write-back : 캐시만 갱신하고 다음에 메모리로 전달할 수 있도록 위치를 표시

캐시의 비 일관성에 대한 조건

캐시의 일관성 문제는 각 프로세스 별로 개별적인 캐시를 가진 멀티 프로세서에서 공통의 기록 가능한 데이터가 필요하기 때문에 발생한다.

캐시의 일관성 문제에 대한 해결책

- Cacheable : 비 공유적이고 읽기 전용 데이터에 한해 캐시에 저장되도록 하는 방안

- Snoopy cache controller : 기본적으로 버스에 부착 된 모든 캐시에 대해 버스 감시 기능을 유지하도록 설계 된 H/W 장치