시간이 없어서, 간략하게 기술한다.

자세한 설명은 시간이 날 때 적는 것으로.

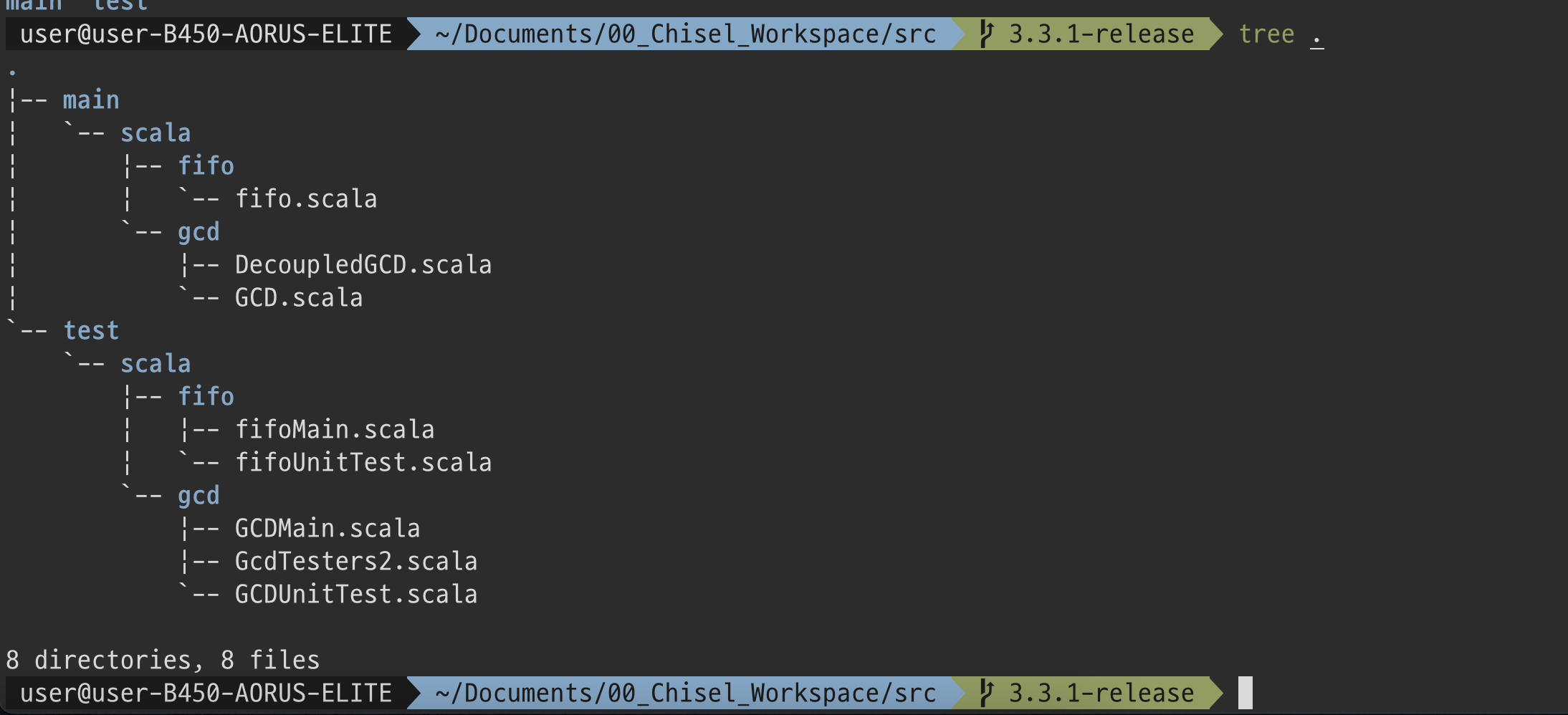

chisel-template로부터 generate한, 내 3.3.1-release branch

src/ 폴더구조

fifo 하위에 scala 파일을 만듬.

src/main 소스(찐 모듈)

src/main/scala/fifo/fifo.scala

/*

* Author: webserver3315

* Created: 2023.Aug.11

*

*

*/

package fifo

import chisel3._

import chisel3.util.log2Ceil

import chisel3.util.DecoupledIO

class fifo(val DEPTH: Int = 4, val WIDTH: Int = 32) extends Module {

val io =IO(new Bundle {

val in = Flipped(new DecoupledIO(UInt(WIDTH.W)))

val out= new DecoupledIO(UInt(WIDTH.W))

})

val dataReg = Reg(Vec(DEPTH*2, UInt(WIDTH.W)))

val empty = WireInit(true.B)

val full = WireInit(false.B)

val inPtrReg = RegInit(0.U(log2Ceil(DEPTH*2).W))

val outPtrReg = RegInit(0.U(log2Ceil(DEPTH*2).W))

empty := (inPtrReg === outPtrReg)

full := (inPtrReg =/= outPtrReg) && (inPtrReg(log2Ceil(DEPTH*2)-2,0) === outPtrReg(log2Ceil(DEPTH*2)-2,0))

io.in.ready := !full && io.in.valid

io.out.valid := !empty

io.out.bits := dataReg(outPtrReg)

when(!full && io.in.valid){

dataReg(inPtrReg) := io.in.bits

inPtrReg := inPtrReg + 1.U // Wrap around

}.otherwise{

}

when(!empty && io.out.ready){

outPtrReg := outPtrReg + 1.U // Wrap around

}.otherwise{

}

}

src/test 소스(ChiselTest)

src/test/scala/fifo/fifoMain.scala

/*

* Author: webserver3315

* Created: 2023/Aug/11

*

*/

package fifo

import chisel3._

object fifoMain extends App{

iotesters.Driver.execute(args, () => new fifo) {

c => new fifoUnitTester(c)

}

//println((new chisel3.stage.ChiselStage).emitVerilog(new fifo))

(new chisel3.stage.ChiselStage).emitVerilog(new fifo)

}

src/test/scala/fifo/fifoUnitTest.scala

package fifo

import java.io.File

import chisel3.iotesters

import chisel3.iotesters.{ChiselFlatSpec, Driver, PeekPokeTester}

class fifoUnitTester(dut: fifo) extends PeekPokeTester(dut){

val TEST_LENGTH = 10

// val test_sequence = Array.fill(TEST_LENGTH){

def make_test_sequence(t: Int): Unit = {

require(t>0, "testLength must be greater than 0")

for(i<-1 until t){

val random = rnd.nextInt(128)

poke(dut.io.in.bits, random)

poke(dut.io.in.valid, true)

poke(dut.io.out.ready, false)

step(1)

poke(dut.io.in.valid, false)

poke(dut.io.out.ready, false)

step(1)

// while(peek(dut.io.out.valid) == false){

// step(1)

// }

val result = peek(dut.io.out.bits)

printf("%dth TEST: result = %d, expected: %d\n", i, result, random)

expect(dut.io.out.bits, random)

poke(dut.io.out.ready, true)

step(1)

}

}

make_test_sequence(TEST_LENGTH)

}

실행

sbt 'test:runMain fifo.fifoMain --generate-vcd-output on'결과

[info] Loading settings for project root-00_chisel_workspace-build from plugins.sbt ...

[info] Loading project definition from /home/user/Documents/00_Chisel_Workspace/project

[info] Loading settings for project root-00_chisel_workspace from build.sbt ...

[info] Set current project to fifo (in build file:/home/user/Documents/00_Chisel_Workspace/)

[warn] Multiple main classes detected. Run 'show discoveredMainClasses' to see the list

[info] running fifo.fifoMain --generate-vcd-output on

[info] [0.002] Elaborating design...

[info] [0.555] Done elaborating.

[info] [0.000] SEED 1692110891701

1th TEST: result = 7, expected: 7

2th TEST: result = 91, expected: 91

3th TEST: result = 62, expected: 62

4th TEST: result = 82, expected: 82

5th TEST: result = 69, expected: 69

6th TEST: result = 116, expected: 116

7th TEST: result = 105, expected: 105

8th TEST: result = 43, expected: 43

9th TEST: result = 29, expected: 29

test fifo Success: 9 tests passed in 32 cycles in 0.038112 seconds 839.63 Hz

[info] [0.020] RAN 27 CYCLES PASSED

[info] [0.000] Elaborating design...

[info] [0.006] Done elaborating.

[success] Total time: 2 s, completed Aug 15, 2023 11:48:13 PM의도대로 동작함을 확인가능하다.

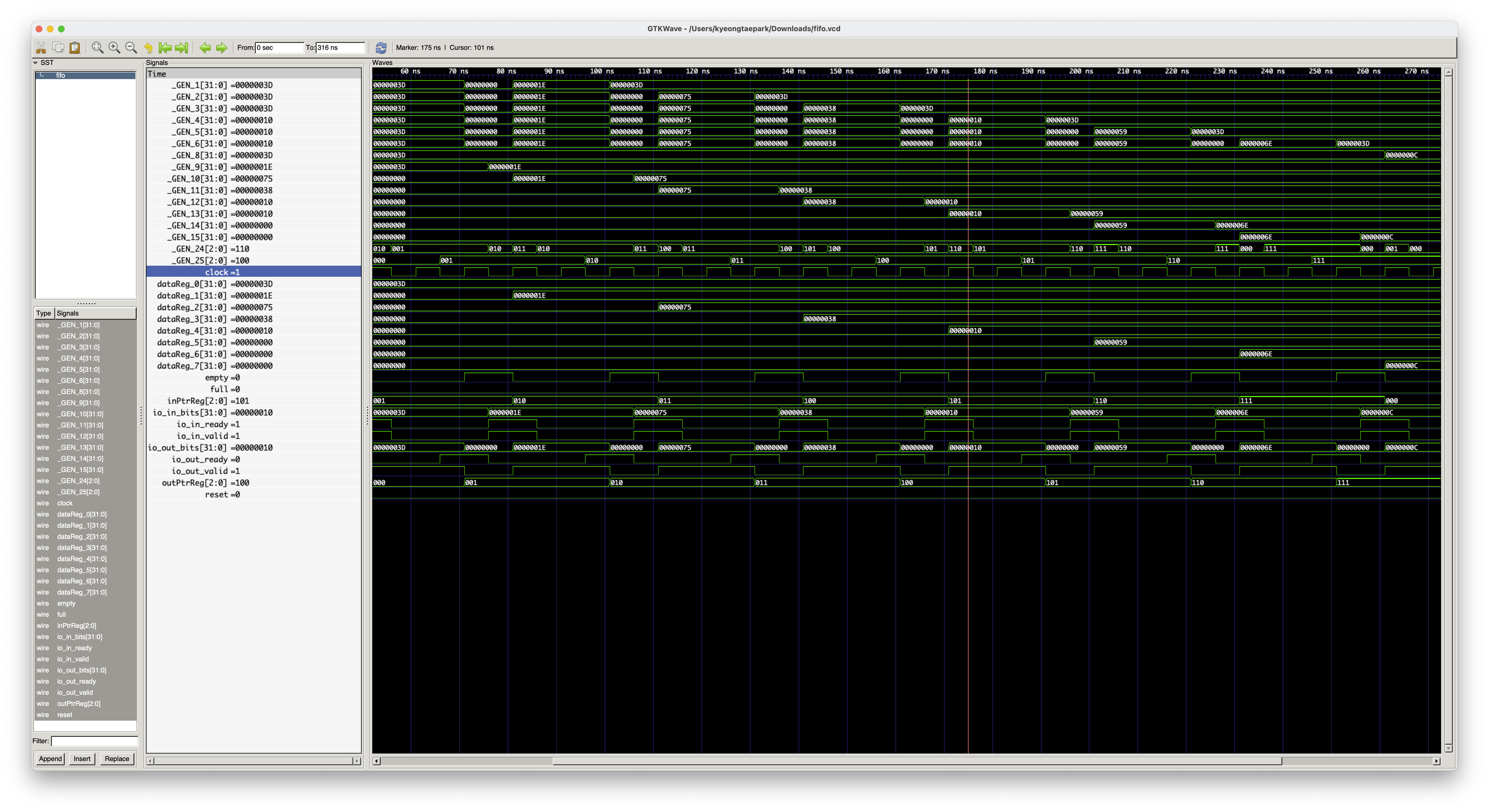

gtkWave로 vcd 확인

파형을 볼 수 있다.

다만, 파형을 보기에는 변수명이 .v로 generate 될 시 생긴 자동변수명들이라, 매우 난해해서

실제 개발에서 이슈가 터진다면,

디버깅은 ChiselTest에서 println 디버깅을 해야할 것 같다.

좋은 글이네요. 공유해주셔서 감사합니다.