Chisel 독학

1.[Chisel] 1 - Introduction to Scala

Chisel 독학을 위한 타래를 만들었다. Reference ^ 위 레퍼런스를 따라갈 생각이다. ucb-bar/chisel-tutorial freechipsproject/chisel-bootcamp => 가장 메인이 될 것 같다. 주피터 노트북 튜토리얼이 웹에서 참

2.[Learning Scala] Ch1, 2: Scala 시작하기~리터럴, 값, 변수, 타입

회사에서 Scala 책을 빌렸다.Learning Scala부서에서 사용하는 툴이 쓰는 언어는 모든 것의 기본이다. 언어를 모르면 대화자체가 되지 않으니까.따라서, Scala를 좀 더 심화하여 공부하기로 하였다.파트장님과 잠깐 얘기를 해봤는데, val == 상수 라는 나

3.[Chisel] Ubuntu에 Chisel 개발환경 Setup

ipynb 튜토리얼이 있긴 하다만,언제까지나 ipynb 웹상에서 진행할 수는 없는 노릇이니,Ubuntu 18.04 로컬상에서 Chisel 환경을 설치하고자 한다.SBT가 뭔지도 모르고, 여러 모르는게 많다.일단 오늘은 늦었으므로, 이해없이 환경셋업만 신속하게 끝내기로

4.[Scala] BOJ 1000: A+B

Scala 언어자체에 익숙해지기 위해, PS를 해보기로 한다.내 Problem Solving 실력은 주력 언어인 C++로 했을 때조차 삼성 Advanced 수준에 불과하지만,목표는 알고리즘 학습이 아니라,향후 Chisel을 사용함에 있어서 Scala의 미숙이 걸림돌이

5.[Scala] PS 길라잡이

2023.07.29 현재...2019.03.07에 내가 군복무시절 작성한 글을 참고로 커리큘럼을 짜게 될 줄이야.다양한 느낌이 든다.개발자의 블로그 운영은 선택이 아닌 필수이다. 4년이 지났는데, 여전히 같은 문제를 풀게 되다니..(비록 전혀 다른 언어일지언정).내 수

6.[Scala] BOJ 10950: A+B - 3

https://www.acmicpc.net/problem/10950믿기지 않겠지만, 삽질을 좀 했다.로컬에서는 잘 도는데, 백준에서는 Runtime Error만 나와서, 고생했다(...)1\. val t:Int = StdIn.rea

7.[Scala] BOJ 10951: A+B - 4

https://www.acmicpc.net/problem/10951역시 삽질 좀 했다.(20분)관건은, t를 미리 받지 않고, 무제한 input stream에서 EOF를 어떻게 감지하느냐다.내 삽질은 아래와 같다.1\. var li

8.[Scala] BOJ 10818 - 최소, 최대

https://www.acmicpc.net/problem/10818삽질목록1\. 처음에는val M:Int = intlist.maxval m:Int = intlist.min에서, intlist가 아니라 쌩으로 list를 썼다.그 결과, List(10, 20, 3

9.[Scala] BOJ 1920 - 수 찾기

https://www.acmicpc.net/problem/1920결과: 시간초과스칼라가 좀 느리긴 하던데(C에서 200ms걸리는게 2000ms나 걸림), 아예 Timeout Error가 뜰 줄이야...아마, Vector에 넣고 10만개짜리 원소 배열에서 해당

10.[Scala] BOJ 10828 - 스택

https://www.acmicpc.net/problem/10828사실, 개발할때는 디큐 하나면 다 되긴 하지만제일 만만한 스택부터 풀었다.시간초과가 발생했다.그러나, 이 부분에서 더 최적화될 여지는 없다고 생각한다.Scala 자체적인 한계라고 판단하고, 그냥

11.[Scala] BOJ 10866 - 덱(디큐)

https://www.acmicpc.net/problem/10866ArrayDeque를 사용했다.ArrayDeque는 Scala 2.13부터 추가된 자료구조로출처,head, tail 상수시간 접근을 보장하는 서큘러 버퍼로 되어있어서Tree로 구현되어있는 Vec

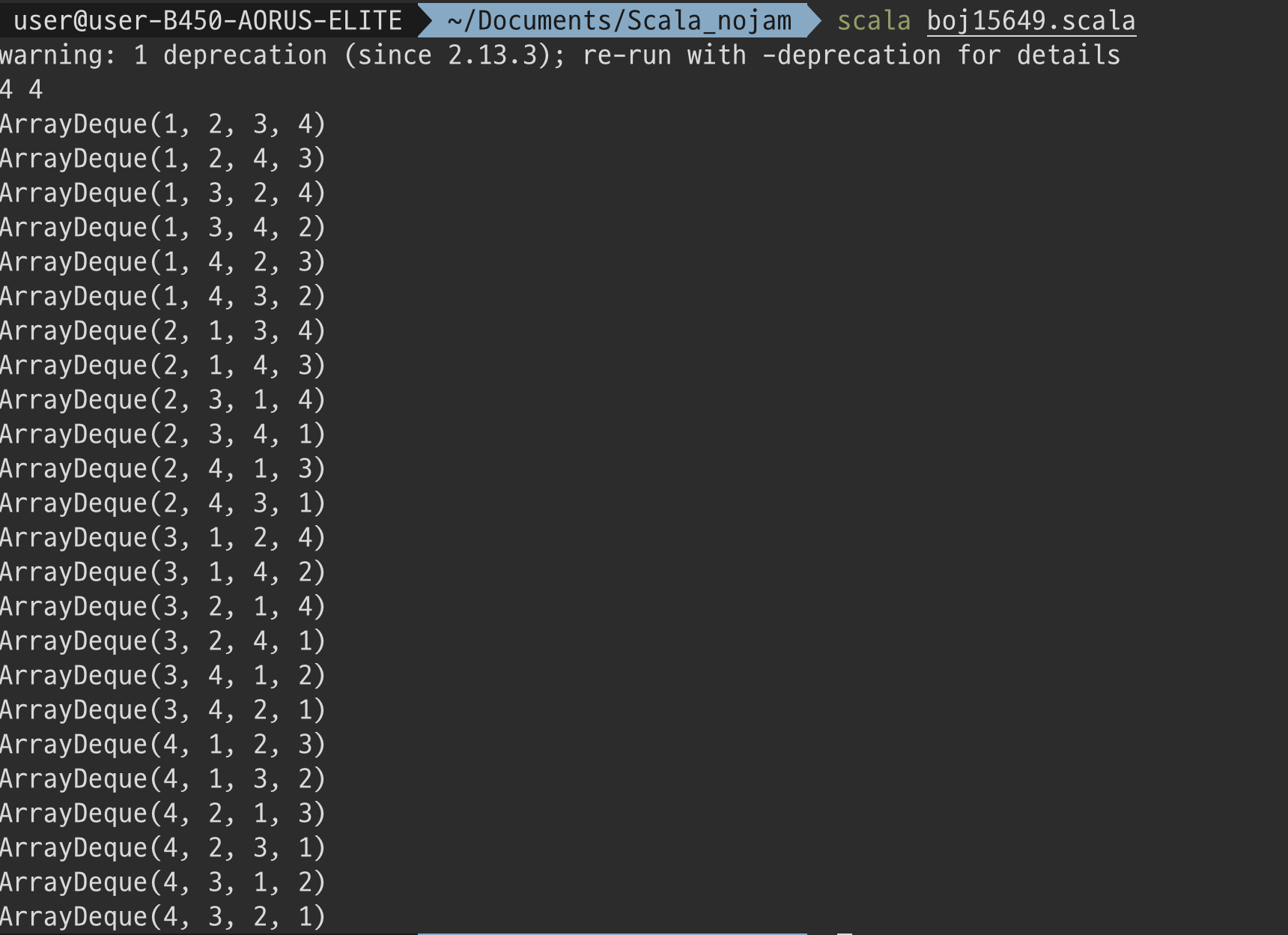

12.[Scala] BOJ 10866 - N과 M 1

재귀 공부하는데는 N과 M만한게 없다.https://www.acmicpc.net/problem/15649Scala에서는 continue문 없이 break() 메서드만 존재한다. 이를 위해 breakable 블록을 미리 잡아놓아야 하며, 이를 위해 또 impor

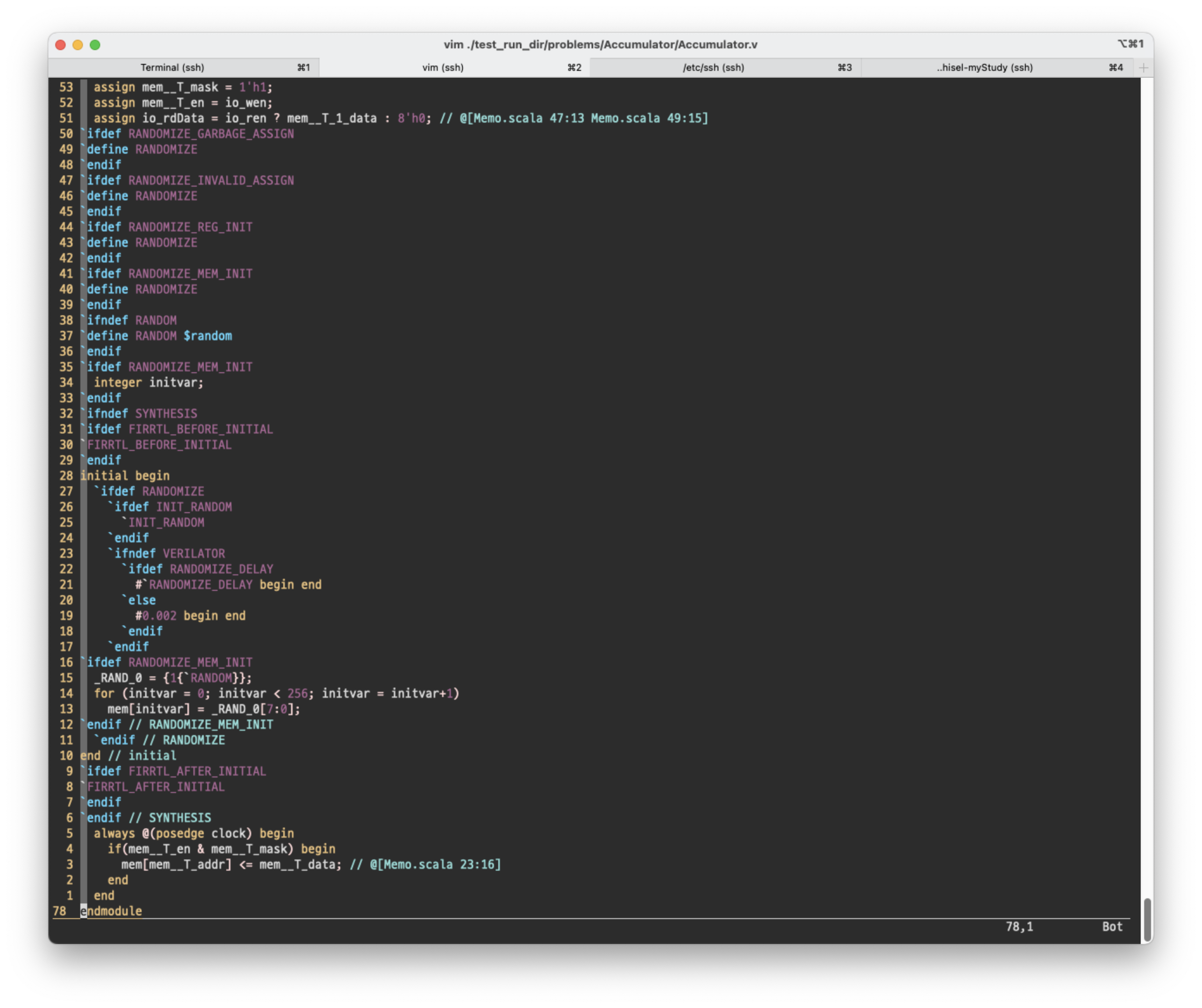

13.[chisel-tutorial] Memo.scala

예제 출처아주 간단한 R/W 레지스터 파일을 구현하는 문제이다.원인은, io.rdData가 실제로 elaborate될 때, Mux로 elaborate 되는데, 기본값이 도대체 무엇이냐를 scala상에서 명시하지 않아서 verilog로 elaborate하는데는 성공했지만

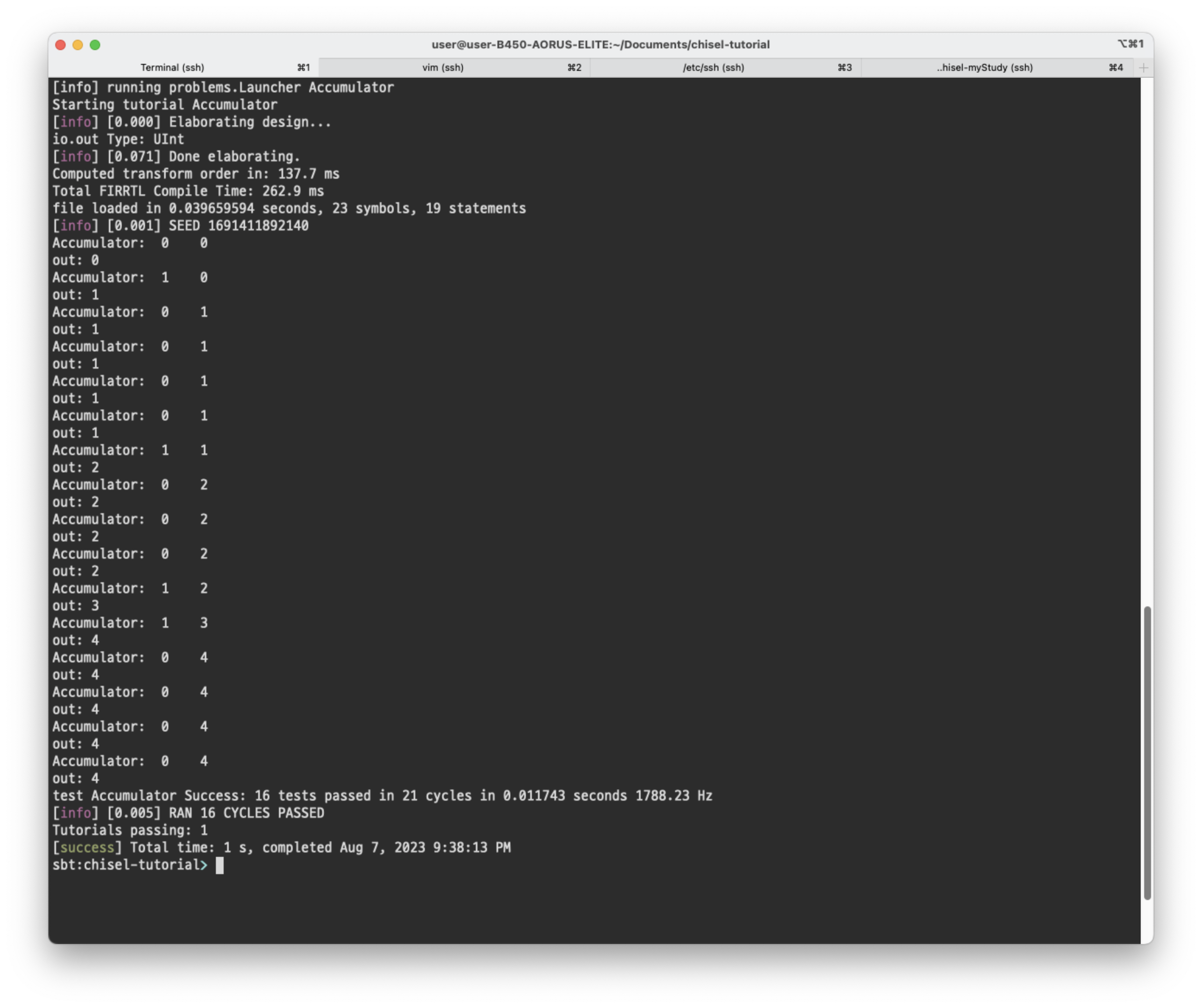

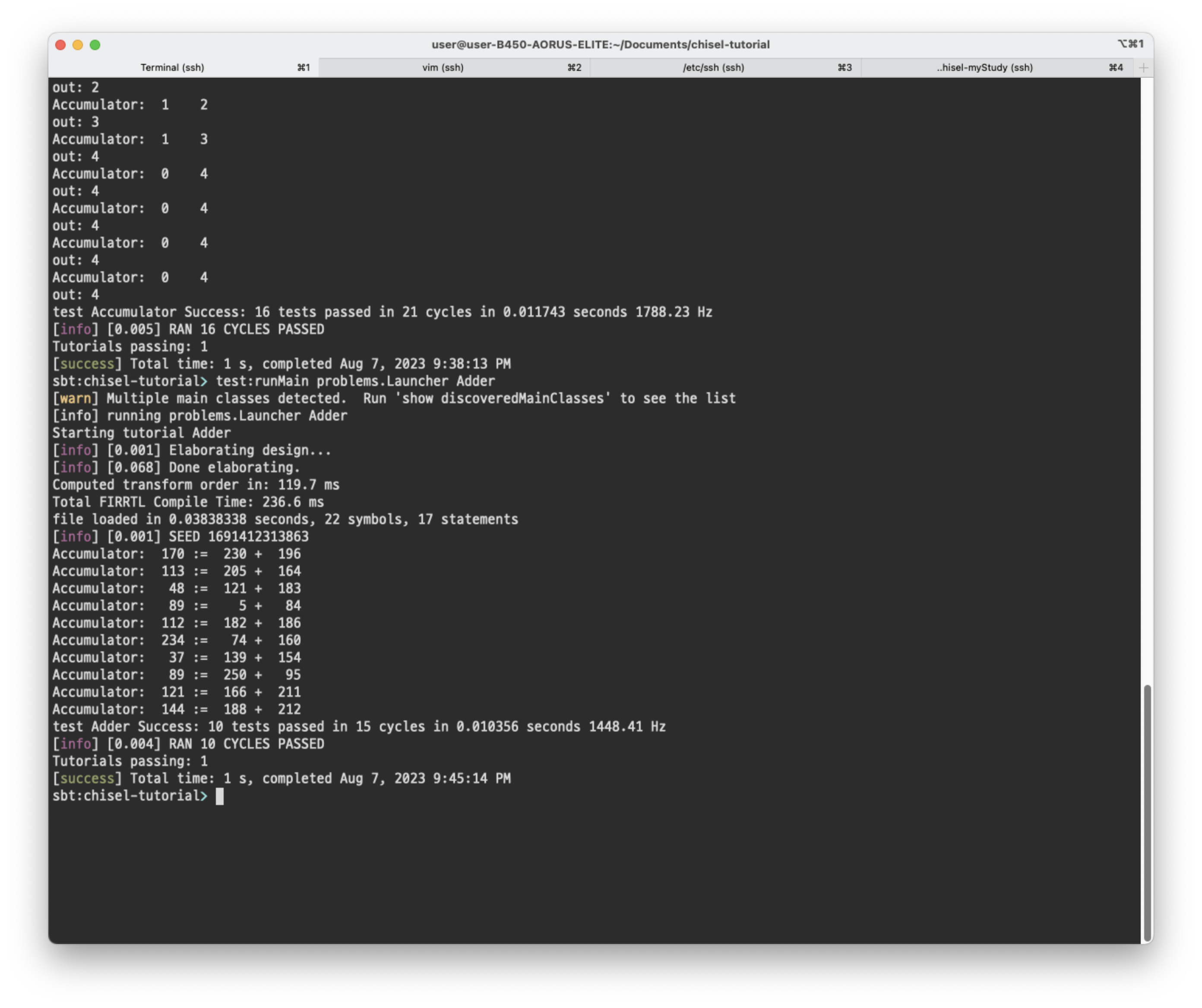

14.[chisel Tutorial] Accumulator.scala

Chisel Tutorial 상에서는 총 22개의 예제가 제공되고있고, 이것을 전부 풀어보려고 한다.실행법은 아래 내 포스트를 참고Register 선언 및 0 초기화는 RegInit(0.U(레지스터길이.W)) 로 하면 된다.Chiasel Datatype 간의 ass

15.[chisel-tutorial] Adder.scala

간단한 Adder 만드는 예제이다.오해의 여지가 없을 정도로, 매우 쉽다.다만, width를 w로 paramaterize해야 하는 함정이 있다.

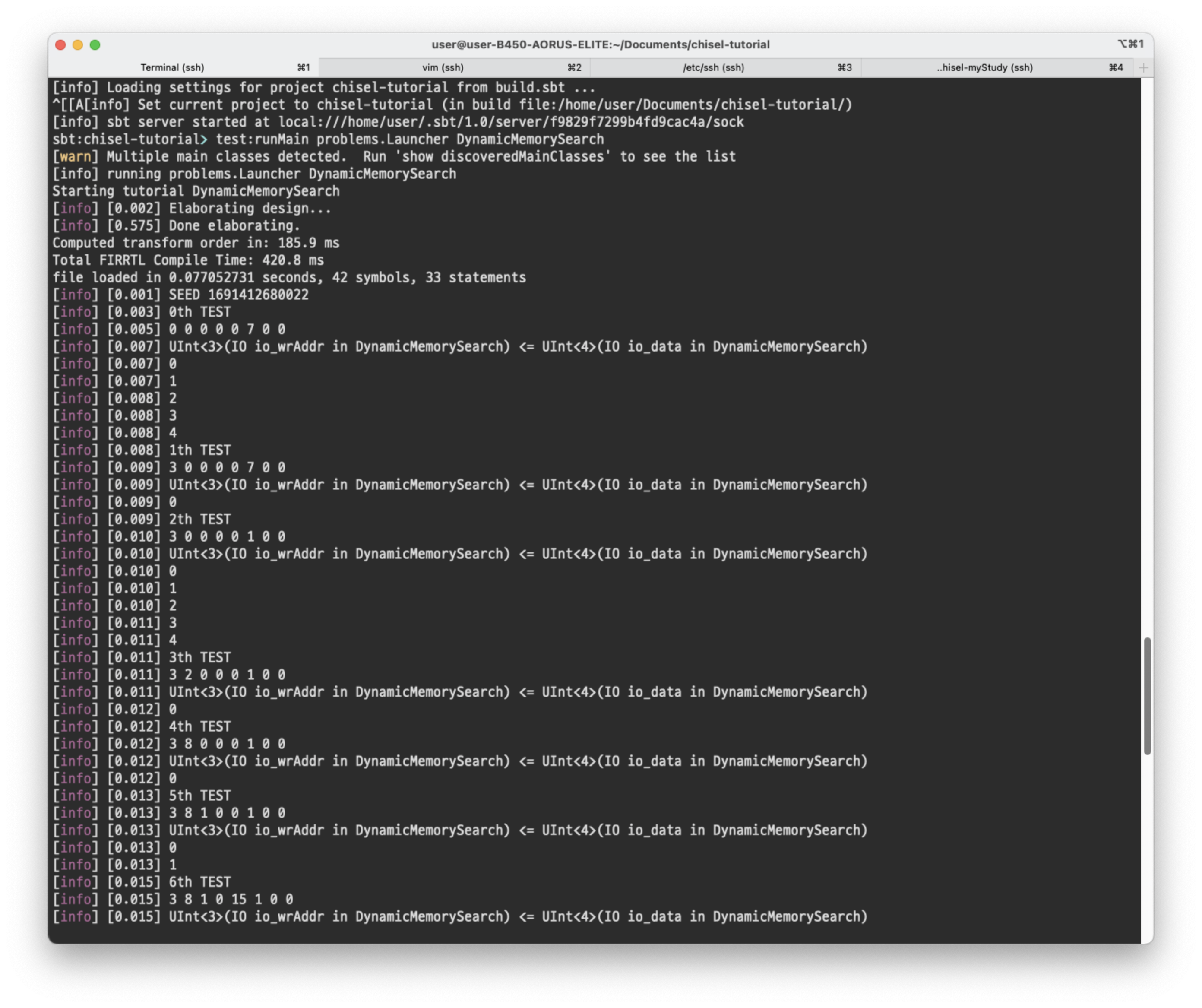

16.[chisel-tutorial] DynamicMemorySearch.scala: 그냥 어려움

임의의 주소에 쓰고, 선형적으로 읽은 뒤, 찾아진 index를 반환하는 것을 확인할 수 있다.Register가 HW적으로 구현되어야겠다는 생각이 들면, RegInit으로 Register를 명시적으로 만들어야 한다.RegInit과 Mem은 다르다. Mem은 packed

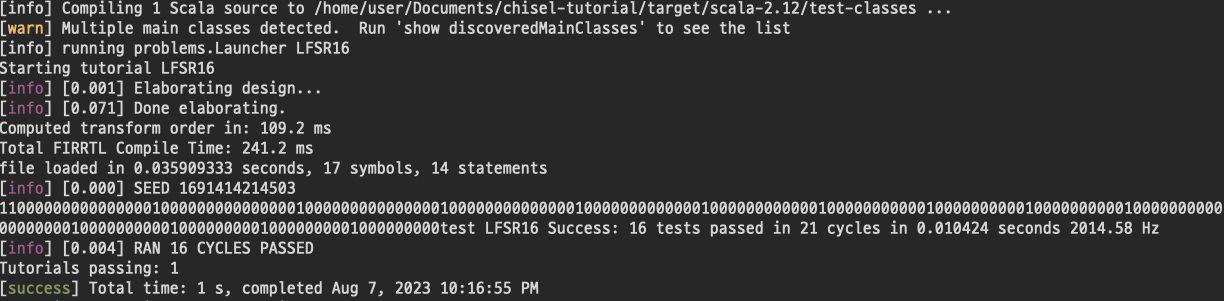

17.[chisel-tutorial] LFSR16.scala

// with polynomial x^16 + x^14 + x^13 + x^11 + 1라는 문제요구사항을 잘 모르겠어서, 해답을 참조했다.\+가 아니라 왠 XOR이, 그리고 index 또한 0 2 3 5로, 16 14 13 11 0과 동떨어진 것이 나왔지만,코드스타일

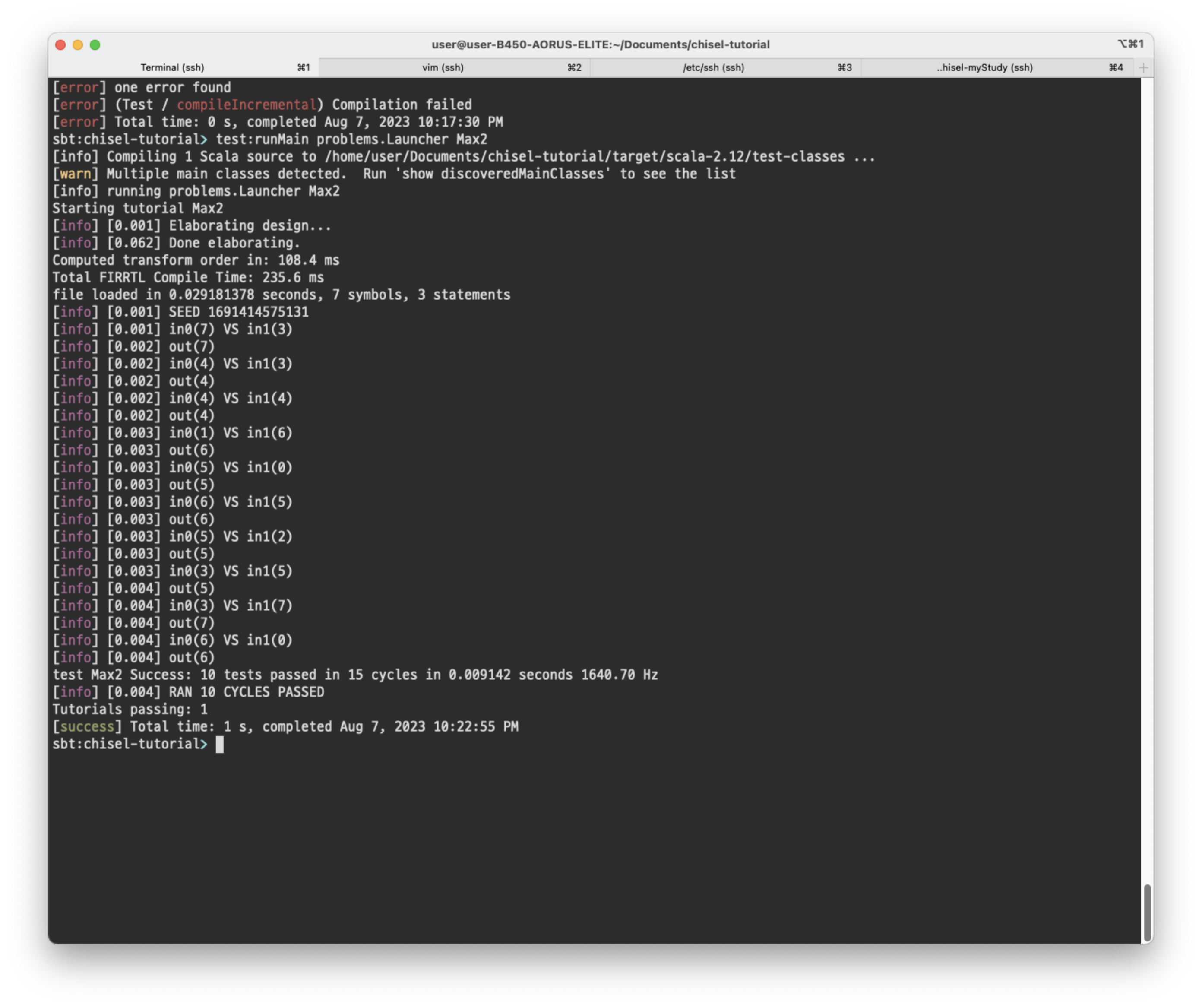

18.[chisel-tutorial] Max2: Testcase 작성

이번 문제는 독특하게, testcase를 만드는 문제이다.주어진 모듈은 쉽다.그저 두 입력 중 큰 쪽을 출력하는 MUX이다.그럼, 이것을 어떻게 테스트할 수 있을까?Mux(io.in0 > io.in1, io.in0, io.in1)를 통해, MUX를 구현가능하다.단순한

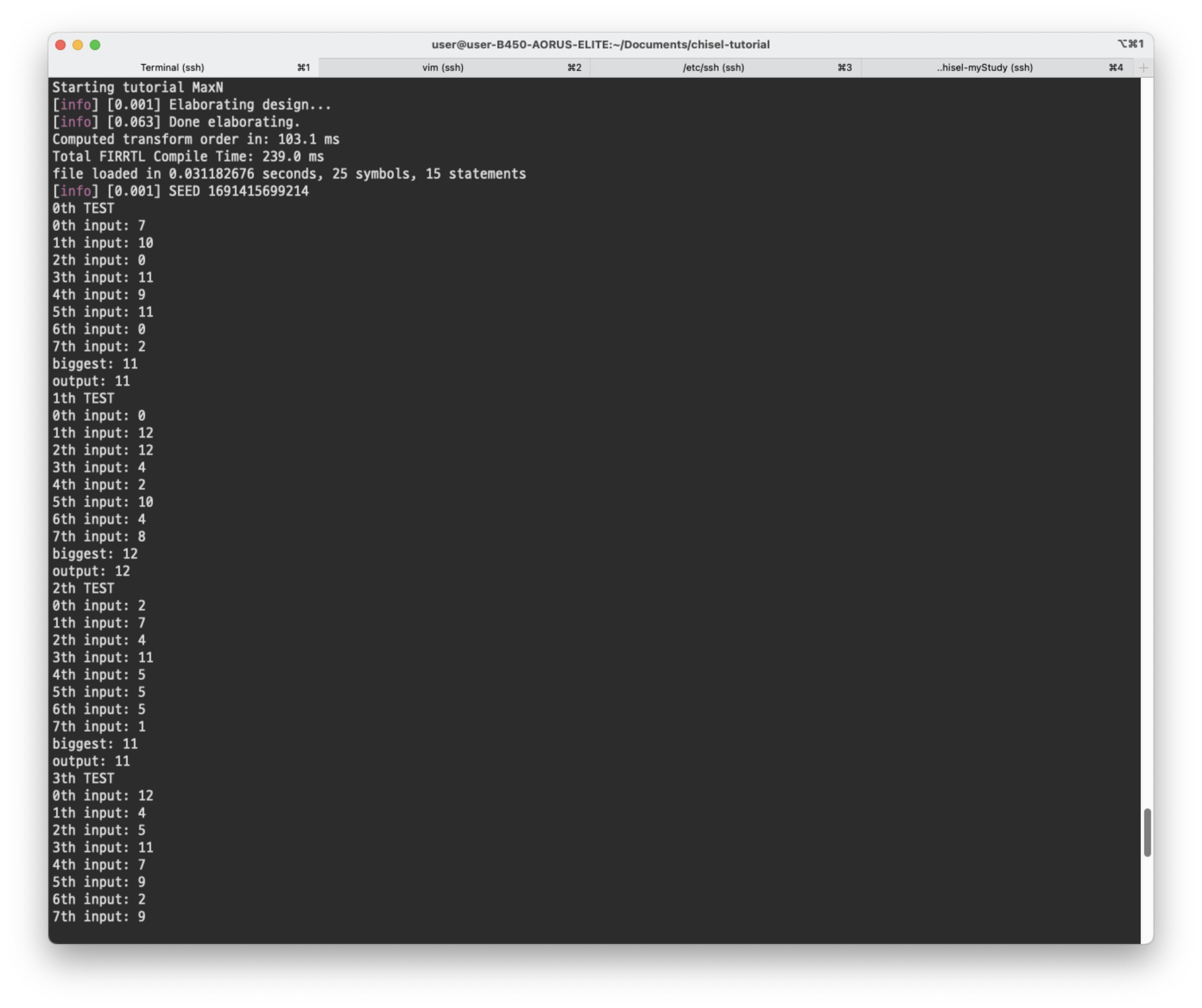

19.[chisel-tutorial] MaxN: reduceLeft 사용 및 Testcase 생성

Max2와 마찬가지로, Testcase를 제작하는 문제이다. reduceLeft라는 생소한 함수를 처음 알게 되었다. iterative 가능한 Vec 같은 자료구조에서, 쭉 동일한 op를 해나가기 위한 함수로 이해하였다.

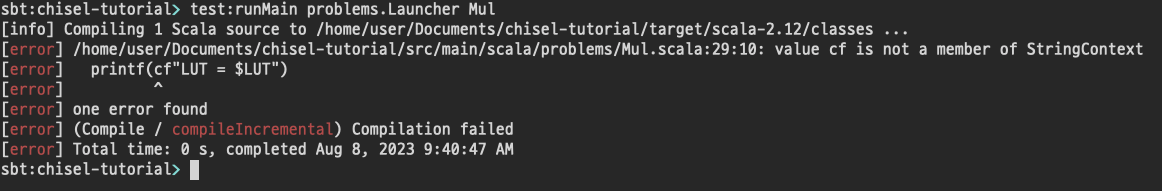

20.[chisel-tutorial] Mul.scala:

4\*4 곱셈을, Multiplier가 아니라 Lookup Table을 256가지 모든 경우의 수에 대해 만들어서 구현하라는 문제이다.Verilog로 하면 5분컷이지만, Chisel로 하니까 낯설었다.간단하게, 랜덤변수 x,y를 받아 입력한 뒤, 한 사이클 뒤에 출력되

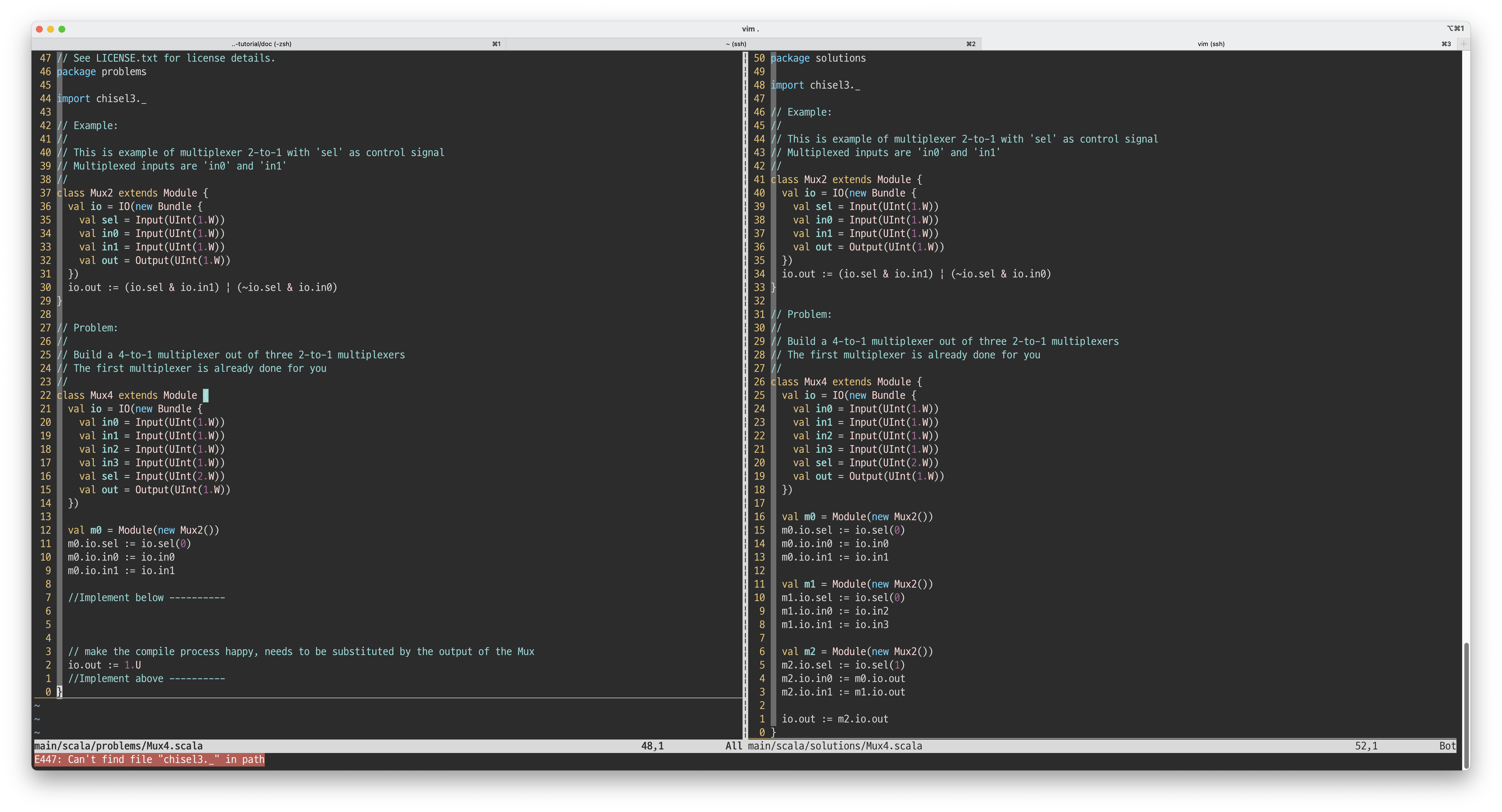

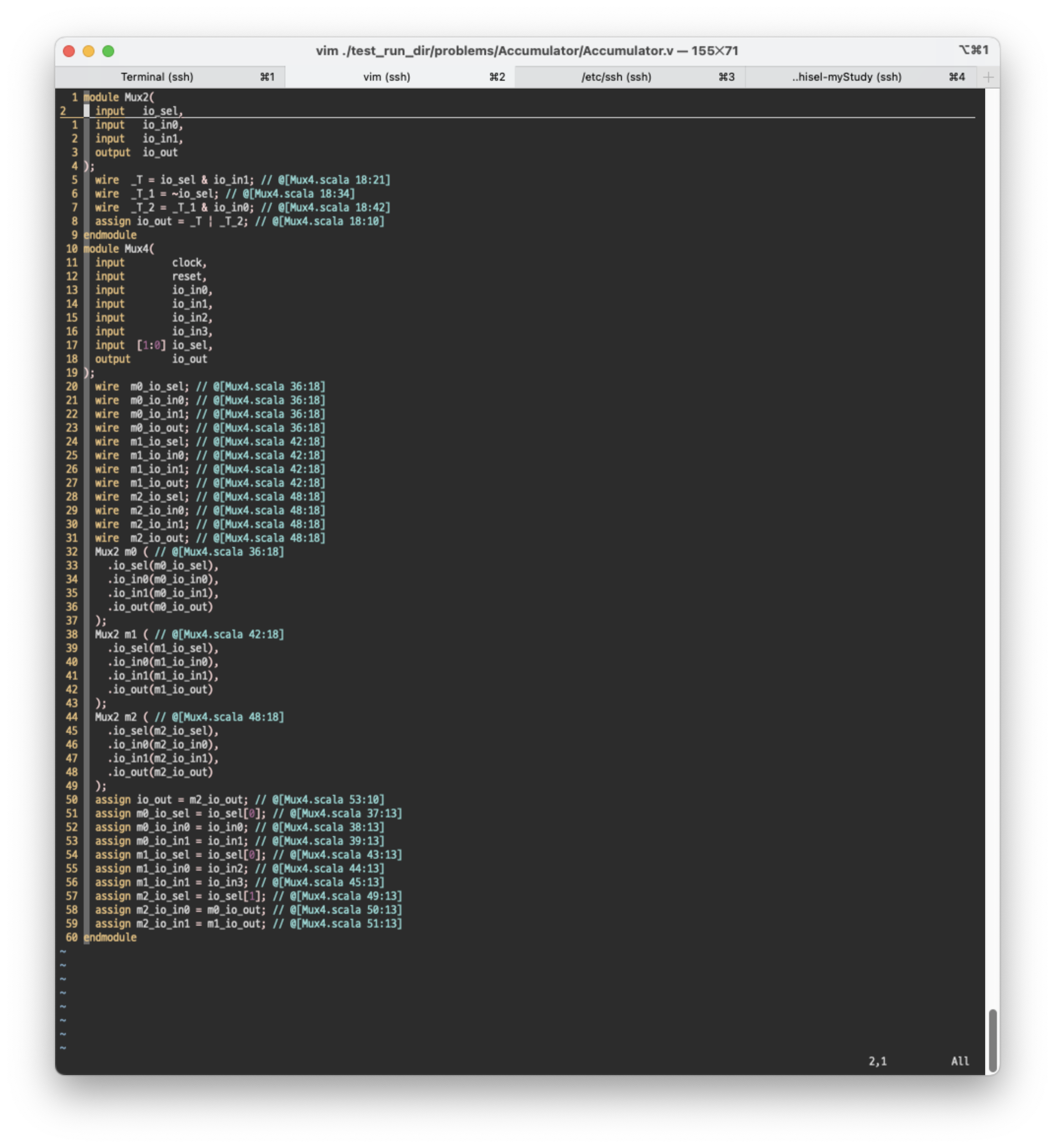

21.[chisel-tutorial] Mux4.scala: Chisel은 정직하다(?)

아주 간단한 문제다.Mux2를 3개 써서 Mux4를 만들면 된다.에러발생어 뭐가 문젠데? 근데 elaborate는 되었네? .v나 봐볼까?헉출력이 그냥 hardwire잖아?왜 1로 hardwire 되어있을까?당연하다. io.out := 이 없으니까.근데, x로 hard

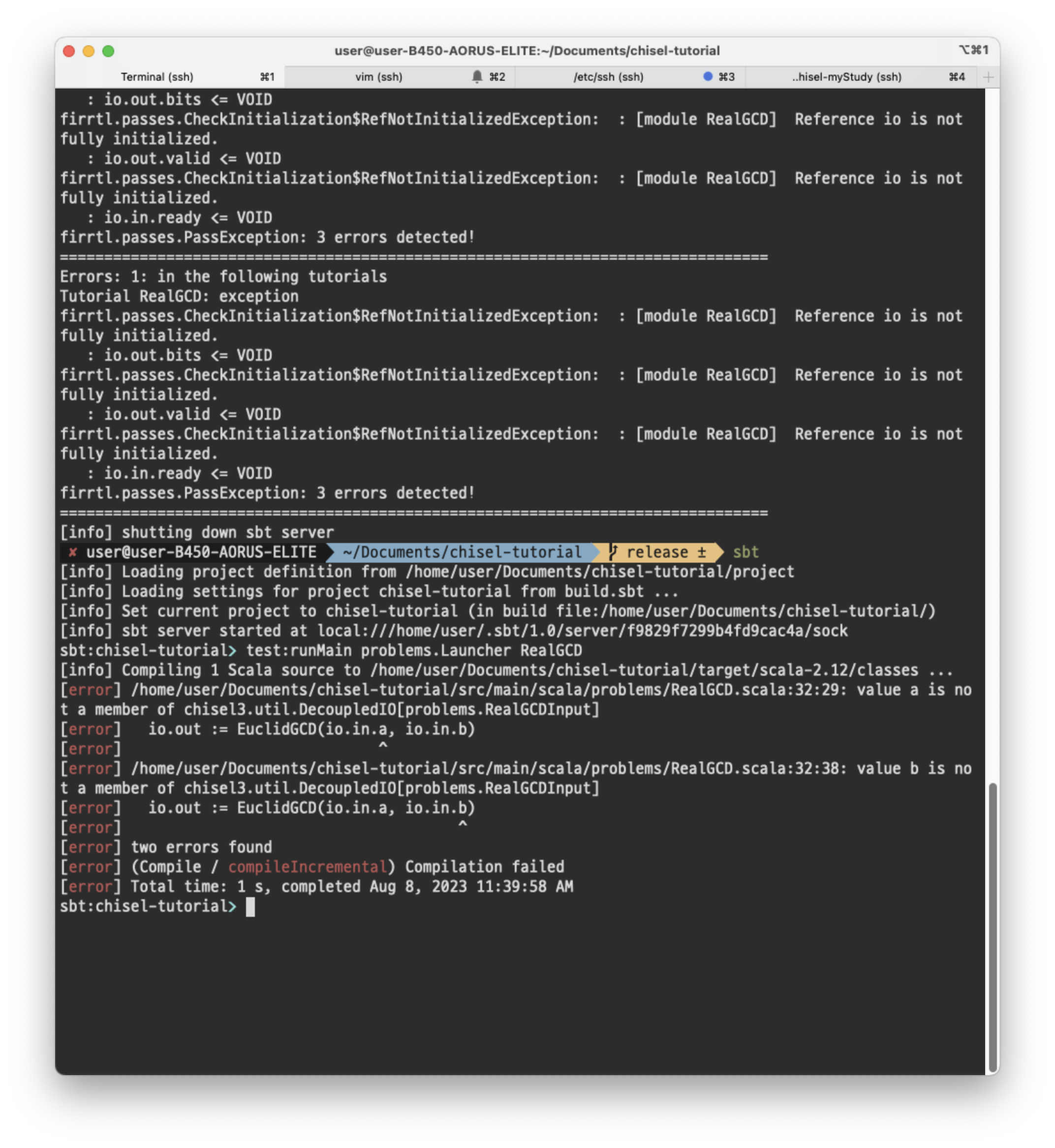

22.[chisel-tutorial] RealGCD.scala: DeqIO 및 bits, swap, Register reset 여부

초장부터 좀 빡세보였다.io 선언부터 쉽지 않아보였다. 도대체 이게 뭐야;GCD는 유클리드 알고리즘을 써야 하는데, 이건 SW적으로 돌아가는 재귀문이잖아? 이걸 Verilog로 elaborate되어야 하는 chisel 언어로 작성하라고?유클리드 호제법은 나눗셈으로도 구

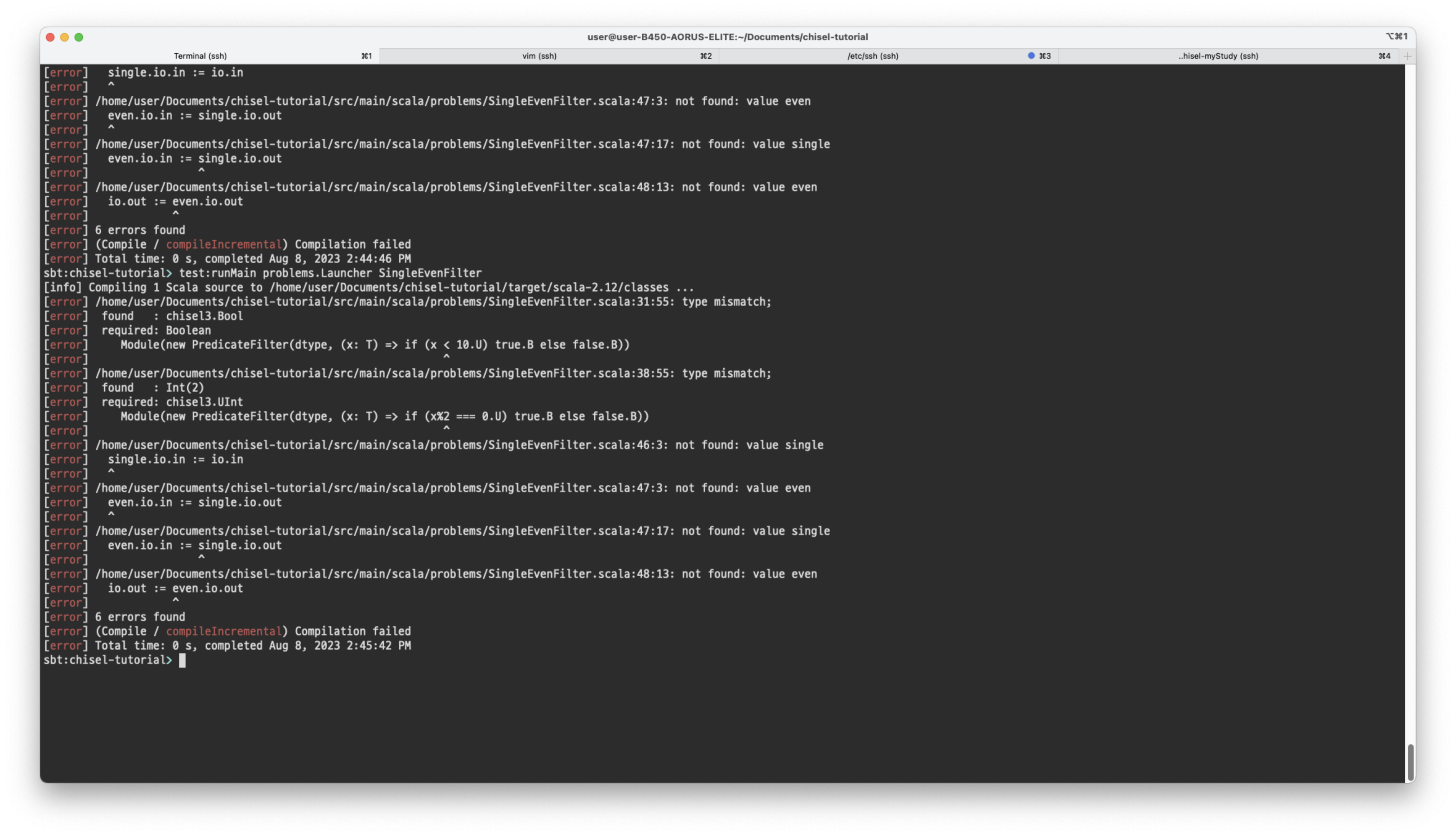

23.[chisel-tutorial] SingleEvenFilter.scala: chisel3 자료형 넘기기

간단하다. 10 미만이면서, Even인지를 판별하기 위해2개의 주어진 Filter를 랜덤수를 만들고, 9이하이면서 홀수인지 여부를 테스트하는 단순한 코드이다.fat arrow(=>)는 함수 선언에 사용된다. 아래는 ChatGPT 답이다(그런데, 특히 Chisel에서는

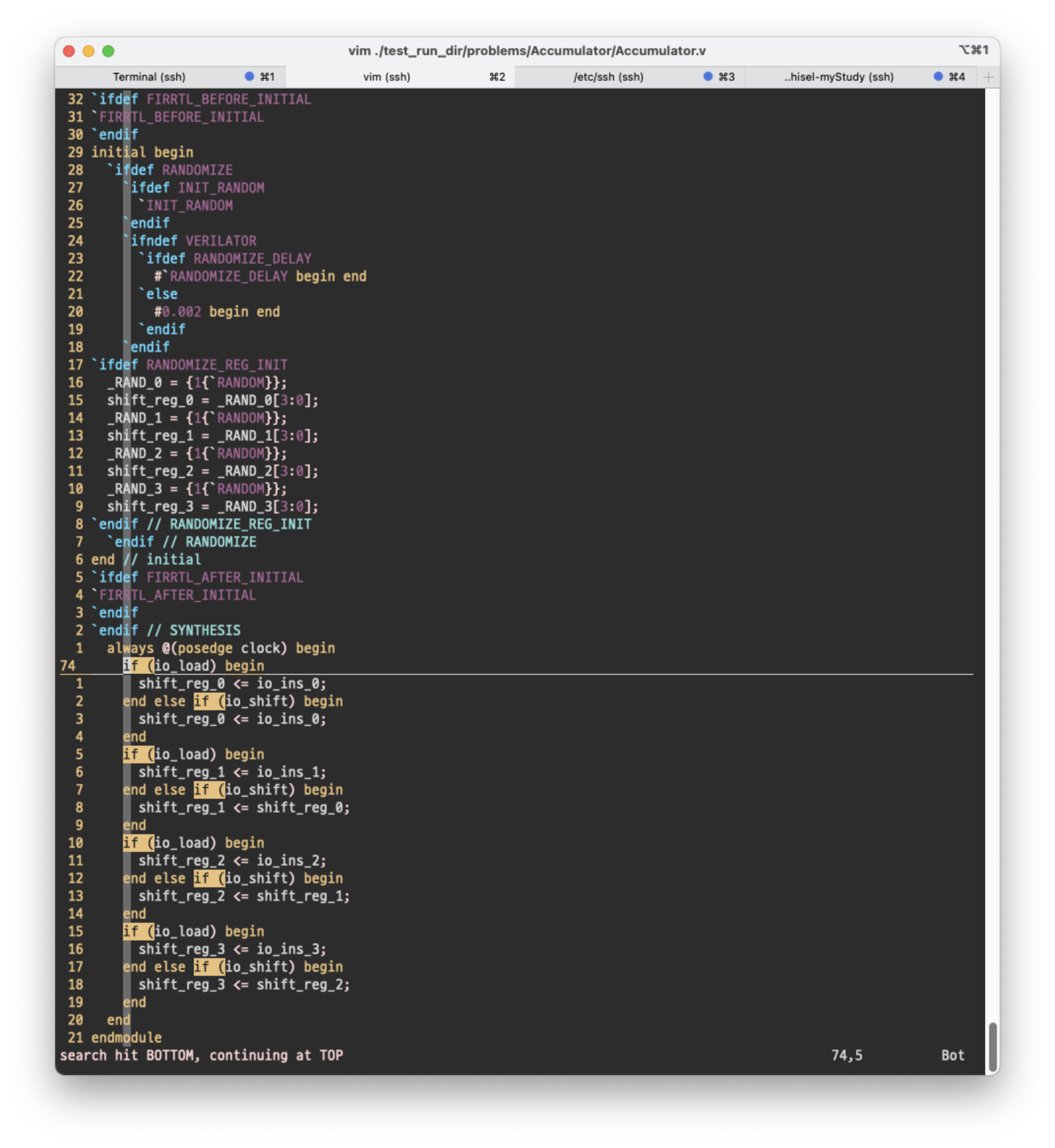

24.[chisel-tutorial] VecShiftRegister.scala: Vec 사용시, 구체적인 HW명을 명시하자

명령어 우선순위는 load가 shift보다 높다.load 입력시, ins 입력대로 내부 shift register가 전부 초기화된다.shift 입력시, 3<2 2<1 1<0 0<3 형식으로 한칸씩 밀려난다(leftshift).compile erro

25.[chisel-tutorial] VecShiftRegisterParam.scala: "Exception thrown when elaborating ChiselGeneratorAnnotation" 시, index 실수를 의심하자

기존의 VecShiftRegister와 거의 다른 점이 없어서, 금방 풀었다.랜덤한 입력을 쭉 넣는다.Array의 결과와 동일한지를 비교하는 TB이다.Exception이 제일 까다롭다..어디서 에러가 떴는지 정확하게 짚어주지 않는다.대충 이런 아주 긴 Excpetion

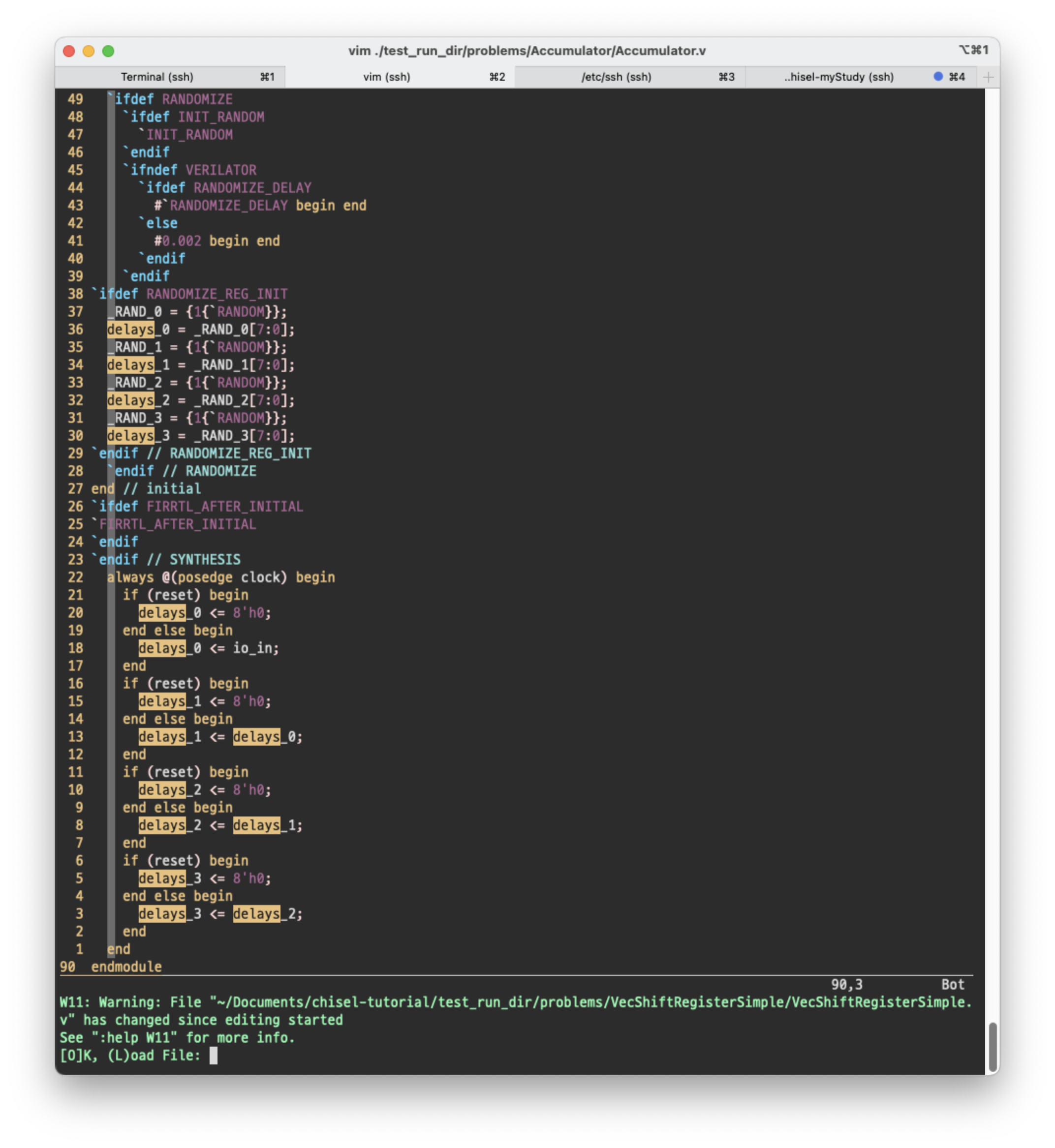

26.[chisel-tutorial] VecShiftRegisterSimple.scala: Seq 사용 - Seq.fill(4) { 0.U(8.W)}

VecShiftRegister.scala문제의 하위호환이다. 바로 풀었다. 다만, 참고할 점이 있었다. 풀이 Test Code 정답 What I learned Seq.fill하여 4*8을 만든 뒤, 해당 seq로 Vec을 만들고, 이걸로 RegInit을 하여

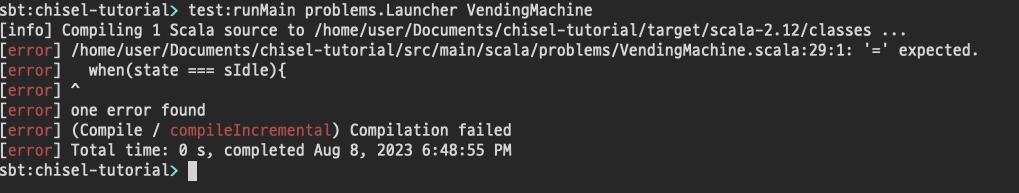

27.[chisel-tutorial] VendingMachine.scala: FSM 구현

Enum: Chisel3 cheatsheet 참조상태머신을 만드는 문제이다.Enum으로 state를 선언하고,moore로 짜면 될 것 같다.너무나도 당연히, state_nxt를 선언했고클럭마다 state가 state_nxt로 바뀌는걸 어떻게 해야할지는 모르겠어서,그냥냅

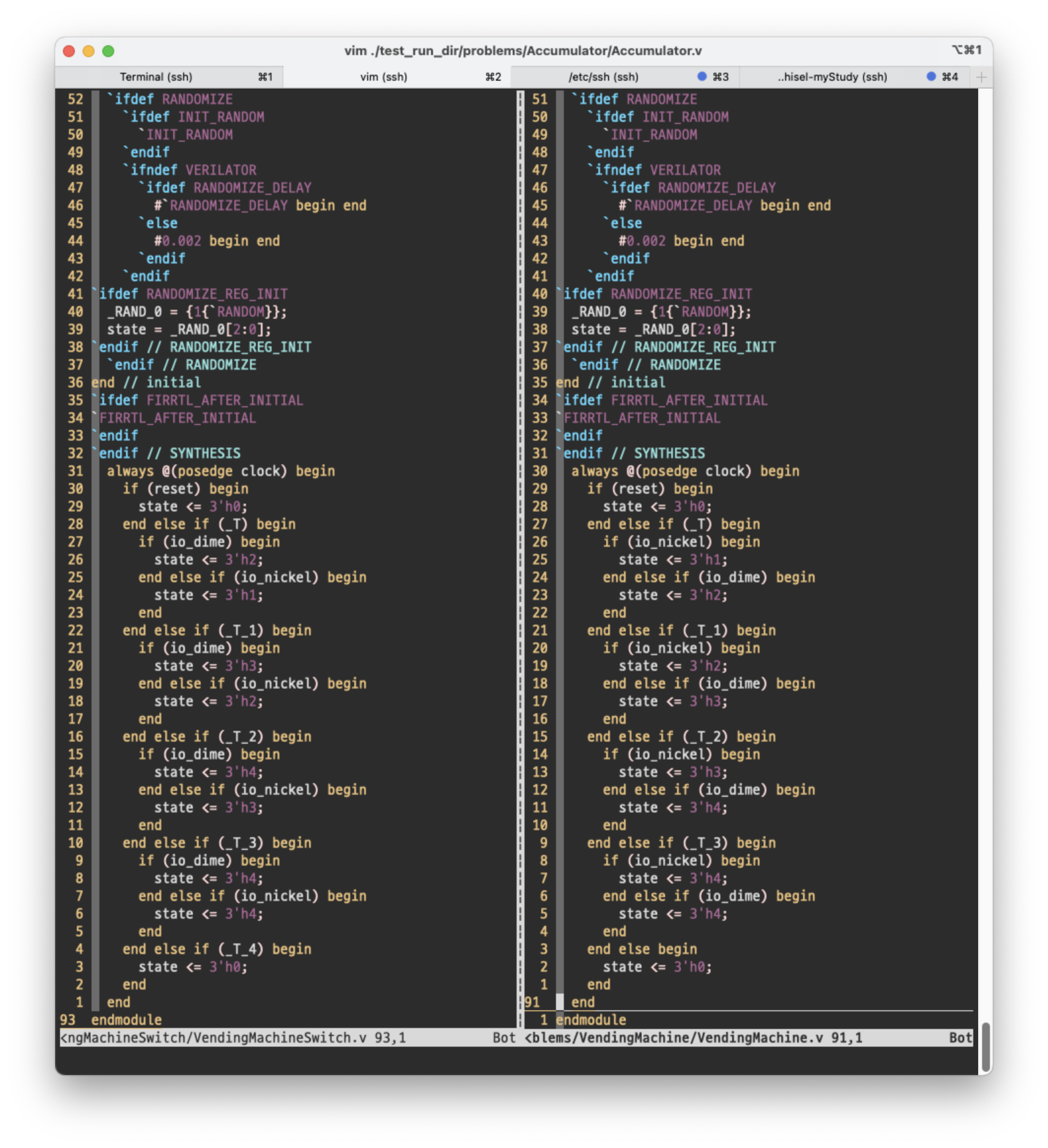

28.[chisel-tutorial] VendingMachineSwitch.scala: Switch 문으로 FSM 구현

FSM을 이번에는 when문이 아니라, switch문으로 구현하는 차이점 뿐이다.즉 간단하다.내부적으로 money 변수를 유지하고, 20 이상인지의 여부를 정답으로 생성하여Chisel 모듈의 답과 비교하는 간단한 테스트코드이다.실수가 있었다.sOk 상태에서는 무지성 s

29.[CSE 228A] Agile Hardware Design 학습계획

과정에 사용되는 Chisel Reference들Youtube 강의 재생목록총 20강,각 평균 대략 50분.chisel-tutorial을 통해 대충 어떻게 짜이는 언어인지 감만 잡은 상태이니,이 강의로 이론적 토대를 제대로 구축할 생각이다.자 드가자~

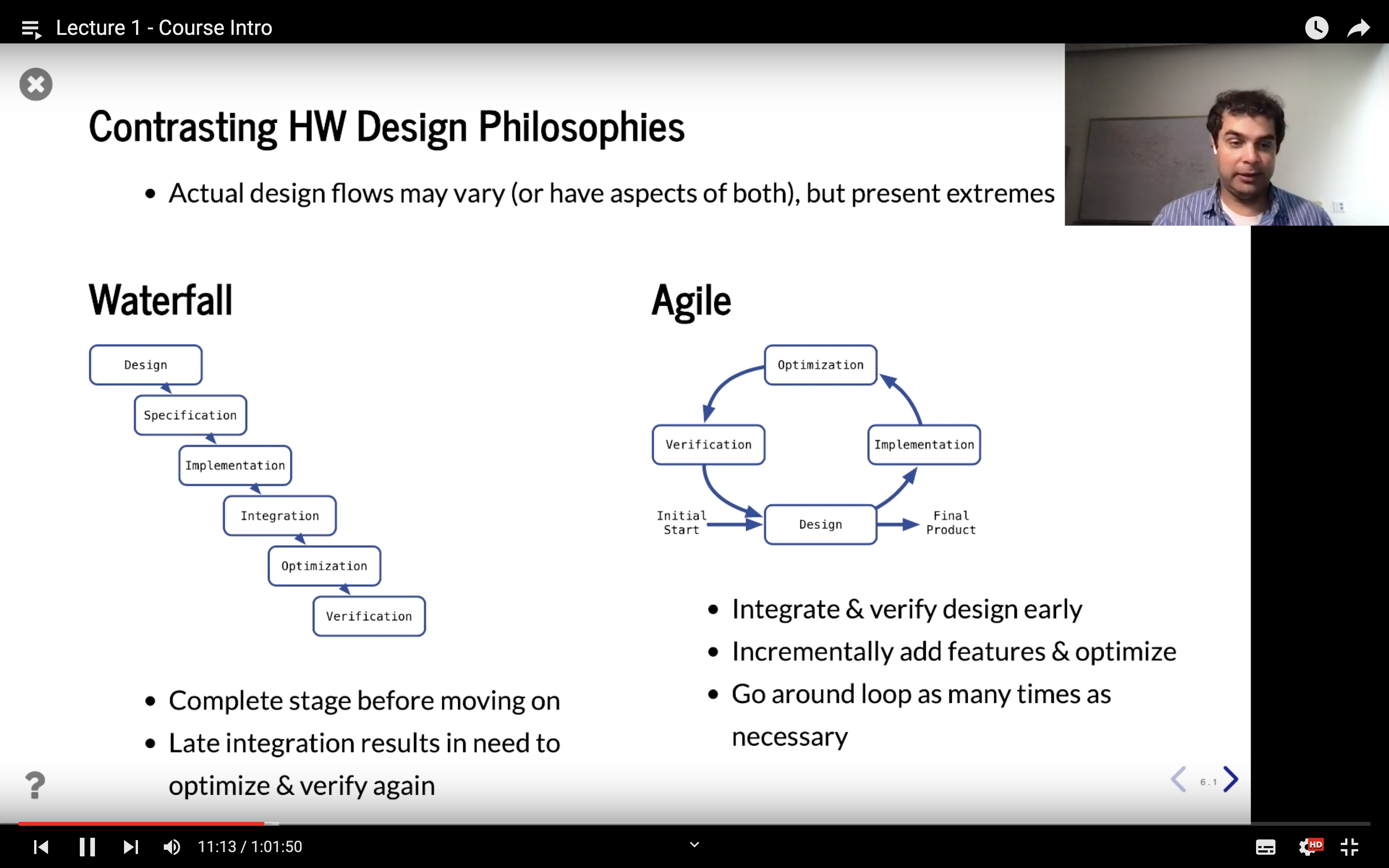

30.[CSE 228A] Lecture 1 - Course Intro

무어법칙이 지속되어도, transistor의 E효율 향상률은 낮아지고 있음.specialization을 통해서, 우리는 E효율을 올려야만 함Design에 점점 더 Advanced Technology Nodes가 필요함그렇다고 다양한 Advanced Tech를 전부 수용

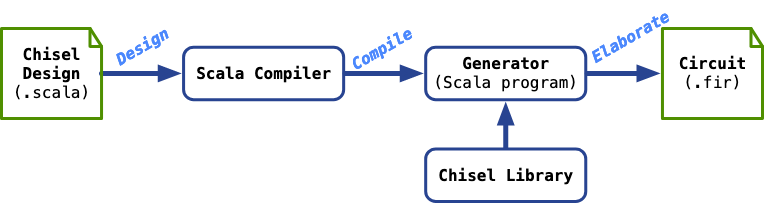

31.[CSE228A] Lecture 2 - Hello Chisel

Binder 링크OOP with strong static type systemfunctional programming도 가능JVM 위에서 돌아서, java binary와 inter-operate 가능Compile time에 여러 potential error를 잡아줌em

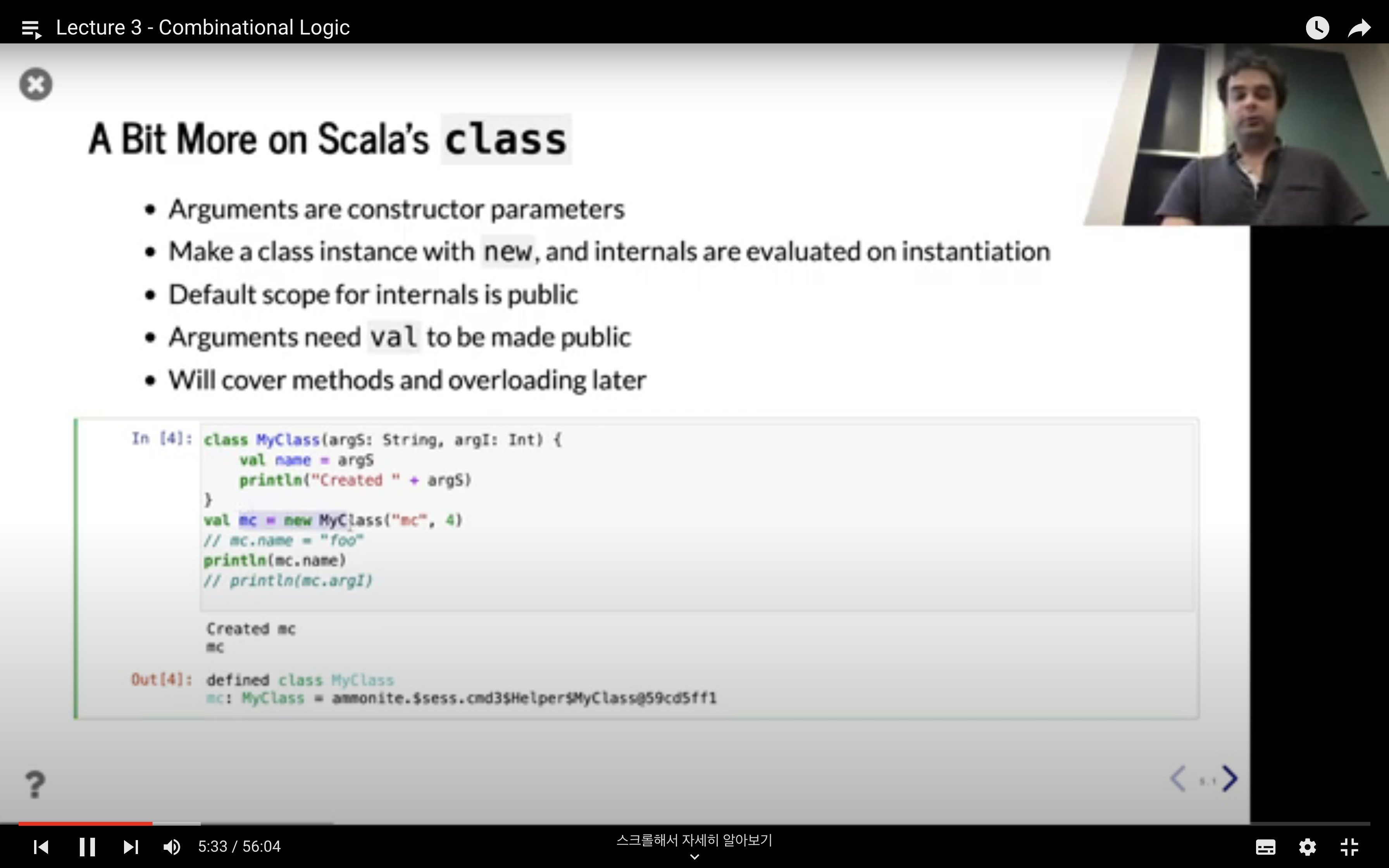

32.[CSE228A] Lecture 3 - Combinational Logic

출처Mux(select, in1, in0) 으로 선언가능Verilog/C의 ternary operator와 동일.MuxCase, Mux1H 등 여러 flavor가 존재함. 참고알다시피 Scala는 OOP다.로 선언해도, 클래스 자체는 된다.이것처럼, Class 생성시

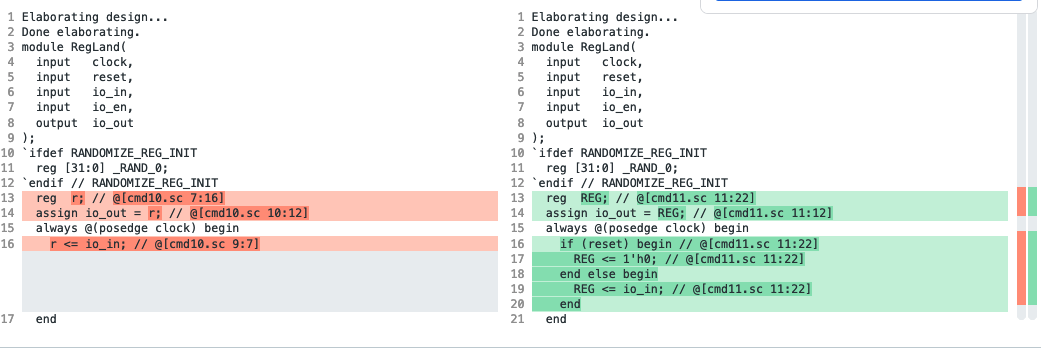

33.[CSE228A] Lecture 4 - Sequential Circuit

Lecture 4 - Sequential Circuit Registers Reg(type)로 명시적 선언해야함 Chisel은 반드시 명시적 Reg 선언을 요구한다는 점에서 Verilog와 다르다. Verilog의 경우, Register는 reg로 선언해도 물리적으

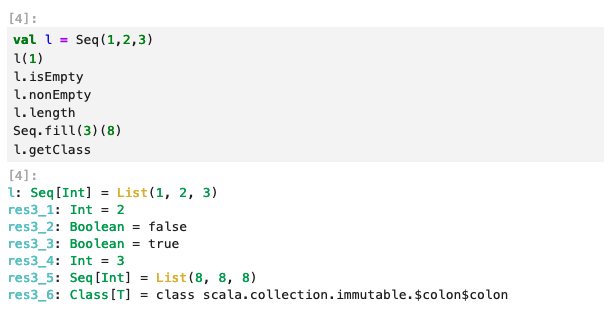

34.[CSE228A] Lecture 5 - Collections

Scala의 collection library에 있음Seq는 Ordered Collection이고, dafault값은 Immutable임.()로 인덱싱할 수 있음.List와 Vector를 사용하기를 권장하는 guideline도 있음Seq는 여러 자료형을 담을 수 있음.

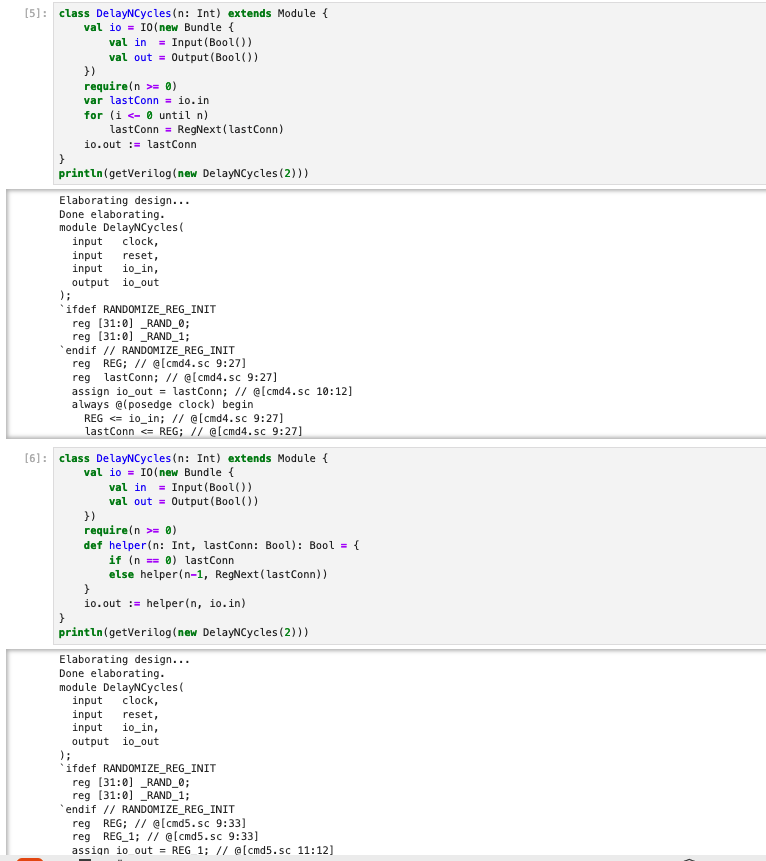

35.[CSE228A] Lecture 6 - Encapsulation

반복문으로 생성한 것과, 재귀적으로 생성한 것 모두 동일한 결과를 내는 것을 확인할 수 잇다.Singleton Object를 위해 만들어졌다.인스턴스가 단 하나만 존재하는 클래스를 위한 것.Shared stateStateless FunctionFactory Method

36.[CSE228A] Lecture 7 - Decoupling

Lecture 7 - Decoupling 강의 전의 의문 Valid, Decouple이 있더라도 결국 단순히 interface처럼, 선언 시의 편의만 제공하고 구체적인 Valid high, ready high시의 동작은 일일히 기술해야한다는 점은 똑같지 않을까?(잘 모

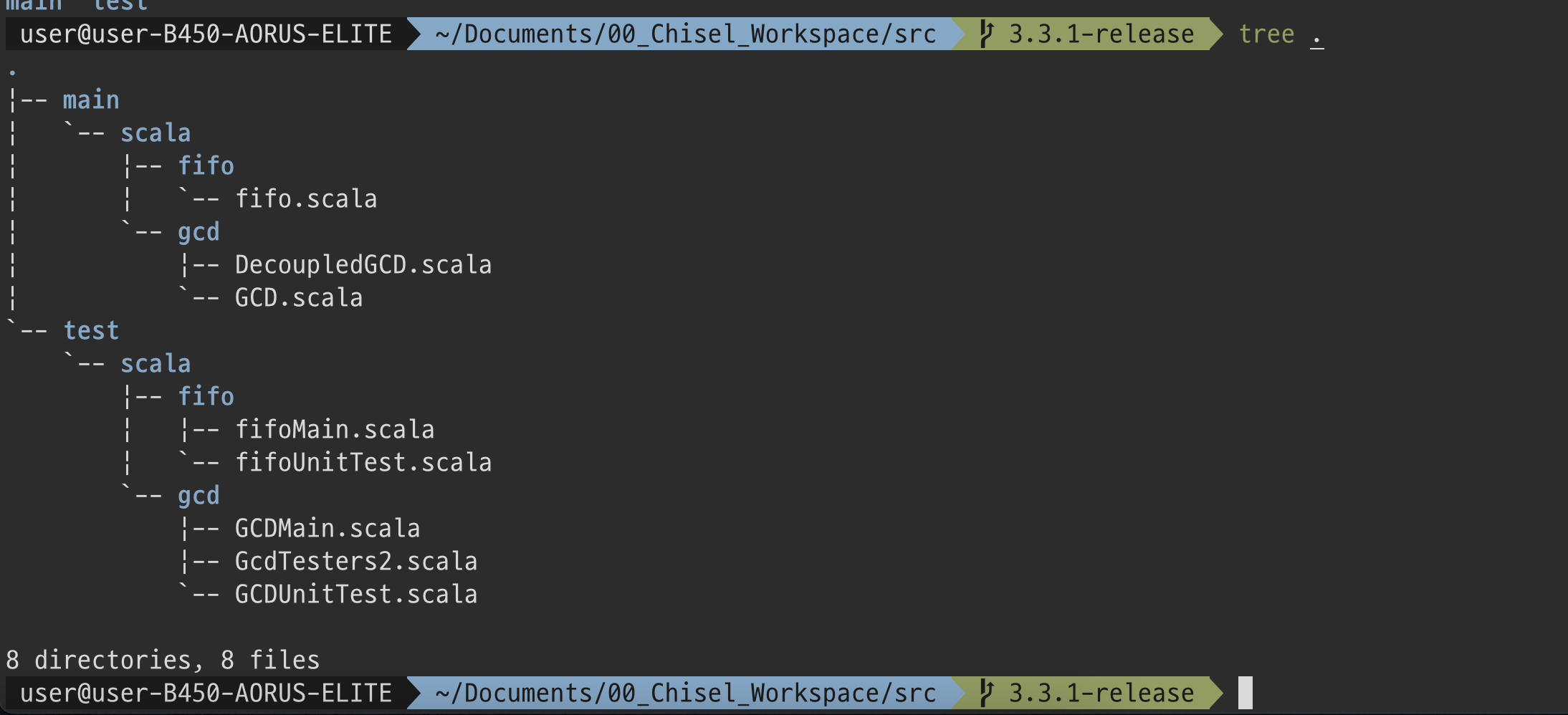

37.[chisel-template] Chisel을 통한 FIFO 설계 및 Chiseltest를 통한 testbench 작성

시간이 없어서, 간략하게 기술한다.자세한 설명은 시간이 날 때 적는 것으로.chisel-template로부터 generate한, 내 3.3.1-release branchfifo 하위에 scala 파일을 만듬.의도대로 동작함을 확인가능하다.

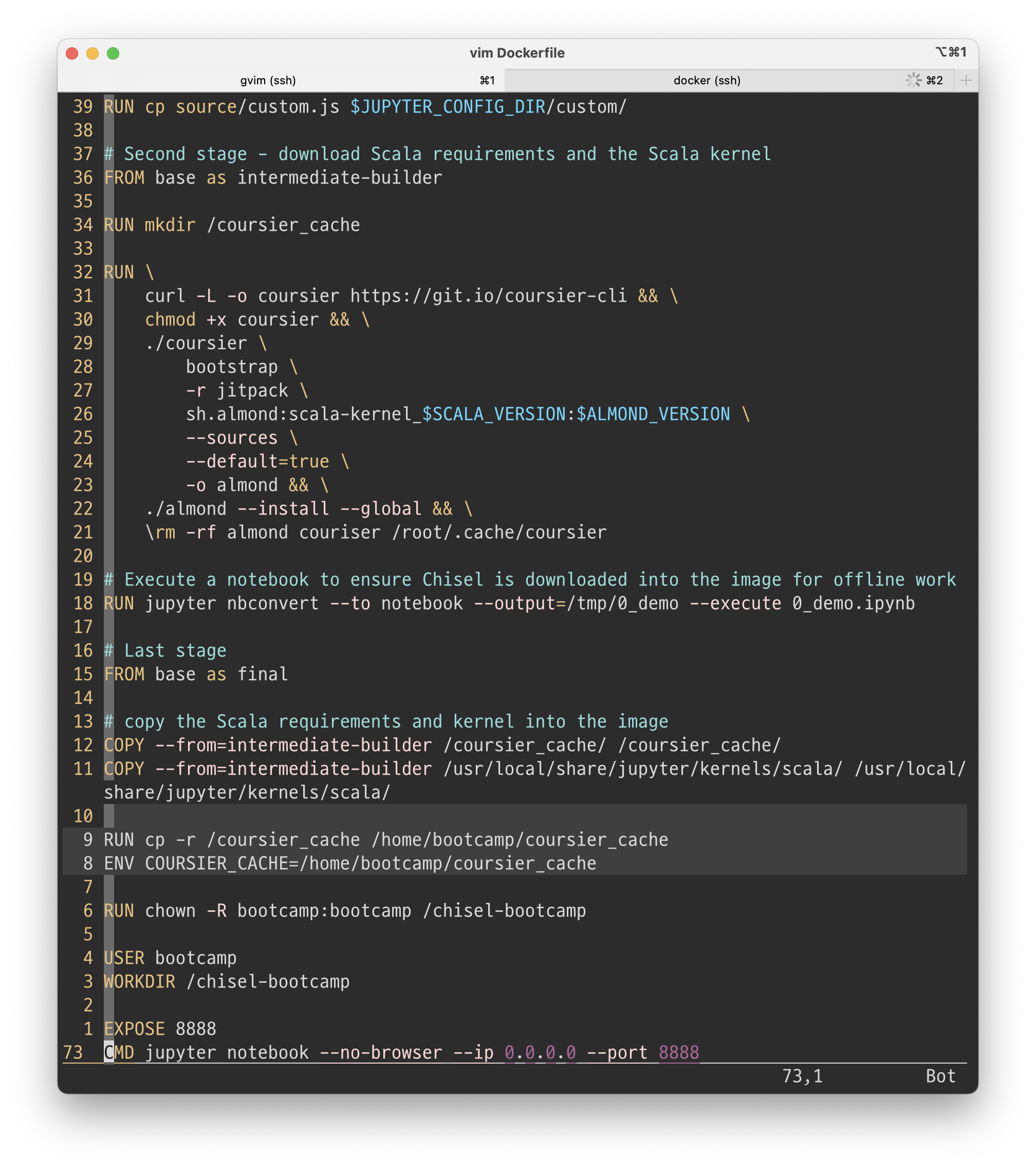

38.[chisel-tutorial] Failed to resolve ivy dependencies:/coursier_cache/.structure.lock (Permission denied) 해결

https://github.com/freechipsproject/chisel-bootcamp/issues/140를 참고했다.Makefile에 드래그한 부분을 추가.그 뒤, 실행하면 정상동작 확인가능하다.

39.RegInit 정리

자꾸 실수해서, 헷갈려서 정리한다.둘다가능하다.그러나는 불가능하다.

40.[ucb-bar chisel-tutorial] Multiple Clock Multiple Reset

변환결과

41.Decoupled Queue 생성

Flipped(Decoupled()) 및 entries를 입력으로 받는다.

42.(미완) Seq.fill과 Seq.tabulate 차이

출처일괄적으로 적용하여 Seq를 생성하는건 같은데,단순히 계산을 일괄적으로 적용하는지, index에 f(i)형식으로 적용하는지의 차이인듯.val taps = Seq.fill(tapSize)(r()) // create a sequence of random coeffic

43.[Learning Scala] 이름에 의한 호출 매개변수

결과doubles는 name에 의한 argument를 받았고,doubles2는 value에 의한 argument를 받았다.이 때, 전자의 경우는 함수가 정말 그대로 넘어가기 때문에(단순한 값이라면 후자와 동일하지만), evaluation될 때마다 해당 함수가 "호출"된

44.[Verilog 출력하기] circt 말고 chisel3 사용하기

공식문서 - Get me Verilog에서는, import circt.stage.ChiselStage를 한 뒤에,를 하라고 되어있는데, 나는 아무리 해도 되지 않았다.testbench 없이 소스코드로부터 바로 Verilog 뽑기를90분 삽질 끝에 겨우 성공하여(...)

45.[CPU自作] 공부시작: RISC-VとChiselで學ぶはじめてのCPU自作

책 링크알라딘에서 해당 책을 1달쯤 전에 직구하였는데,무지성 Verilog->Chisel로의 변환이 아니라,좀 더 OOP적이면서도 ChiselTest를 사용한 짜임새있는 개발방법을 공부하기 위해, 해당 책을 따라 공부하기로 하였다.