풀이

아주 간단한 문제다.

Mux2를 3개 써서 Mux4를 만들면 된다.

Test

// See LICENSE.txt for license details.

package problems

import chisel3.iotesters.PeekPokeTester

class Mux4Tests(c: Mux4) extends PeekPokeTester(c) {

for (s0 <- 0 until 2) {

for (s1 <- 0 until 2) {

for(i0 <- 0 until 2) {

for(i1 <- 0 until 2) {

for(i2 <- 0 until 2) {

for(i3 <- 0 until 2) {

poke(c.io.sel, s1 << 1 | s0)

poke(c.io.in0, i0)

poke(c.io.in1, i1)

poke(c.io.in2, i2)

poke(c.io.in3, i3)

step(1)

val out = if(s1 == 1) {

if (s0 == 1) i3 else i2

} else {

if (s0 == 1) i1 else i0

}

expect(c.io.out, out)

}

}

}

}

}

}

}

오답 1

// See LICENSE.txt for license details.

package problems

import chisel3._

// Example:

//

// This is example of multiplexer 2-to-1 with 'sel' as control signal

// Multiplexed inputs are 'in0' and 'in1'

//

class Mux2 extends Module {

val io = IO(new Bundle {

val sel = Input(UInt(1.W))

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val out = Output(UInt(1.W))

})

io.out := (io.sel & io.in1) | (~io.sel & io.in0)

}

// Problem:

//

// Build a 4-to-1 multiplexer out of three 2-to-1 multiplexers

// The first multiplexer is already done for you

//

class Mux4 extends Module {

val io = IO(new Bundle {

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val in2 = Input(UInt(1.W))

val in3 = Input(UInt(1.W))

val sel = Input(UInt(2.W))

val out = Output(UInt(1.W))

})

val m0 = Module(new Mux2())

m0.io.sel := io.sel(0)

m0.io.in0 := io.in0

m0.io.in1 := io.in1

//Implement below ----------

val m1 = Module(new Mux2())

m1.io.sel := io.sel(0)

m1.io.in0 := io.in2

m1.io.in1 := io.in3

// make the compile process happy, needs to be substituted by the output of the Mux

val m2 = Module(new Mux2())

m2.io.sel := io.sel(1)

m2.io.in0 := m0.io.out

m2.io.in1 := m1.io.out

//Implement above ----------

}

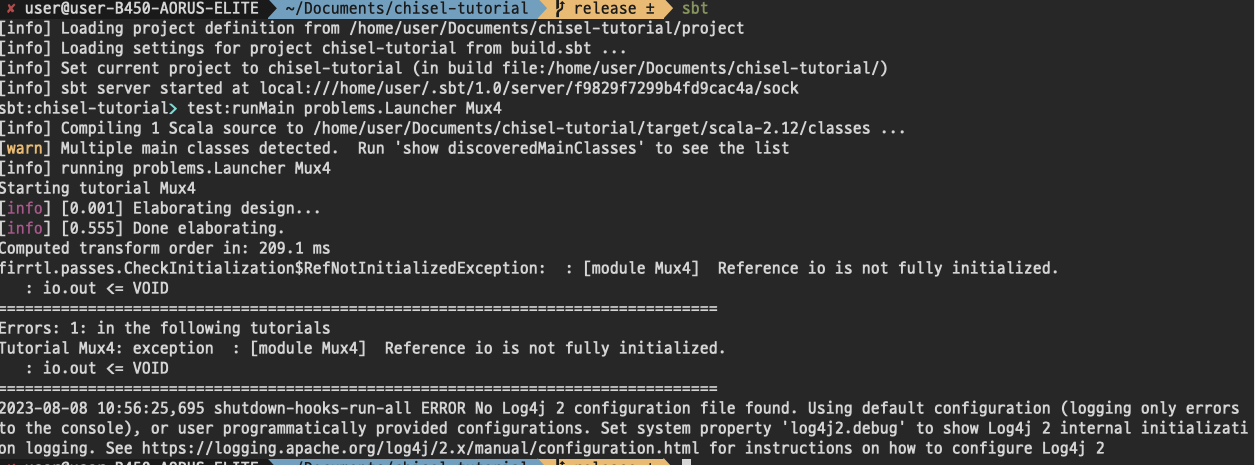

에러발생

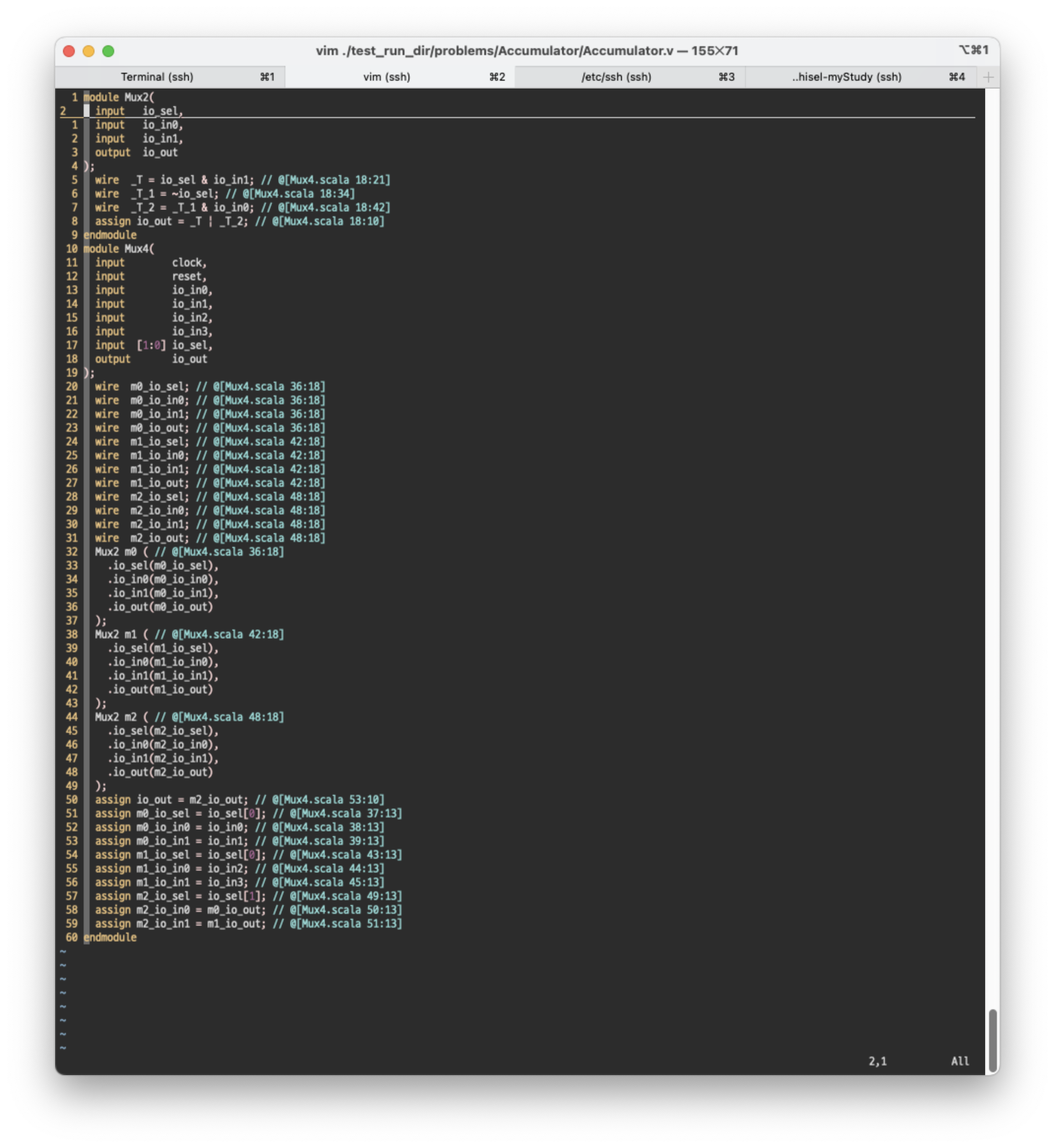

어 뭐가 문젠데? 근데 elaborate는 되었네? .v나 봐볼까?

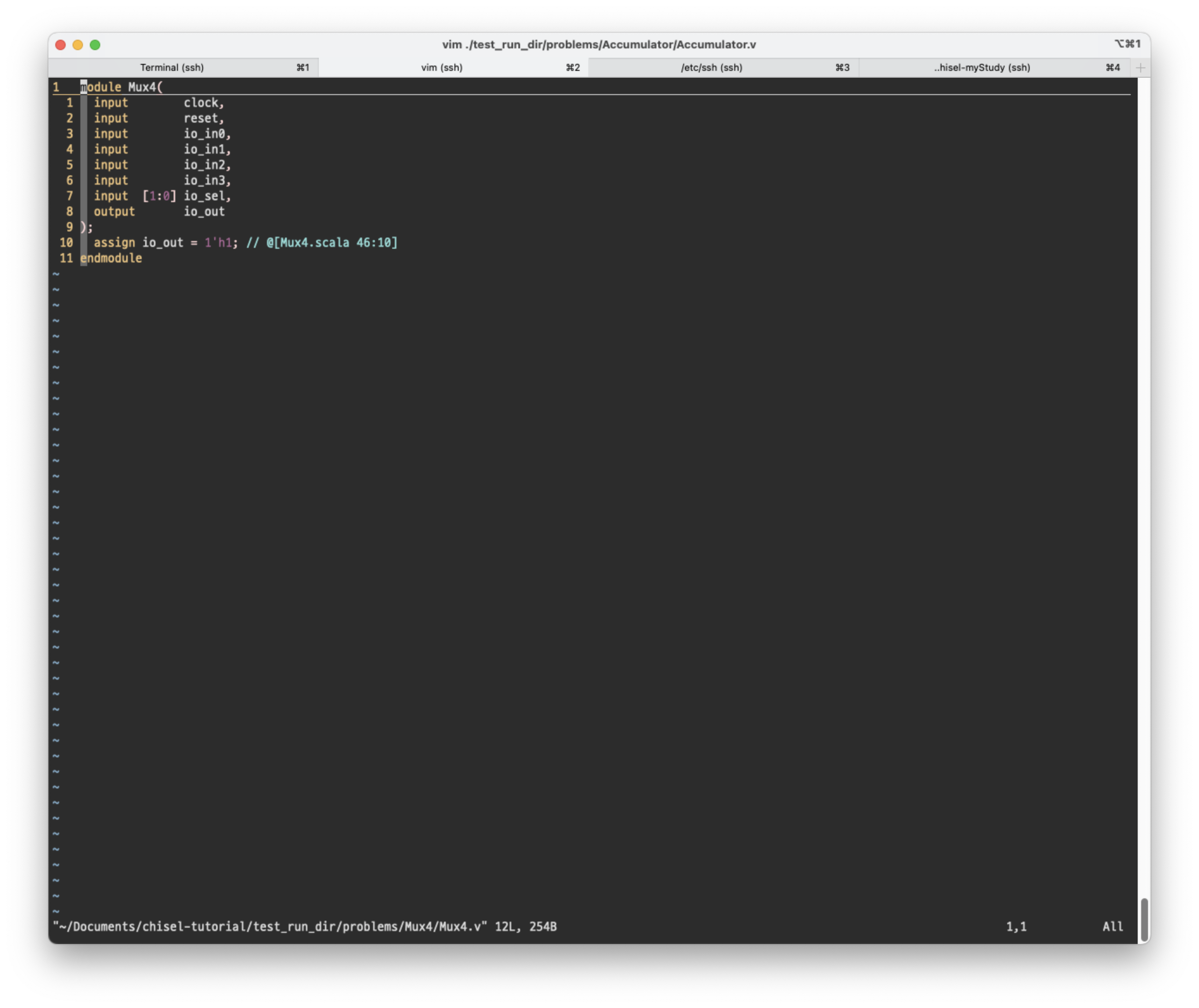

헉

출력이 그냥 hardwire잖아?

- 왜 1로 hardwire 되어있을까?

- 당연하다. io.out := 이 없으니까.

- 근데, x로 hardwire이 아니라 자기멋대로 1로 hardwire하네..?

정답

// See LICENSE.txt for license details.

package problems

import chisel3._

// Example:

//

// This is example of multiplexer 2-to-1 with 'sel' as control signal

// Multiplexed inputs are 'in0' and 'in1'

//

class Mux2 extends Module {

val io = IO(new Bundle {

val sel = Input(UInt(1.W))

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val out = Output(UInt(1.W))

})

io.out := (io.sel & io.in1) | (~io.sel & io.in0)

}

// Problem:

//

// Build a 4-to-1 multiplexer out of three 2-to-1 multiplexers

// The first multiplexer is already done for you

//

class Mux4 extends Module {

val io = IO(new Bundle {

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val in2 = Input(UInt(1.W))

val in3 = Input(UInt(1.W))

val sel = Input(UInt(2.W))

val out = Output(UInt(1.W))

})

val m0 = Module(new Mux2())

m0.io.sel := io.sel(0)

m0.io.in0 := io.in0

m0.io.in1 := io.in1

//Implement below ----------

val m1 = Module(new Mux2())

m1.io.sel := io.sel(0)

m1.io.in0 := io.in2

m1.io.in1 := io.in3

// make the compile process happy, needs to be substituted by the output of the Mux

val m2 = Module(new Mux2())

m2.io.sel := io.sel(1)

m2.io.in0 := m0.io.out

m2.io.in1 := m1.io.out

io.out := m2.io.out

//Implement above ----------

}

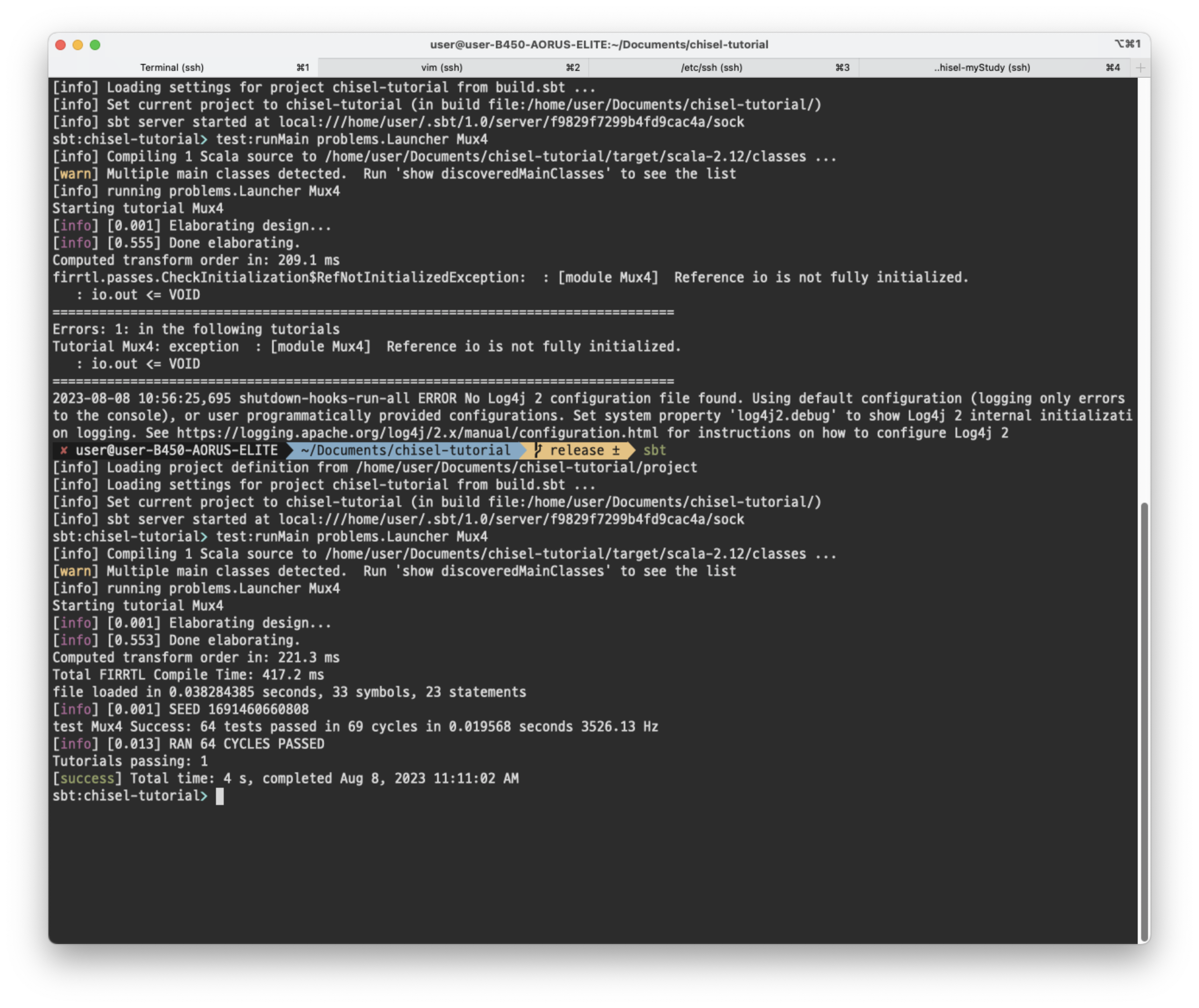

통과했다.

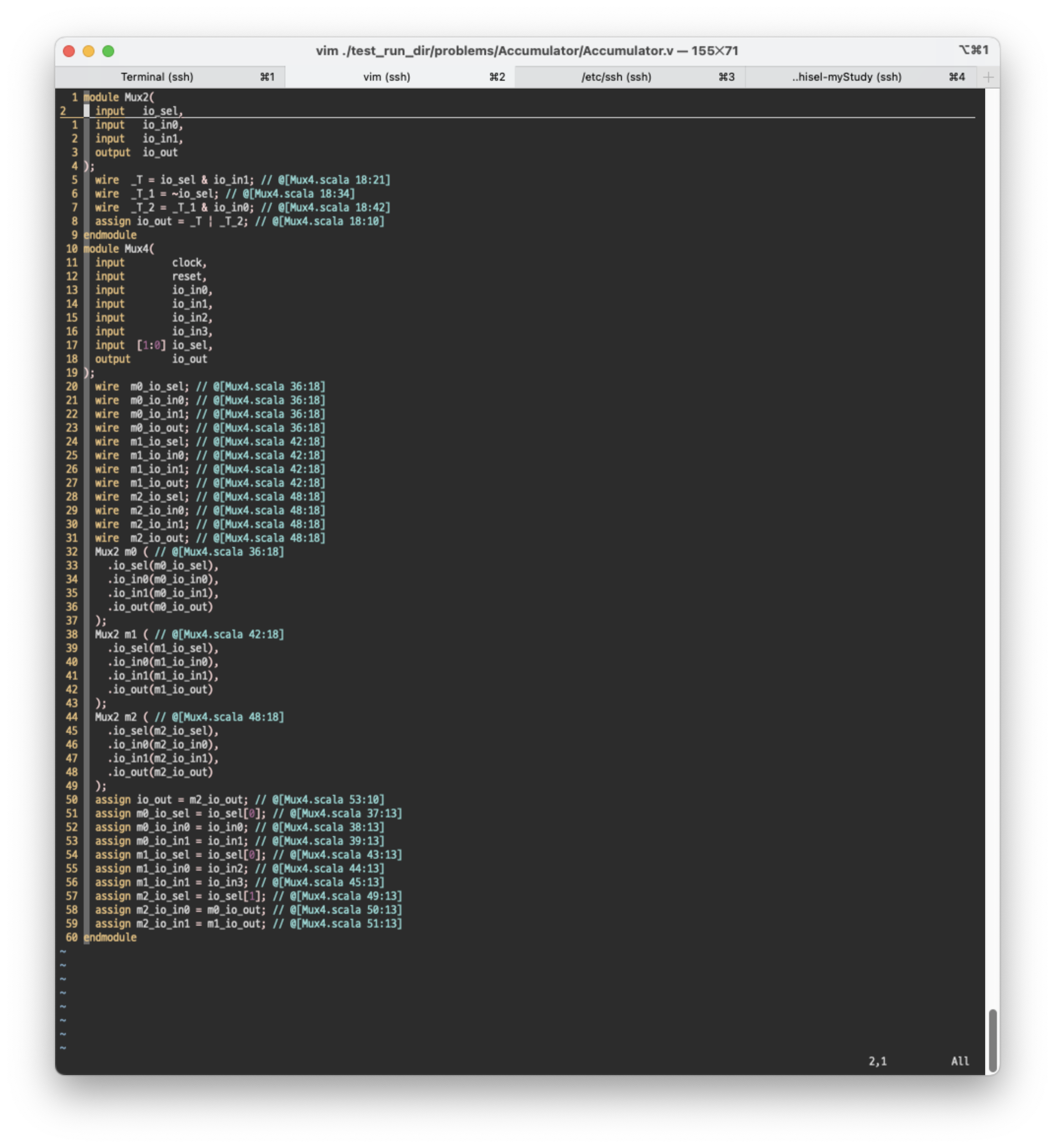

Chisel 상에서 new로 생성한 모듈들이,

Verilog 코드상에서 잘 instantiate 된 것을 확인할 수 있다.

What I learned

- 모듈 또한 val로 선언가능하다.

val m0 = Module(new Mux2())

로 new를 선언하면 된다.

정확히는,

코드를 선언하여 Class 정의를 해주고,class Mux2 extends Module { val io = IO(new Bundle { val sel = Input(UInt(1.W)) val in0 = Input(UInt(1.W)) val in1 = Input(UInt(1.W)) val out = Output(UInt(1.W)) }) io.out := (io.sel & io.in1) | (~io.sel & io.in0) }

아래 Class 내에서 마음껏 new 해서 만들어주면 된다.