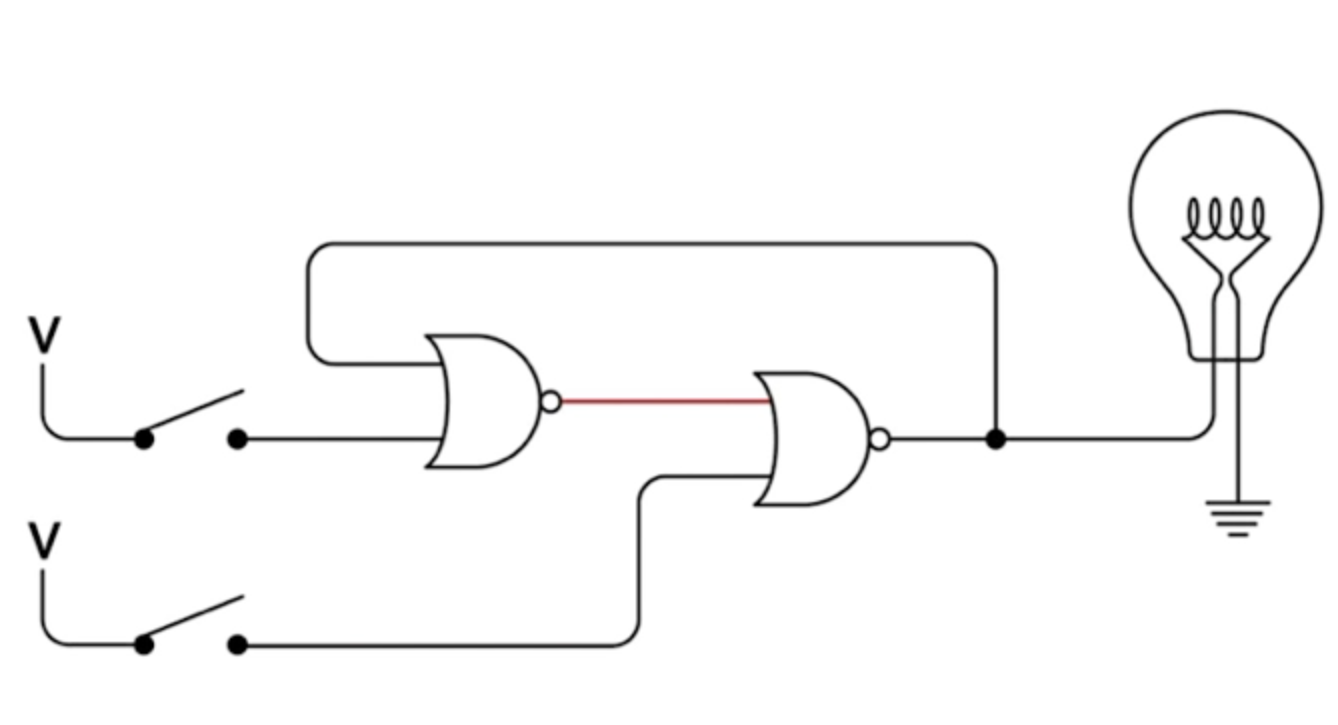

플립플롭(flip-flop)

1비트 데이터를 저장하는 논리회로

NOR게이트, NAND게이트로 만들 수 있다.

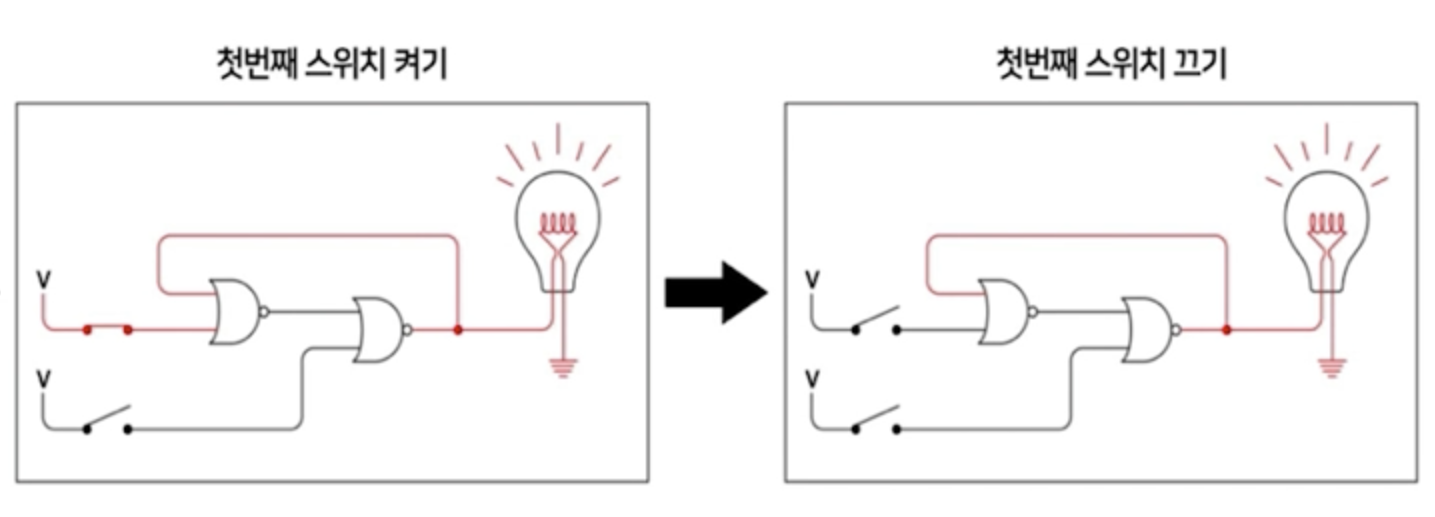

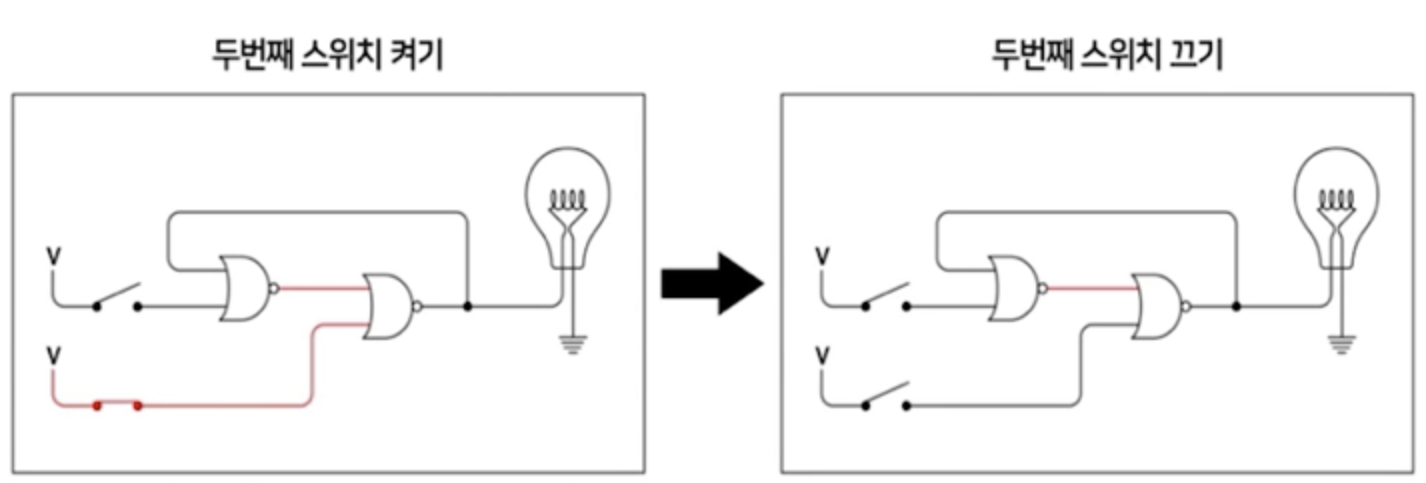

불이 켜져있다.

⇨ 첫번째 스위치가 켜졌었다.

불이 꺼져있다.

⇨ 두번째 스위치가 켜졌었다.

플립플롭의 종류

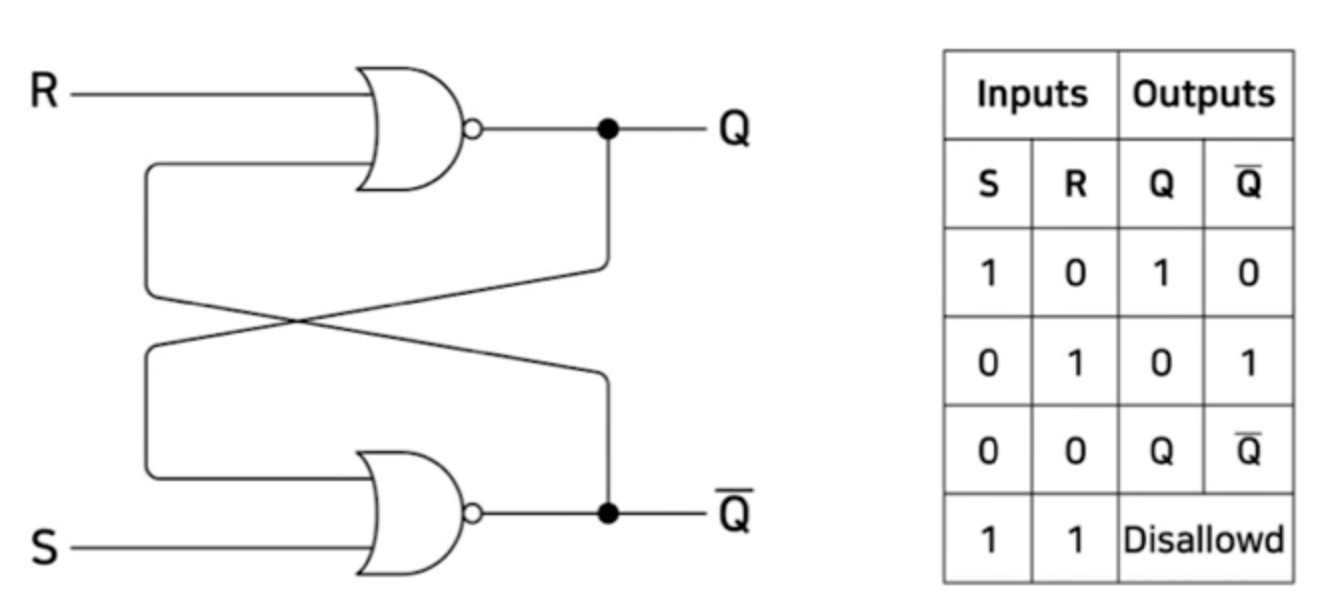

RS플립플롭(Reset-Set)

- Q = output

- /Q = Q의 반대값

- 단, S와 R이 1인 상태는 피하도록 설계 (Q 나 /Q 둘 다 0이 되므로

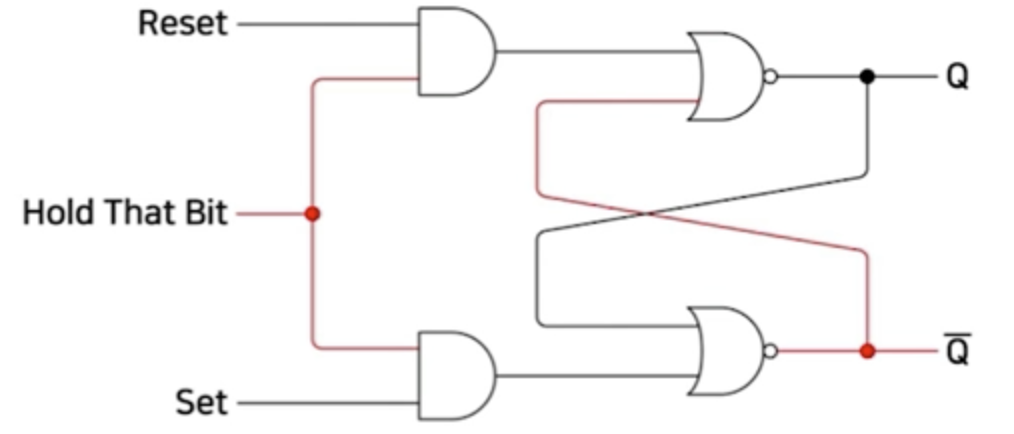

Hold That Bit

Hold That Bit가 1이 아니면 and게이트로 묶인 reset set이 변경되지 않기 때문에 클럭을 조절하는 역할로 Level-triggered flip-flop 이라고 한다.

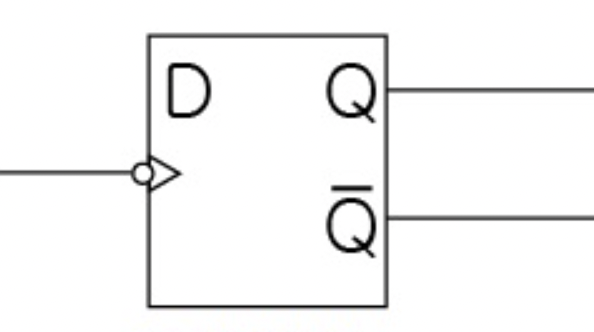

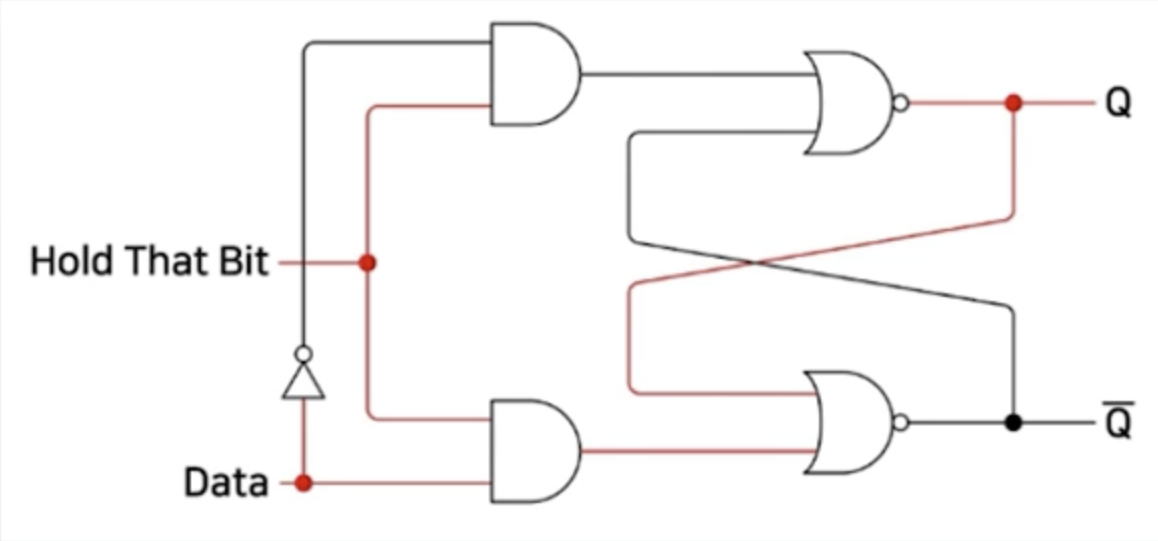

D플립플롭(Data)

Reset-Set을 Data 로 합치고 한 방향에 not게이트를 붙여 동시에 1이 나오지 않게 해두었다.

Level-triggered D-type flip-flop

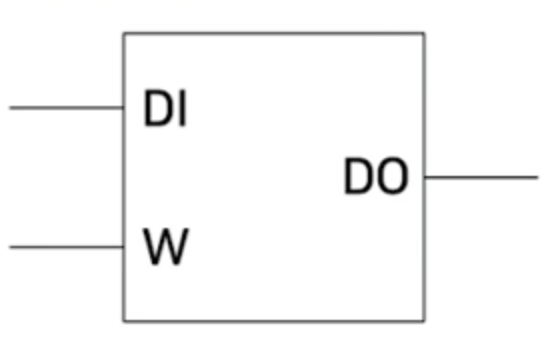

메모리 부품인 flip-flop. 1bit latch 래치 라고 한다.

1bit latch

1bit를 일시적으로 저장할 수 있는 메모리

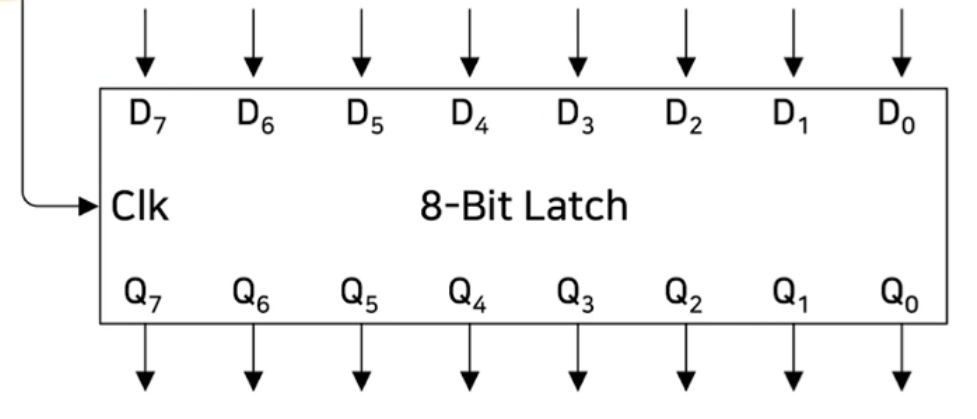

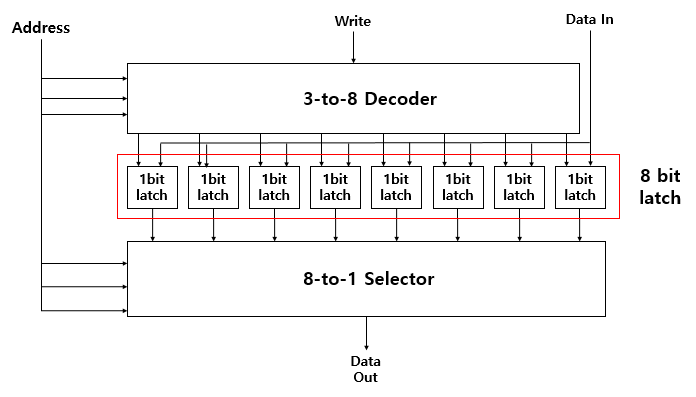

8bit latch

1bit latch가 8개 있는 것으로

Write가 1일때 8개의 DataInput이 DataOutput에 저장된다.

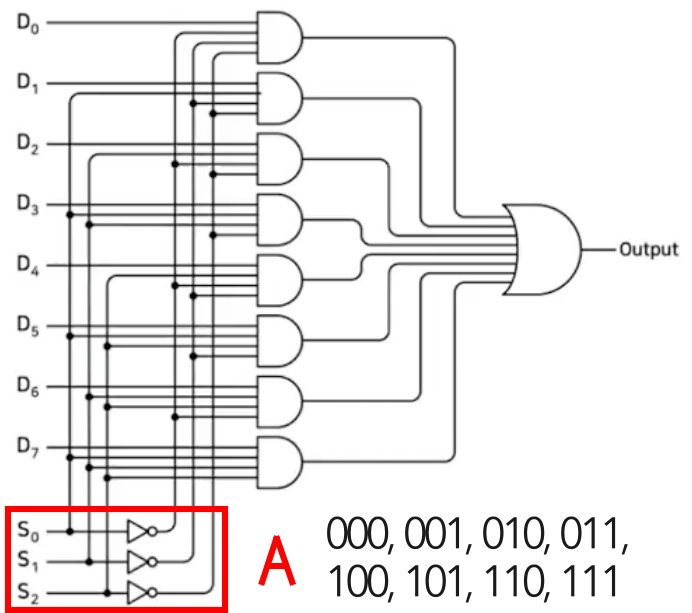

8-to-1 selector

데이터를 저장했으면 읽어올 수도 있어야 한다.

데이터를 저장할 때는 변수의 값은 데이터가 저장된 특정 주소를 가리킨다.

8-to-1 selector는 8개의 1bit latch 중에 하나의 데이터 출력신호를 선택하여 확인할 수 있다.

Switch 1~3을 통해 8개의 Unique한 신호를 보내고

이 신호가 Data 0~7에 도달하여

총 4개의 회선이 합쳐져 AND게이트로 1이 되게 되면

해당 Data가 output으로 나오게 된다.

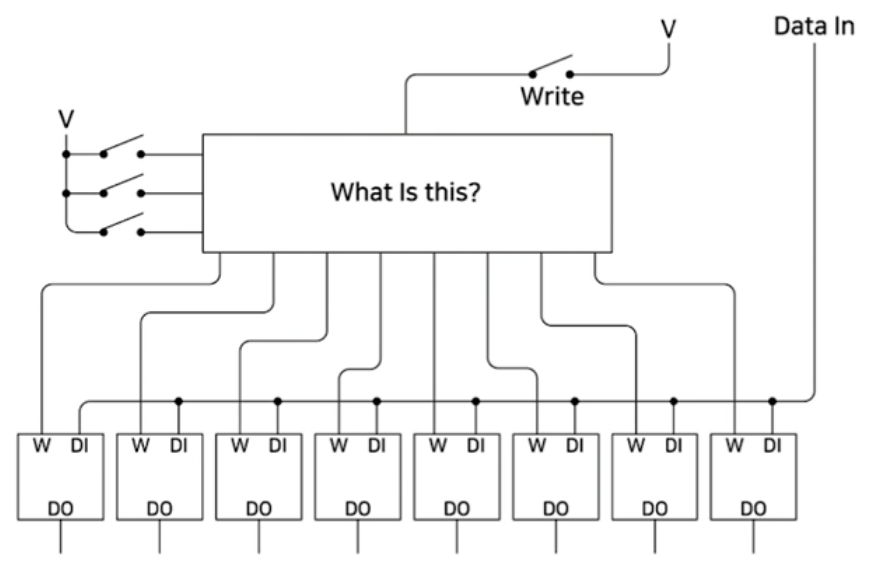

3-to-8 decoder

3개의 입력(Switch)가 있고 1개의 Wirte 를 갖고 있다.

즉 읽기와 쓰기가 동시에 되는 메모리이다.

8bit latch 회로 = RAM

온전한 8bit latch 회로는

3-to-8 decoder 와 8-to-1 selector로 구성되어 있다.

이게 주소, Adress이다.

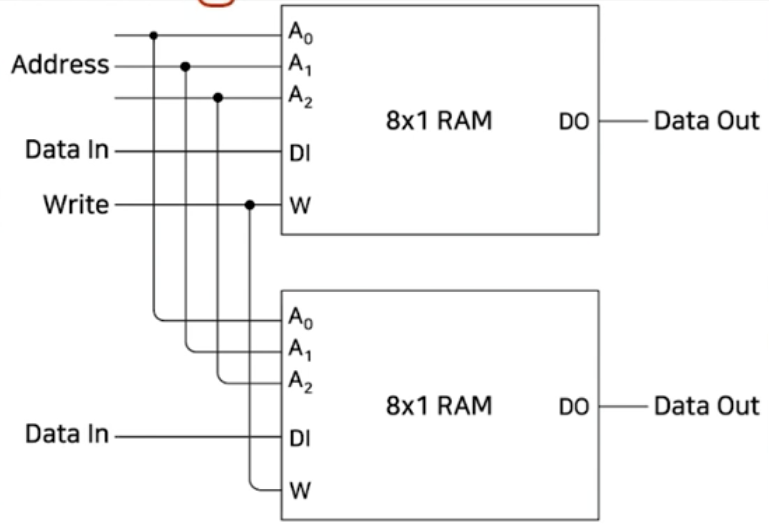

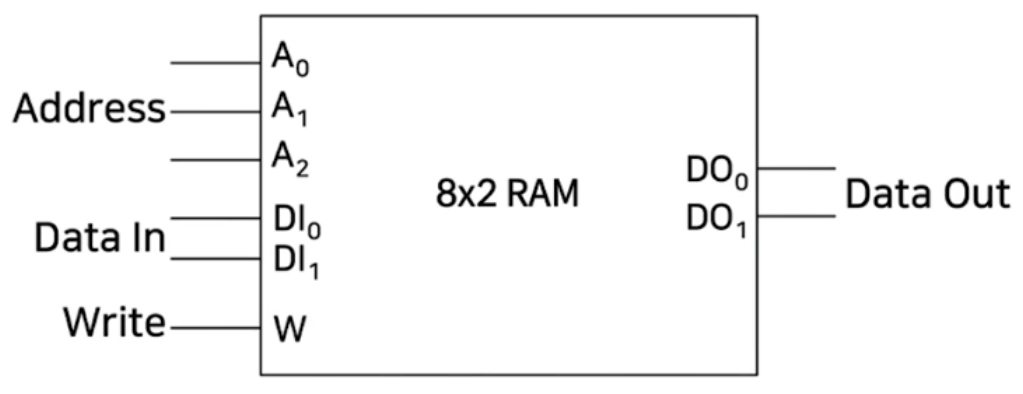

RAM(Random Access Memory) Array

8 x 1 RAM을 2개 두면 8 x 2 RAM이 된다.

8개의 데이터를 저장하고 읽을 때, 각 데이터는 2bits를 갖는다.

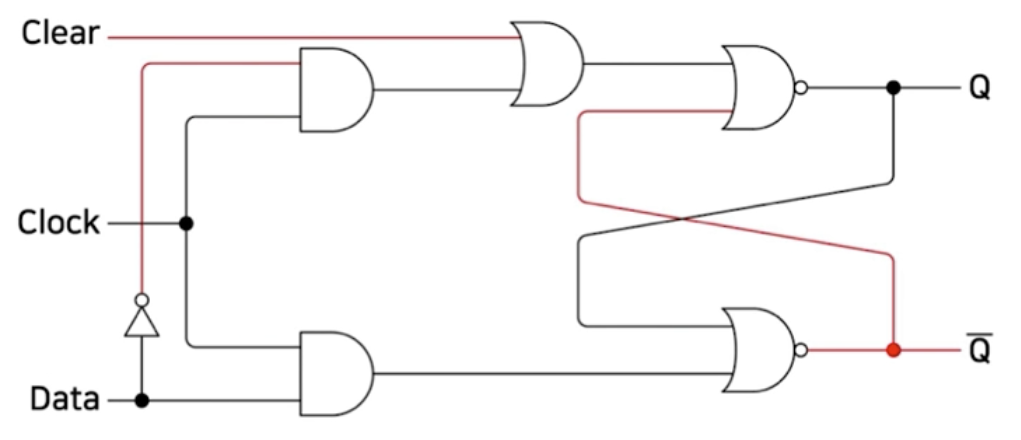

Accumulator(가산기)

clear 입력을 추가함.

clear = 1 이면 Q = 0

Data에 어떤 입력이 오든 clear가 입력되면 output값이 삭제된다.

clear를 1로 만들어거 기존값을 초기화하고

A데이터를 넣고 Add

B데이터를 넣고 또 Add를 누르면

결과적으로 A + B 가 된다.

이 Accumulator 가산기가 CPU에 들어있다

가산기를 보면 A를 임시로 저장할 공간이 필요한데 이곳을 "레지스터" 라고한다.

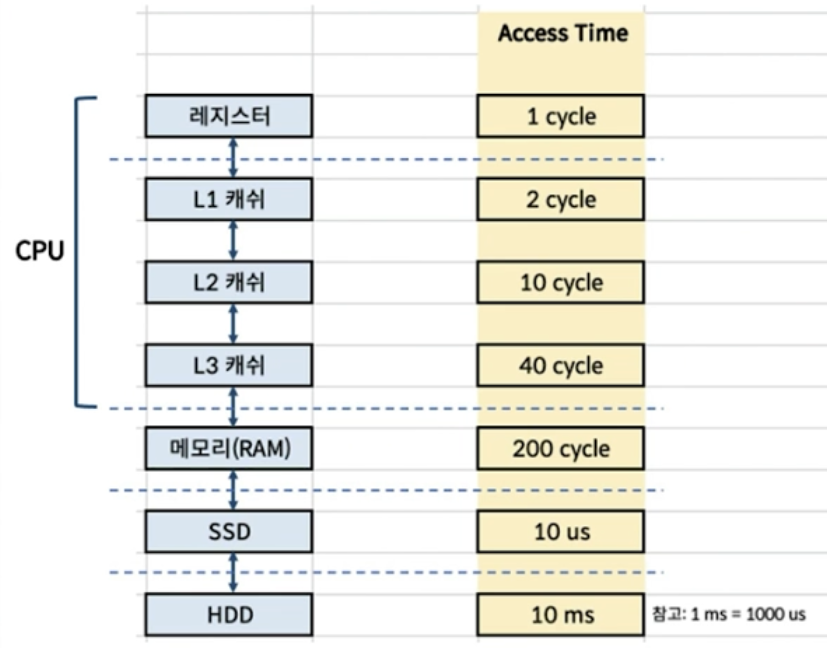

*레지스터

cpu가 요청을 처리하는데 필요한 데이터를 일시적으로 저장하는 기억장치

32bit data, 64bit data 하나의 데이터만 넣을 수 있는 공간인 레지스터가 여러개 있다고 할 수 있다.

1cycle

*어셈블리어 Assembly

기계어. cpu에 가장 가깝게 명령을 내릴 수 있는 언어

- 이전까지 Oscillator로 클럭을 만들었듯이

Flip-Flop으로 Memory-CPU 가산기를 만들었다.

Program Counter (PC)