Processor

1) CPU Pipelining

-

3-stage pipelining

-

superscalar

-

커널모드, 유저모드 둘 다 제공해야

-

System call

: Trap

→ user mode에서 수행시 user mode → kernel mode로 뛰고 특정 주소지의 명령어 실행 -

Registers

: program counter, stack pointer, general purpose register, program status word (PSW)

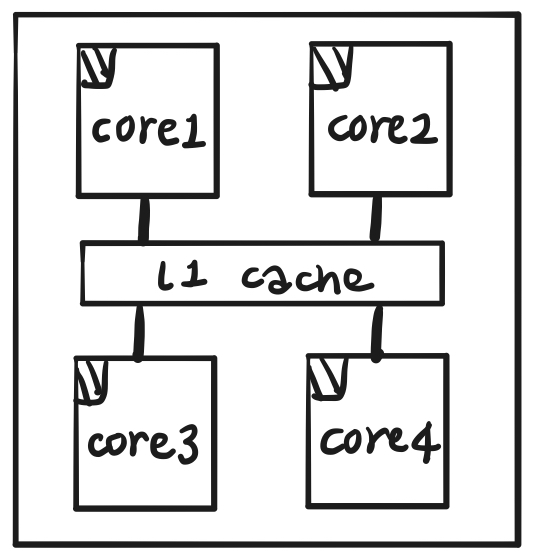

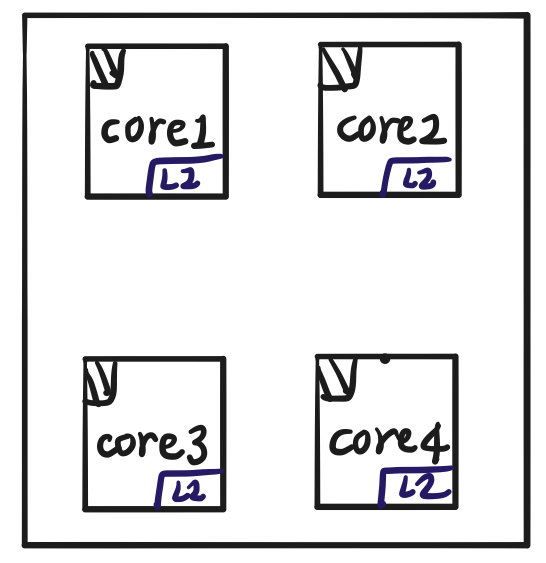

2) Multithread & Multicore chip

(i) L2 cache 공유

(ii) 각 CPU가 L2 따로

: CPU 두개가 서로 다른 thread 상태를 갖게 하여 nanosecond 단위에서 왔다갔다 할 수 있도록

→ 병렬성 제공 x

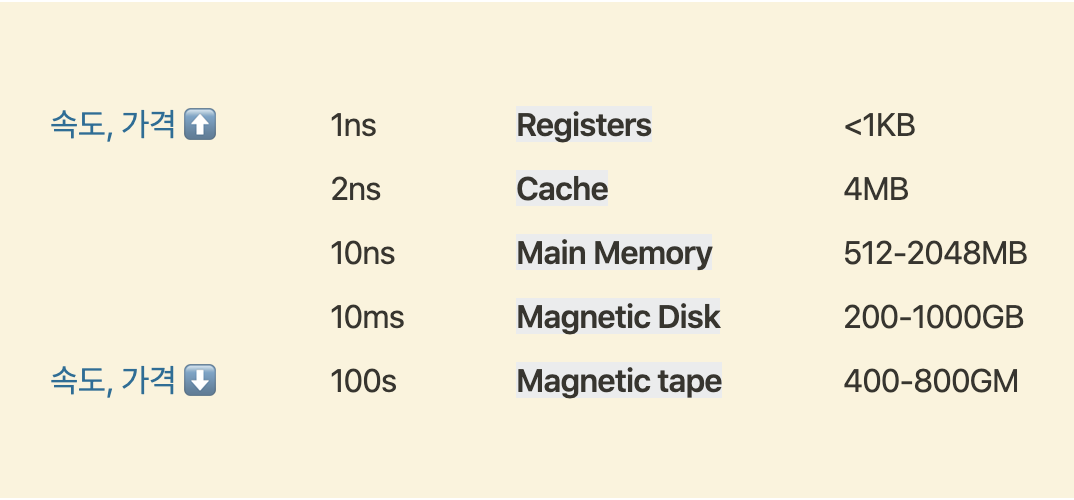

Memory

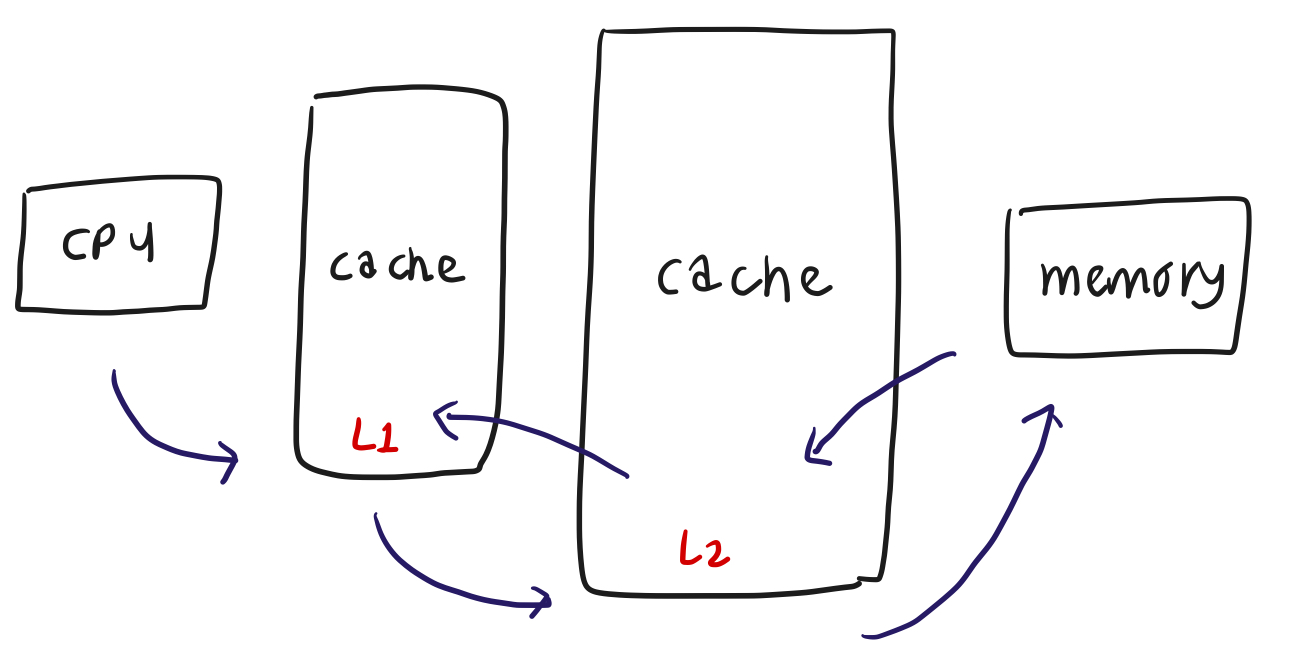

1) Cache

: main memory에 64B 크기의 cache line 존재

e.g. 주소 0~주소 63 : 캐시라인 0, 주소 64~주소 123: 캐시라인 1

-

L1 cache

: CPU 안에, decode된 명령들 제공시 -

L2 cache

: 최근 사용 memory 워드 수를 MB단위로 저장

2) Main Memory

→ 보통 RAM (Random Access Memory)

- ←→ 비휘발성 메모리

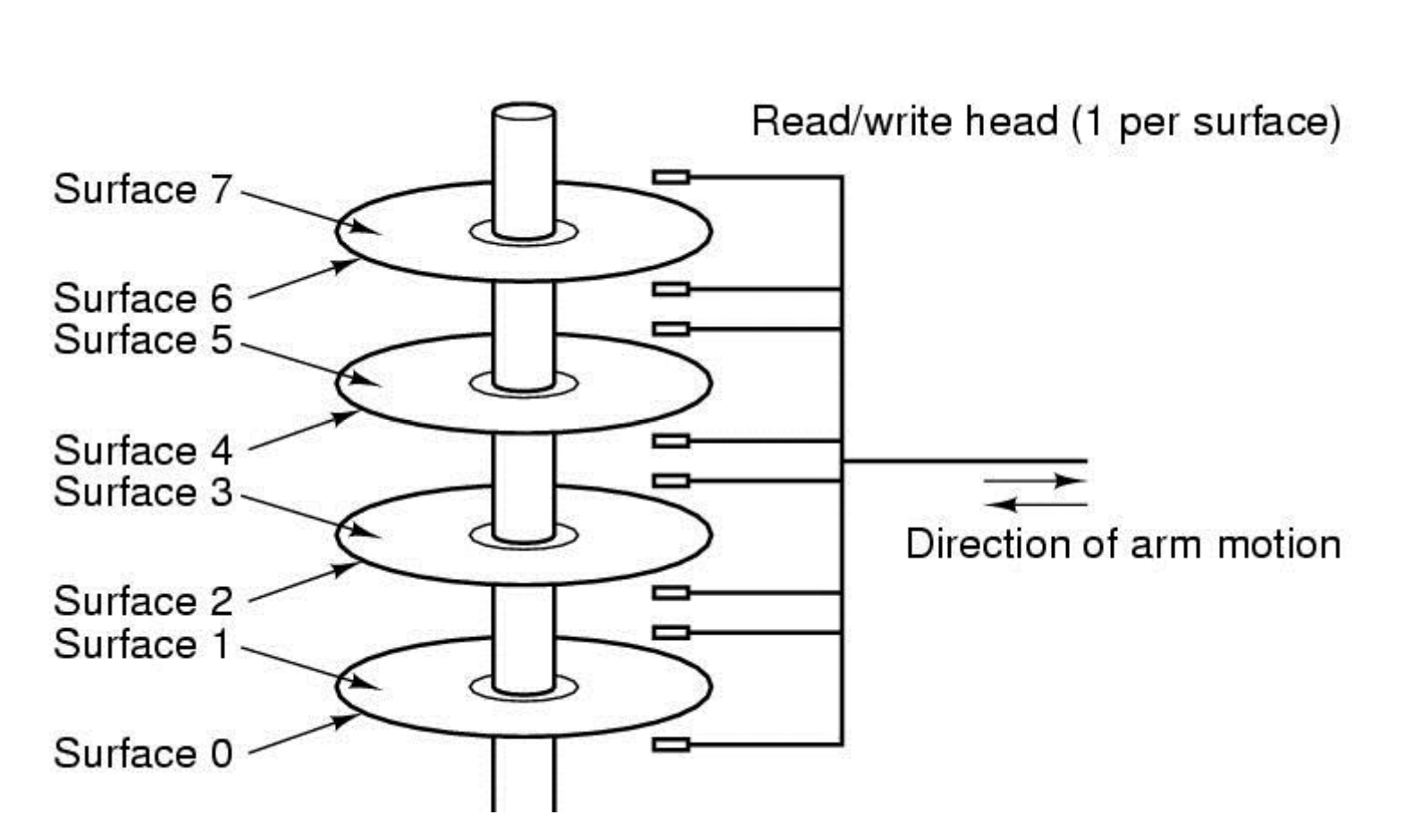

Disks

-

virtual memory : 물리메모리보다 더 큰 프로그램 적재시

→ MMU (memory management unit)이 담당 -

context switch

: 다중 프로그래밍 시스템에서 실행중인 Program → 다른 Program으로 CPU 옮겨갈때

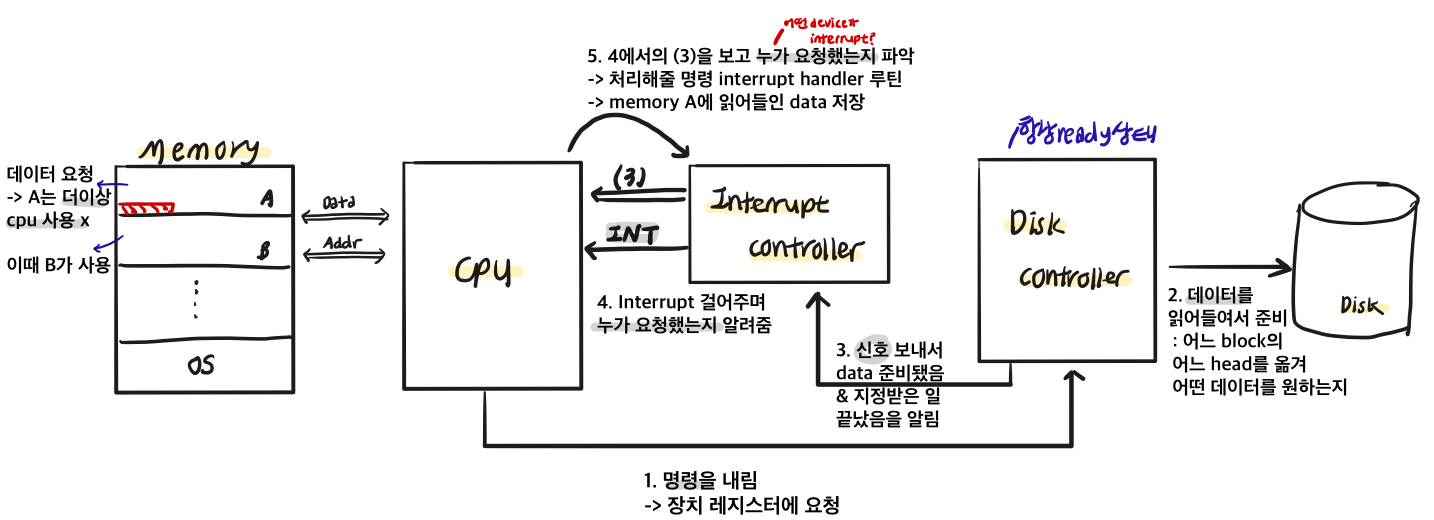

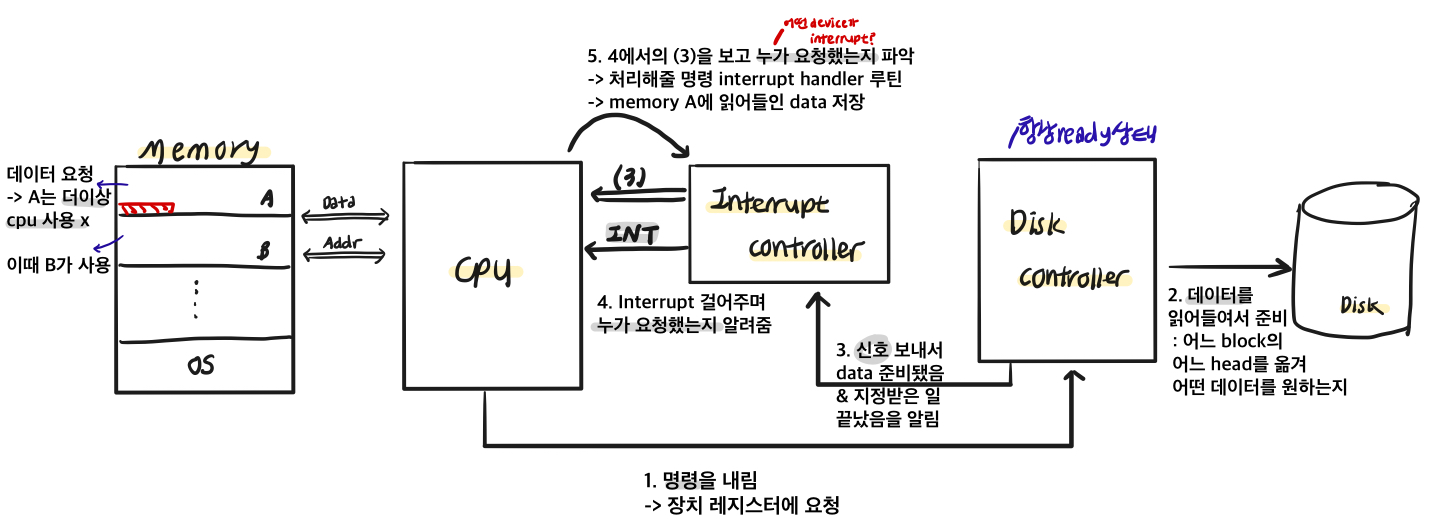

I/O Devices

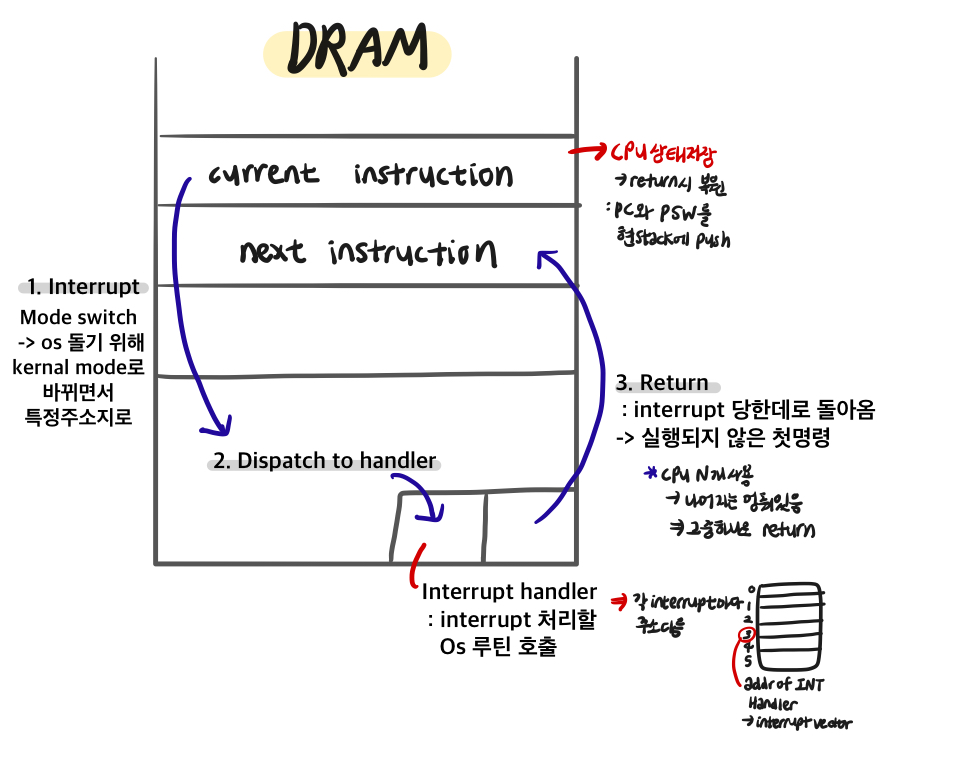

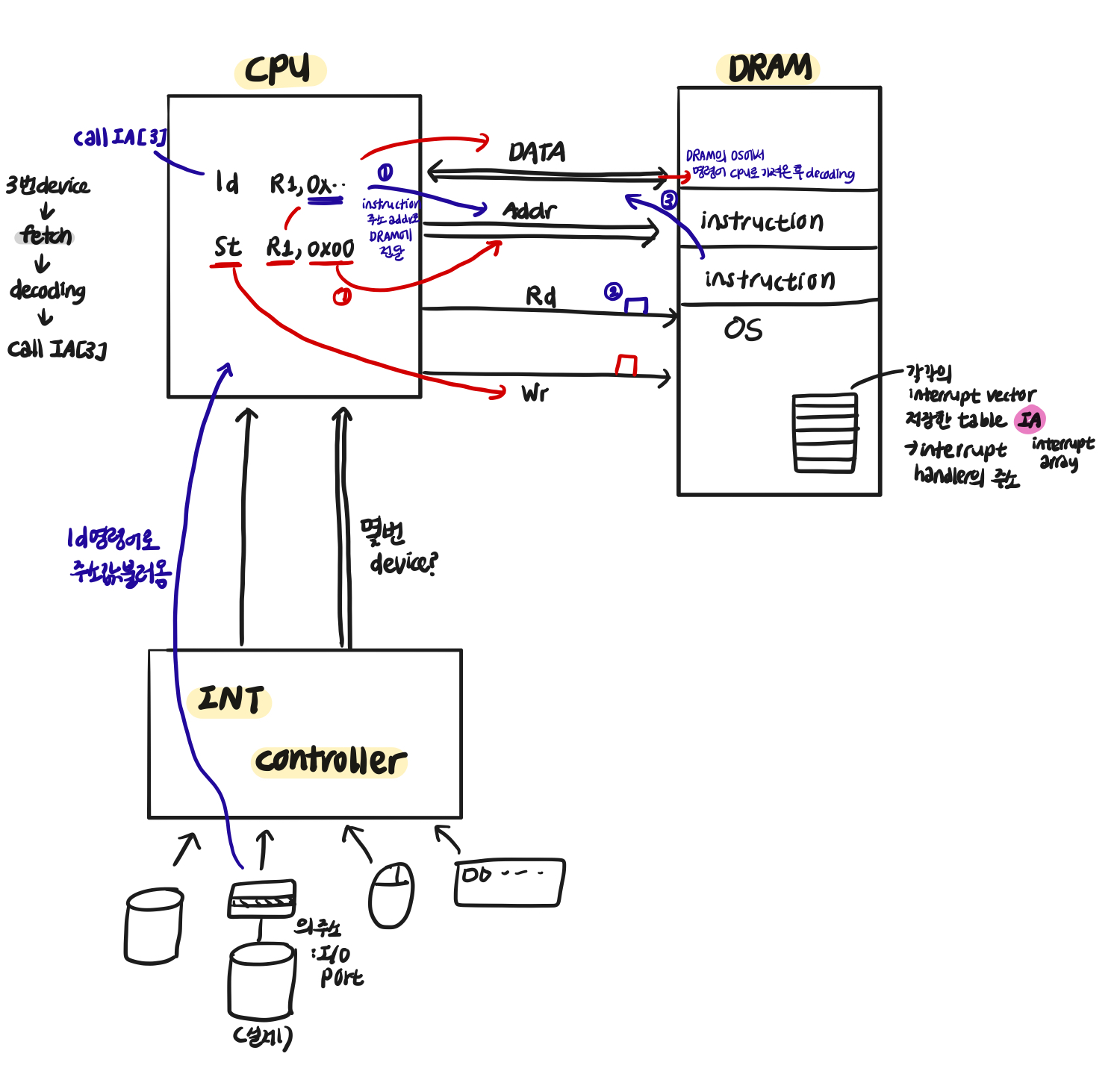

- INT?

: interrupt line에서 점프시 CPU가 하던 일 멈추고 특정 주소지의 명령어 실행

→ kernal mode로 바뀌고 특정 주소지 명령(int 처리 명령) 실행

e.g.

-

instruction fetch 과정

: CU안의 instruction 주소 Addr로 DRAM에 전달 -

DRAM의 OS에서 명령어 CPU로 가져온 후 decoding

-

다른 인터럽트 처리 중 등에 인터럽트 발생 ?

: CPU안에 인터럽트 무효화, 유효화 하는 방법 존재

→ 무효화? 인터럽트 계속 올려놓은 상태 유지 or 다시 유효화될때까지 인터럽트 수신 x

→ 우선순위 높은 장치부터 처리 -

I/O 장치

: device driver + device controller -

I/O port space

: device register들의 집합

→ 디스크 컨트롤러 : 디스크 주소, 메모리 주소, 섹터카운트, 읽기쓰기의 방향 지정 레지스터 -

I/O Access

→ 방법 1 busy waiting

: 사용자 프로그램이 시스템 호출 요청 → 커널이 변환 → 적절한 드라이버에 함수 호출 → 드라이버가 I/O 시작 (장치가 폴링루프로 작업 완료됐는지 확인) → 필요한 곳에 데이터 → 다시 유저모드로→ 방법 2 Interrupt

→ 방법 3 DMA (direct memory array)

: CPU의 지속적 개입 없이 메모리 - 컨트롤러 간의 비트흐름제어

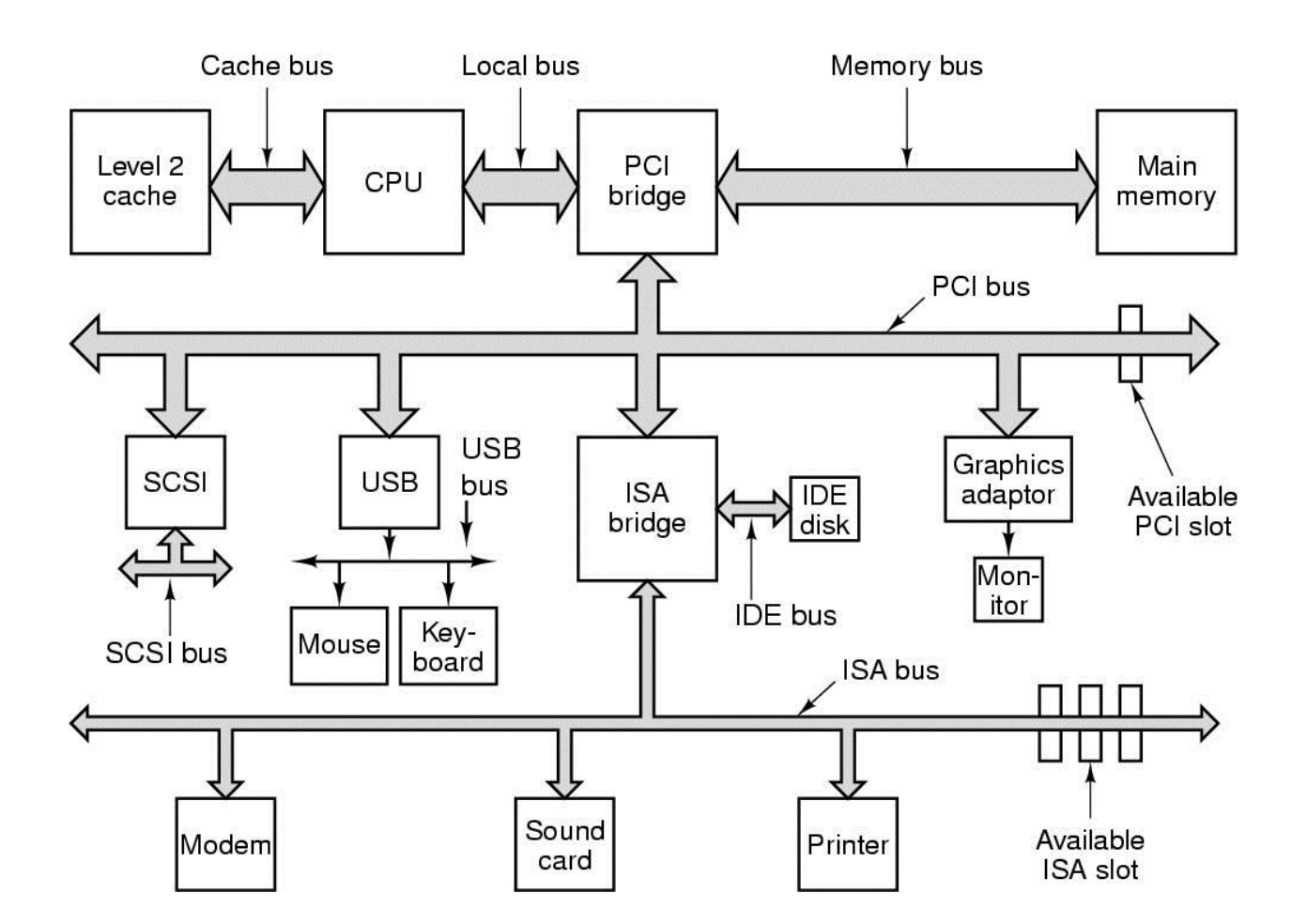

Buses

-

주요 버스

- 초기 ISA : 오래되고 느린 I/O 카드들의 호환성을 위해

→ 점차 사라지는 추세 - PCI : ISA의 후속

- 초기 ISA : 오래되고 느린 I/O 카드들의 호환성을 위해

-

특별한 기능의 버스

- IDE : 주변 장치(disk, cd-rom 등) 시스템에 연결

- USB : 느린 i/o장치 (키보드, 마우스) 컴퓨터에 연결

- SCSI : 고성능 버스 → 빠른 디스크, 스캐너, 높은 대역폭 필요 장치

개멎지다,, 이거보고 기말고사 공부할게요