개요

컴퓨터는 외부 환경과 통신하지 않으면 썩 유용한 결과물을 내놓기 힘들다.

그렇기에 입출력 장치를 갖추고 이를 통해 외부 환경과 통신 할 필요가 있다.

입출력 통신의 가장 기본적인 요구사항을 설명하자면 다음과 같다.

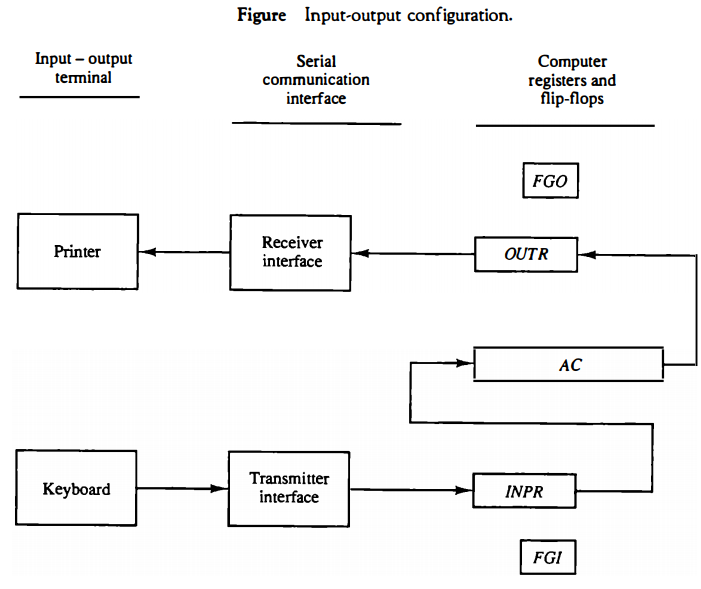

I/O terminal은 직렬로 정보를 주고 받는다. 이때의 각 정보는 8비트의 alphanumeric code로 이루어져 있다.

입력 장치의 직렬 정보는 Transmitter interface에 의해 INPR (Input Register)로 전송된다.

출력 장치에게 전달 될 정보는 OUTR (Output Register)에 저장되며, Receiver interface가 받아서 직렬로 전달한다.

두 register는 각 interface와는 직렬로 통신하지만, AC와는 병렬로 통신한다. 즉, INPR & AC & OUTR이 병렬로 연결되어 있다는 소리이고, 이건 입력 순서에 따라 순차적으로 정보가 이동되는 것이 아니라 여러 개의 정보가 일괄적으로 전송될 수 있다는 말이다.

INPR은 8비트로 구성되어 있으며 alphanumeric input information을 저장한다.

FGI는 제어 플립플롯의 하나이며, 새 정보가 있으면 1, 컴퓨터에 입력이 되었다면 0의 값을 가지는 flag를 표시한다. FGI의 flag가 1이라면 INPR 내부의 정보는 새로운 입력에 의해 교체될 수 없다. FGI의 초기값은 0이다.

FGO는 FGI와 비슷한 역할을 하지만 정보의 흐름이 반대이다. 초기값은 1이며, FGO가 0이라면 output device가 OUTR의 데이터를 출력하는 과정에 있다는 말이기에 OUTR의 값은 새 것으로 교체되지 않는다.

flag는 입력 장치와 컴퓨터 간의 타이밍 속도 차이를 동기화하는 데 필요하다.

I/O의 기본적인 과정

Input

-

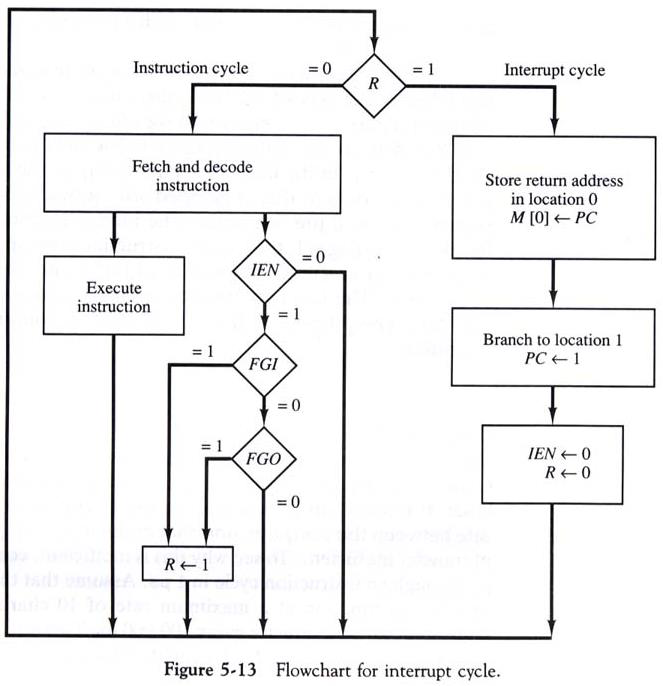

Input device로부터 직렬 정보가 입력되면 인터럽트가 발생, IEN = 1로 세트된다. (IEN = 인터럽트 발생을 알리는 플립플롯)

-

FGI가 0이면 입력된 정보는 Transmitter interface를 통해 INPR에 전송된다. INPR은 8비트 크기이며 8비트가 다 채워지면 FGI = 1로 세트된다. 1번에서 IEN이 이미 1이 되었기에 FGI == 1 && IEN == 1로 인해 R 플립플롯이 1로 세트되고 통상적인 Instruction cycle 대신 Interrupt cycle이 진행된다.

-

FGI를 확인해서 1이면 INPR의 내용을 PC로 옮긴다. 이때 AC는 OUTR가 적재할 수 있는 Output data로 변환처리한다. 데이터가 옮겨졌기에 INPR은 다시 이용가능 상태가 되어 FGI = 0으로 세트한다.

-

Interrupt cycle 진행 후 IEN, R = 0이 된다.

Output

-

출력 명령이 발생하면 IEN = 1로 세트된다. FGO의 초기값은 1이므로 R이 1로 세트되고 Interrupt cycle이 진행된다.

-

FGO 상태 확인해서 1이면 AC에서 OUTR로 데이터가 직렬 전송된다. OUTR 또한 8비트 크기이고, 다 채워지면 FGO = 0로 세트된다.

-

Interrupt cycle 진행 후 IEN, R = 0이 된다.

-

Receiver interface를 통해 Output device로 데이터가 전달되며 device는 데이터를 받고 출력 작업을 한다. 출력이 끝나면 Output device에 의해 FGO = 1로 세트되어 다시 이용가능 상태가 된다.

인터럽트와 IEN, R 플립플롯

왜 인터럽트를 사용해야 하는가에 대해 알아보자.

기본적으로 CPU와 입출력장치는 처리 속도는 확연히 차이가 난다.

CPU가 하나의 Instruction Cycle를 처리하는데 걸리는 속도를 1μs(micro sec)이라고 치고, 입출력 장치가 하나의 문자를 처리하는데 걸리는 시간을 0.1초라고 하자. 0.1초를 μs으로 바꾸면 100000μs가 된다.

플래그를 일일히 체크해서 1이면 분기된 해당 명령(전송 등)을 실행하고 하는 방식을 프로그램된 제어(programmed control) 내지는 polling이라고 하는데, 이러한 방식으로 입출력 체크를 하면 초당 100000회의 플래그 확인을 해야 한다. 그만큼 CPU의 시간이 낭비된다는 것이다.

반면, 인터럽트 방식을 사용해 평소에는 플래그 확인을 하지 않다가 인터럽트가 발생했을 때만 Instruction cycle이 Interrupt cycle로 돌아가게끔 설계를 하면 CPU가 그만큼 효율적으로 일을 하게 된다.

이에 인터럽트 발생을 알리기 위해 사용하는 것이 IEN (Interrupt enable) flip-flot이다.

FGI or FGO가 1이고, IEN도 1이라면 R 플립플롯을 1로 세트해서 Interrupt cycle이 돌아가게 된다.

인터럽트 사이클 수행 과정

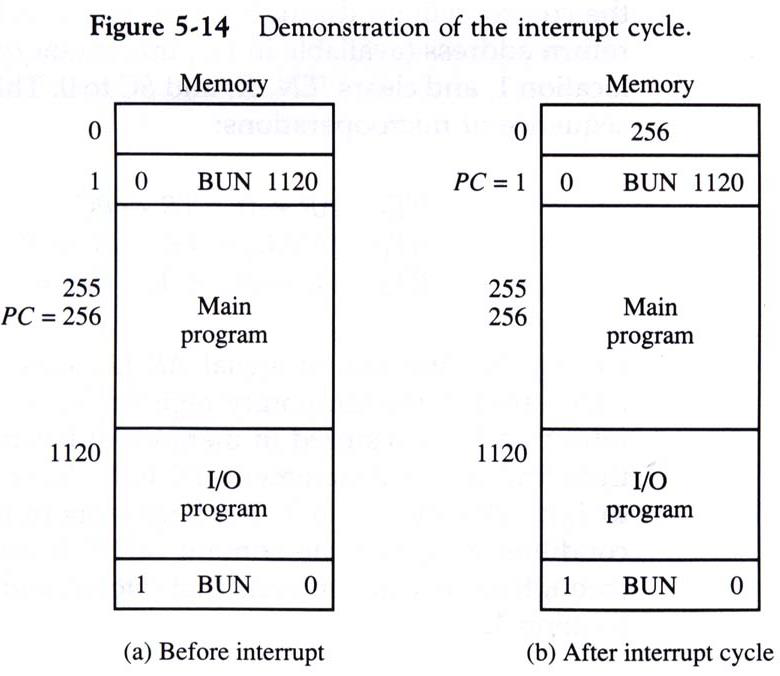

Precondition : 주소 255번의 명령이 실행 중에 인터럽트가 발생. I/O program은 주소 1120번에 올라와 있고, 해당 I/O program의 주소로 점프하는 명령은 주소 1번에 있다.

-

PC의 값 (return address)를 M[0]에 저장. PC를 0으로 세트

-

IEN, R, SC 클리어하며 PC + 1. 다음 명령은 Direct mode BUN 1120.

-

1120으로 점프해서 입출력 수행.

-

입출력 끝나면 Indirect mode BUN 0을 실행. 간접 모드이기에 0이 아닌 주소 0의 값 256으로 점프해서 하던 일 계속 수행.

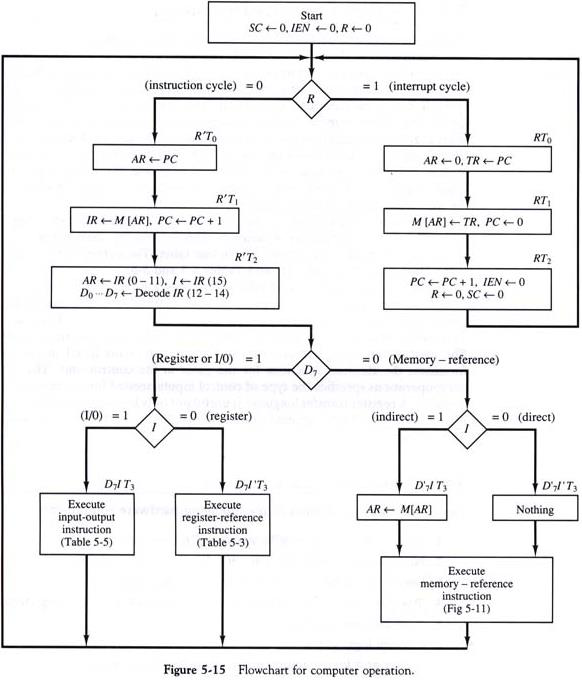

인터럽트를 포함해 컴퓨터 작업을 흐름도로 나타내면 다음과 같다.

Reference

- Computer Organization Architecture : https://upscfever.com/upsc-fever/en/gatecse/en-gatecse-chp157.html

- The Interrupt Cycle - UNCW : http://people.uncw.edu/tagliarinig/Courses/242/RegisterTransfer/The%20Interrupt%20Cycle.htm

- Topic 5: Input and Output : https://www.cs.albany.edu/~sdc/CSI404/Topic05.html