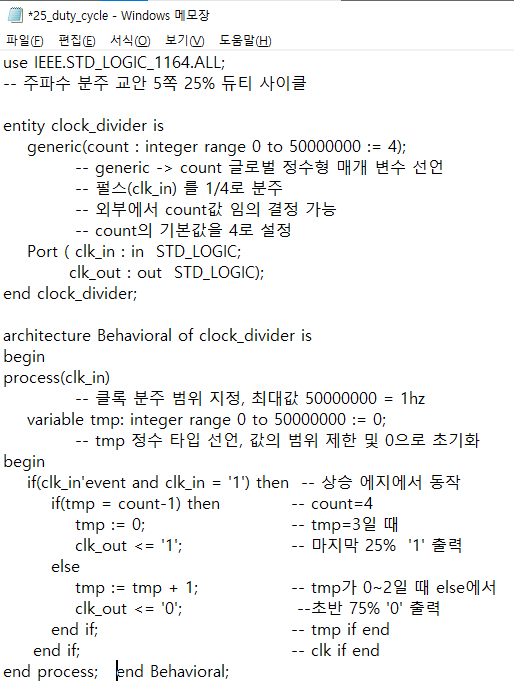

25% duty cycle 구현하기

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity clock_divider is

generic(count : integer range 0 to 50000000 := 4);

Port ( clk_in : in STD_LOGIC;

clk_out : out STD_LOGIC);

end clock_divider;

architecture Behavioral of clock_divider is

begin

process(clk_in)

variable tmp: integer range 0 to 50000000 := 0;

begin

if(clk_in'event and clk_in = '1') then

if(tmp = count-1) then

tmp := 0;

else

tmp := tmp + 1;

end if;

if(tmp < count/4) then

clk_out <= '1'; -- 25% 동안 '1' 출력

else

clk_out <= '0'; -- 나머지 75% 동안 '0' 출력

end if;

end if;

end process;

end Behavioral;이 코드에서:

tmp는 0부터count-1까지 계속 증가합니다.tmp가count/4미만일 때(즉, 전체 주기의 25% 동안)clk_out은 '1'입니다.tmp가count/4이상일 때(나머지 75% 동안)clk_out은 '0'입니다.

이렇게 하면 25% duty cycle이 구현됩니다. 예를 들어, count가 4라면:

- tmp가 0일 때 (25% 동안) clk_out은 '1'

- tmp가 1, 2, 3일 때 (75% 동안) clk_out은 '0'

이 패턴이 반복되어 25% duty cycle을 만들어냅니다.

generic과 variable의 주요 차이점

-

선언 위치와 범위:

- generic은 엔티티(entity)에서 선언되며, 전체 설계에서 사용 가능합니다.

- variable은 프로세스(process) 내부에서 선언되며, 해당 프로세스 내에서만 사용 가능합니다.

-

값 할당 시점:

- generic은 컴파일 시 또는 인스턴스화 시에 값이 할당되며, 실행 중에는 변경할 수 없습니다.

- variable은 프로세스 실행 중에 동적으로 값이 변경될 수 있습니다.

-

용도:

- generic은 설계를 재사용 가능하고 유연하게 만드는 데 사용됩니다. 예를 들어, 카운터의 비트 수나 분주 비율을 쉽게 변경할 수 있게 합니다.

- variable은 프로세스 내에서 임시 계산이나 상태 저장에 사용됩니다.

-

할당 연산자:

- generic은 인스턴스화 시 '=>'를 사용하여 값을 할당합니다.

- variable은 ':='를 사용하여 값을 할당합니다.

-

시뮬레이션과 합성:

- generic은 시뮬레이션과 합성 모두에서 상수처럼 취급됩니다.

- variable은 시뮬레이션에서는 동적으로 변할 수 있지만, 합성 시에는 특정 시점의 값으로 고정됩니다.

예시에서 generic(count)는 전체 설계의 분주 비율을 설정하는 데 사용되고, variable tmp는 프로세스 내에서 현재 카운트 값을 추적하는 데 사용됩니다. 이 두 요소는 서로 다른 목적과 범위를 가지고 있어 설계의 다른 부분에서 중요한 역할을 합니다.

generic 선언부

generic(count : integer range 0 to 50000000 := 4);이 제너릭 선언은 다음과 같은 의미를 가집니다:

-

매개변수 선언: 'count'라는 이름의 정수형 매개변수를 선언합니다.

-

범위 제한: 'count' 값의 범위를 0부터 50,000,000까지로 제한합니다. 이는 50MHz 클록을 기준으로 1초까지의 카운트 값을 표현할 수 있는 범위입니다.

-

초기값 설정: ':= 4'는 'count'의 기본값(default value)을 4로 설정합니다.

이 제너릭 선언의 주요 목적은:

- 재사용성 향상: 동일한 코드를 다양한 분주 비율에 사용할 수 있게 합니다.

- 유연성 제공: 컴포넌트 인스턴스화 시 분주 비율을 쉽게 변경할 수 있습니다.

- 오류 방지: 유효한 범위 내의 값만 사용하도록 제한합니다.

따라서 이 선언은 50MHz 클록을 기준으로 하는 분주기에서 기본적으로 4분주를 수행하되, 필요에 따라 다른 분주 비율로 쉽게 변경할 수 있게 해줍니다.

25% 듀티 사이클의 주파수 파형

- tmp = 0: clk_out은 '0', tmp는 1로 증가

- tmp = 1: clk_out은 '0', tmp는 2로 증가

- tmp = 2: clk_out은 '0', tmp는 3으로 증가

- tmp = 3: clk_out은 '1'로 변경, tmp는 0으로 리셋

출력 파형은 다음과 같습니다:

clk_in _|‾|_|‾|_|‾|_|‾|_|‾|_|‾|_|‾|_|‾|_

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6

tmp 0 1 2 3 0 1 2 3 0 1 2 3 0 1 2 3 0

clk_out _____|‾|_____|‾|_____|‾|_____|‾|_

L L L H L L L H L L L H L L L H L

<-75%->|25%|<-75%->|25%|<-75%->|25%|

<-1 cycle ->이 파형에서:

- clk_out은 tmp가 3일 때만 High('1') 상태가 됩니다.

- 전체 주기의 25%만 High 상태를 유지합니다.

- 나머지 75% 동안은 Low('0') 상태를 유지합니다.

이는 25% 듀티 사이클을 정확히 구현하는 방식입니다. 입력 클록 주파수의 1/4로 분주된 출력을 나타내며, 매 4번째 클록 사이클에서만 High 상태가 됩니다.

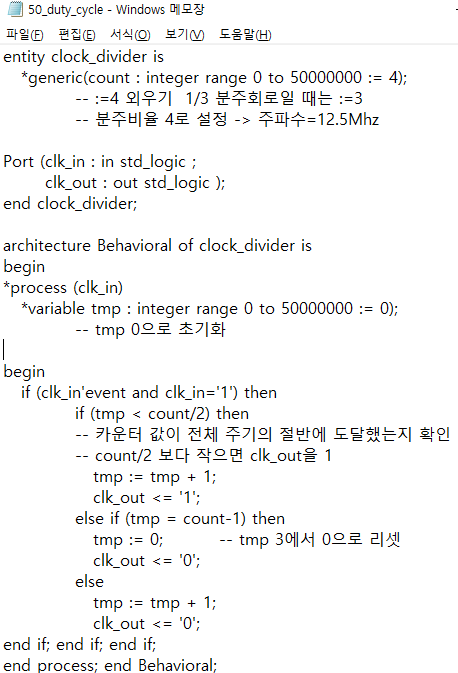

50% duty cycle

50% duty cycle 출력파형

-

tmp < count/2 일 때:

clk_out = '1' -

tmp >= count/2 일 때:

clk_out = '0'

이를 표로 나타내면:

| tmp 값 | clk_out 값 |

|---|---|

| 0 | '1' |

| 1 | '1' |

| 2 | '0' |

| 3 | '0' |

출력 파형은 다음과 같습니다:

clk_in _|‾|_|‾|_|‾|_|‾|_|‾|_|‾|_|‾|_|‾|_

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6

tmp 0 1 2 3 0 1 2 3 0 1 2 3 0 1 2 3 0

clk_out ‾‾|_____|‾‾|____|‾‾|____|‾‾|___|‾‾

1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1

<--50%-->|<--50%-->|<--50%-->|<--

<-----1 cycle----->이 파형에서 볼 수 있듯이, clk_out은 전체 주기의 50%동안 '1' 상태를 유지하고, 나머지 50%동안 '0' 상태를 유지합니다. 이는 정확히 50% 듀티 사이클을 나타냅니다.

50% duty cycle 주파수

분주란 주파수를 낮추는 과정입니다. 주어진 코드에서 generic 선언부의 := 4는 기본 분주 비율을 4로 설정한 것입니다.

이 설정으로 인해:

- 입력 주파수가 4로 나누어집니다.

- 출력 주파수는 입력 주파수의 1/4이 됩니다.

따라서, 50MHz 입력 클록을 사용할 경우:

- 출력 주파수 = 50MHz / 4 = 12.5MHz

맞습니다. 50% 듀티 사이클 코드의 주파수는 12.5MHz가 됩니다.

주의할 점은 분주 비율(여기서는 4)과 듀티 사이클(50%)은 별개의 개념입니다:

- 분주 비율은 출력 주파수를 결정합니다.

- 듀티 사이클은 한 주기 내에서 신호가 high 상태인 비율을 나타냅니다.

이 코드는 주파수를 4로 나누면서 동시에 50% 듀티 사이클을 유지하도록 설계되었습니다.

--

50% 듀티 사이클의 주파수 계산에 대해 설명드리겠습니다.

50*10^6/2 계산 결과는 정확히 25,000,000 또는 25MHz입니다. 하지만 이 계산이 50% 듀티 사이클의 주파수를 나타내는 것은 아닙니다.

50% 듀티 사이클은 신호가 한 주기 동안 절반의 시간 동안 high 상태를 유지하고, 나머지 절반 동안 low 상태를 유지하는 것을 의미합니다. 이는 주파수와는 직접적인 관련이 없습니다.

주파수 분주 회로에서 50% 듀티 사이클을 구현할 때, 출력 주파수는 입력 주파수를 분주 비율로 나눈 값이 됩니다. 예를 들어, 50MHz 입력을 4로 분주하면 출력 주파수는 12.5MHz가 되며, 이때 듀티 사이클은 50%가 됩니다.

따라서 50*10^6/2 = 25MHz는 단순히 50MHz를 2로 나눈 값일 뿐이며, 이것이 50% 듀티 사이클의 주파수를 의미하는 것은 아닙니다. 50% 듀티 사이클은 주파수와 관계없이 신호의 high와 low 상태의 비율을 나타내는 개념입니다.

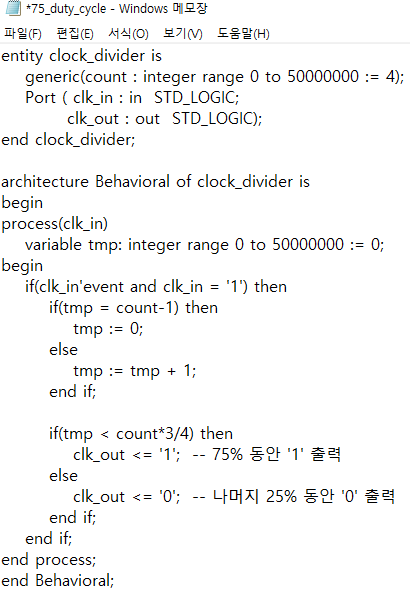

75% duty cycle

75% duty cycle 출력파형

High |‾‾‾‾‾‾‾‾‾‾‾‾‾| |‾‾‾‾‾‾‾‾‾‾‾‾‾|

| | | |

| | | |

| | | |

Low | |________| |________

|<---75%---->|<-25%-->|<---75%---->|<-25%-->

|<-------1 cycle----->|<-------1 cycle----->|이 파형에서:

- 신호는 전체 주기의 75% 동안 High 상태를 유지합니다.

- 나머지 25% 동안 Low 상태를 유지합니다.

- 이 패턴이 계속 반복됩니다.

75% 듀티 사이클은 전체 시간의 3/4 동안 신호가 활성 상태(High)를 유지하므로, 50% 듀티 사이클에 비해 평균 전력 소비가 더 높습니다. 이러한 파형은 LED 밝기 조절, 모터 속도 제어 등 다양한 응용 분야에서 사용될 수 있습니다.