코드에서 레지스터 동작

레지스터는 클럭의 상승 에지(rising_edge(clk))에서만 동작합니다. 이는 동기식 설계의 기본 원칙입니다.

- 클럭 상승 에지에서:

- 쓰기 동작:

we = '0'일 때, 입력 데이터(d)를 지정된 주소(addr)에 저장합니다. - 읽기 동작: 항상 활성화되어 지정된 주소의 데이터를 출력(

q)으로 보냅니다.

- 쓰기 동작:

시뮬레이션 결과 해석

주어진 테스트 벤치 코드에 따라 시뮬레이션을 수행하면 다음과 같은 파형을 얻을 수 있습니다:

-

쓰기 동작 (

we = '0'):- 클럭 상승 에지에서 입력 데이터(

d)가 지정된 주소(addr)에 저장됩니다. - 예:

addr = "00"일 때,d = "0100"이 저장됩니다.addr = "01"일 때,d = "0101"이 저장됩니다.

- 클럭 상승 에지에서 입력 데이터(

-

읽기 동작 (

we = '1'):- 클럭 상승 에지에서 지정된 주소의 데이터가 출력(

q)으로 나타납니다. - 예:

addr = "00"일 때, 출력은"0100".addr = "01"일 때, 출력은"0101".

- 클럭 상승 에지에서 지정된 주소의 데이터가 출력(

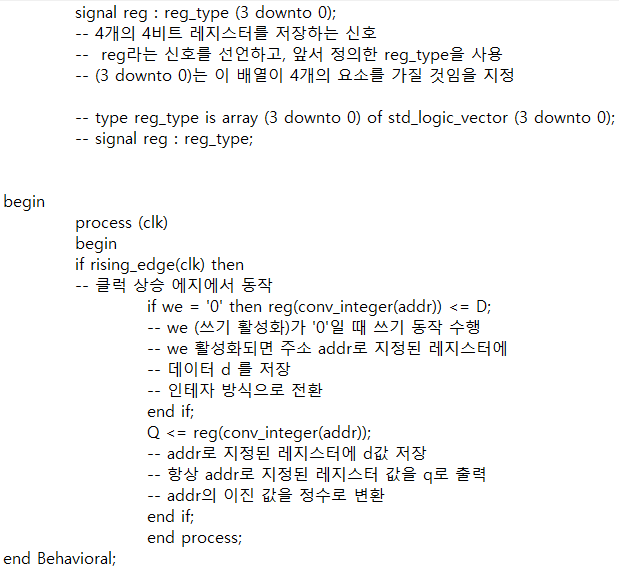

signal reg

signal reg : reg_type (3 downto 0); 이 부분에서 reg가 레지스터라는 것을 직접적으로 알려주는 것은 아닙니다. 이 선언은 단순히 4개의 4비트 벡터를 저장할 수 있는 배열을 정의하고 있습니다.

레지스터로서의 기능은 이 신호가 어떻게 사용되는지에 따라 결정됩니다. 이 경우, 레지스터로 동작하는 이유는 다음과 같습니다:

-

클럭에 동기화된 동작:

프로세스가 클럭의 상승 에지에 반응하도록 설계되어 있습니다 (if rising_edge(clk) then). -

데이터 저장 및 유지:

클럭 에지에서 데이터를 저장하고, 다음 쓰기 동작이 있을 때까지 그 값을 유지합니다. -

주소에 따른 개별 접근:

addr신호를 사용하여 개별 4비트 단위로 접근합니다. -

쓰기 동작 제어:

we신호를 통해 쓰기 동작을 제어합니다.

따라서, reg가 레지스터인지 여부는 이 신호가 어떻게 사용되는지, 특히 클럭에 동기화되어 데이터를 저장하고 유지하는 방식에서 유추할 수 있습니다.

natural range

-

type reg_type is array (natural range <>) of std_logic_vector(3 downto 0);- 이 줄에서는

reg_type이라는 제한되지 않은 배열 타입을 선언합니다. - 각 요소는 4비트

std_logic_vector입니다 (3 downto 0). <>는 배열의 크기가 나중에 결정될 것임을 나타냅니다.

- 이 줄에서는

-

signal reg : reg_type (3 downto 0);- 이 줄에서는

reg라는 신호를 선언하고, 앞서 정의한reg_type을 사용합니다. (3 downto 0)는 이 배열이 4개의 요소를 가질 것임을 지정합니다.

- 이 줄에서는

따라서, 이 두 줄을 통해:

- 유연한 배열 타입을 정의하고 (첫 번째 줄)

- 그 타입을 사용하여 구체적인 크기(4개 요소)의 신호를 선언합니다 (두 번째 줄)

결과적으로 reg는 4개의 4비트 벡터를 저장할 수 있는 배열이 됩니다. 이는 4x4 레지스터 구현에 적합한 구조입니다.

natural range 선언 비교

두 선언은 비슷해 보이지만 중요한 차이가 있습니다:

-

type reg_type is array (natural range <>) of std_logic_vector(3 downto 0);- 이것은 '제한되지 않은 배열 타입'을 선언합니다.

<>는 배열의 범위가 나중에 결정될 것임을 나타냅니다.- 이 타입으로 선언된 배열은 다양한 크기로 인스턴스화될 수 있습니다.

-

type reg_type is array (3 downto 0) of std_logic_vector (3 downto 0);- 이것은 '고정된 크기의 배열 타입'을 선언합니다.

- 배열의 크기가 명시적으로 4(3 downto 0)로 지정되어 있습니다.

- 이 타입으로 선언된 배열은 항상 4개의 요소를 가집니다.

주요 차이점:

- 유연성: 첫 번째 선언은 더 유연하며, 다양한 크기의 배열을 만들 수 있습니다.

- 고정성: 두 번째 선언은 항상 4개의 요소를 가진 배열만 만들 수 있습니다.

- 사용 시점: 첫 번째 방식은 배열 크기를 나중에 결정할 수 있지만, 두 번째 방식은 타입 선언 시 크기가 고정됩니다.

실제 사용 예:

-- 첫 번째 방식 사용

signal reg1 : reg_type(0 to 3); -- 4개 요소

signal reg2 : reg_type(0 to 7); -- 8개 요소

-- 두 번째 방식 사용

signal reg3 : reg_type; -- 항상 4개 요소결론적으로, 두 선언은 4x4 레지스터를 만드는 데 사용될 수 있지만, 첫 번째 방식이 더 유연하고 재사용 가능한 코드를 작성하는 데 유리합니다.

conv_integer(addr)

conv_integer(addr)를 사용하여 정수로 변환하는 이유는 다음과 같습니다:

-

배열 인덱싱 요구사항:

- VHDL에서 배열의 인덱스는 정수 타입이어야 합니다.

reg는 배열이므로, 접근할 때 정수 인덱스가 필요합니다.

-

addr의 타입:

addr은std_logic_vector(1 downto 0)타입입니다.- 이는 2비트 이진수로, "00", "01", "10", "11" 값을 가질 수 있습니다.

-

타입 변환 필요성:

- 배열

reg에 접근하려면addr을 해당하는 정수 값(0, 1, 2, 3)으로 변환해야 합니다.

- 배열

-

conv_integer 함수의 역할:

conv_integer는std_logic_vector를 해당하는 정수 값으로 변환합니다.- 예: "00" → 0, "01" → 1, "10" → 2, "11" → 3

따라서, conv_integer(addr)는 addr의 이진 값을 정수로 변환하여 reg 배열의 올바른 인덱스에 접근할 수 있게 해줍니다. 이를 통해 주소에 따라 정확한 레지스터 위치에 데이터를 저장하거나 읽을 수 있습니다.