Synthesis1

Logic Synthesis

RTL Level -> Gate Level

Cell Delay에 대한 Timing Closure

Physical Synthesis

P&R 이후의 DEF, QRC

wire 고려하여 Synthesis

Cadence QRC is the parasitic RCL (resistance, capacitance, and inductance) extraction tool which is valuable and powerful to help IC designers to complete both digital- and transistor-level circuit design and assure on-time tapeout.

Fusion Compiler

[출처] Synopsys

BIST(Built in Self Test)

Test를 위한 Test 수단 삽입

JTAG, IJATG 필요

Mentor Graphics사의 Tessent

Memory BIST(MBIST)

DFT

Fault의 검출 목적

ATE 장비를 이용하여 Chip test를 진행 <- 이때를 위해 Scan Cell 삽입

Scan Chain 구성

ATPG 및 ATPG Simulation

Tool : Design Compiler

Power Synthesis

Power를 줄이기 위한 Synthesis

UPF or CPF(Cadence)

Compiler NXT

UPF(Unified Power Format)

반도체의 효율적인 전력 설계/검증/구현을 위해 사용하는 방법론 혹은 언어

상대적으로 높은 수준에서 설계의 의로를 반영한 설계

파워 레일을 개별 블록으로 라우팅하는지, 블록의 전원을 켜거나 끌 것으로 예상되는 시기, 신호가 한 파워 도메인에서 다른 파워 도메인으로 교차할 때 전압 레벨을 어떻게 전환해야 하는지, 레지스터 및 도메인에 대한 기본 전원 공급 장치가 제거된 경우 메모리 셀 내용을 다룸.

관련 자료

https://ettrends.etri.re.kr/ettrends/182/0905182006/35-2_69-78.pdf

https://m.blog.naver.com/jdancor/223047286825

Synthesis 2

Synthesis = Translation + Mapping + Optimization

[출처] https://gakari.tistory.com/entry/Chapter2-Design-Compiler-Basics

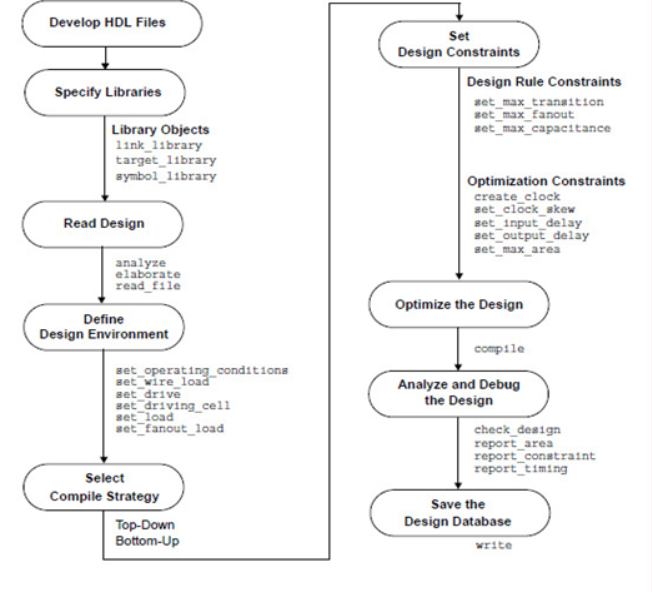

Synthesis Flow

1. Specify libraries

Design Compiler가 사용할 lib(db파일) 지정

Target lib, link lib, Symbol lib 선언

-

Read Design

analyze, elaborate, read_file -

Define design environment

Operating Condition(PVT), Wire load model, System I/F 지정 -

Compile 전략

-

SDC 설정

-

Compile 명령어를 사용한 Synthesis, Optimize

-

Analyze and Optimize Design

report를 확인하고 Debug -

Write 명령어를 통한 저장

Design Compiler

logic, Symbol, library 사용해서 합성

logic_library : optimization하는 중에 Target lib을 불러서 Mapping

target_library : Standard Cell db file

netlist를 만들 때 사용하는 Cell

link library의 subset이고 Design을 Translate할 때 사용

link_library : Standard Cell db file, IO PAD db file, IP db

delay models를 define하고 Timing Values와 Path Delay 계산

Physical Synthesis

wire delay 계산하여 Net delay 적용

Elaboration

Top을 기준으로 합쳐줌

사용하지 않는 코드제거

Clock gating candidate 식별

QoS (quality of Service)

Compile

Compile_ultra

Compile Strategies

- Patitioning이 합성에 정확한지 확인 -> RTL 계층 구조 분할 잘 하면 최적화 향상

- Constratins 정확하게 설정

- 좋은 Synthesis library 사용

- Multi Cycle, False path 잘 식별하기

- instantiate Clock gating elements

- Optionally, define scan Style

- 전략

7-1 Top Down Compilation

7-2 Bottom up Compilation

7-3 Mixed Compile