Glue Logic

복잡한 조합회로의 연결

최근에 AXI에서 배운 가운데 조합회로

연결이 중간에 안 끊어지면 Critical Path가 엄청 길어짐.

Registering All Outout

Block Output에 Reg를 연결하여 Delay 해결하는 방법

1. set_driving_cell my_flop [all_input]

2. set_input_delay 2 -clock CLK

Synthesis 3

implementing the Design Function

Technology libraries는 최적화시 Target libraries로 Mapping

target lib는 Netlist나 Design 동작 조건 같은 Cell

Resolving Cell References

Linking 과정 중 reference를 link lib에 연결

link libraries는 Timing 값과 path delay를 계산한다.

Symbol libraries

Specifying Libraries

Target library

Translate할때 사용

DC는 기능적으로 정확한 GATE를 target library에서 선택함. <- 이 선택된 GATE를 통해 Timing Delay 계산

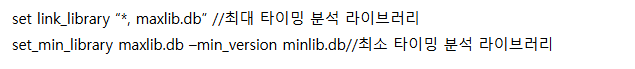

link library

library list를 명시하고 dc는 이 라이브러리를 linking하는 과정에서 사용

delay models를 define하고 Timing Value와 path delay 계산

local library

wire load selection group, wire load mdel, net delay의 계산

physical Synthesis

library loading

read_file my_lib.db

read_file my_lib.sdb

listing Library

list_libs 명령어를 사용하면 현재 사용하고 있는 lib을 볼 수 있음.

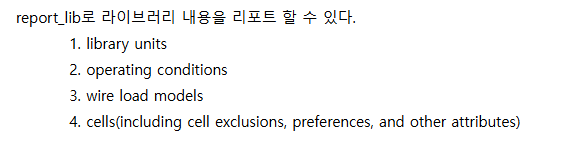

reporting library contents

report_lib으로 라이브러리 내용을 확인하는 것이 가능

specifying library objects

**[file:] library/cell/[pin]

file : technology file name

EX) set_dont_use my_lib/AND3

EX2) set_disable_timing [get_pins my_lib/AND4/Z]

my_lib library안에 AND4의 Z핀을 사용하지 말라는 뜻

[출처] https://gakari.tistory.com/entry/Chapter4-Working-With-Libraries