Video processing FPGA -1

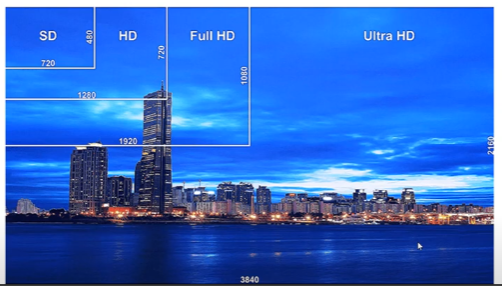

해상도

디스플레이의 너비와 높이

resolution = width height

보통 너비를 먼저 정의하고 높이를 정의한다.

1920 1080

1920 1080 Full HD

1280 720 HD

1픽셀은 RGB 3픽셀로 구성되어 있음.

Frame Rate

프레임 속도는 기본적으로 초당 프레임 수

60, 50 HZ는 초당 50개의 이미지가 다시 돌아오는 것

주파수가 존재하는 이유

시력의 지속성으로, 눈과 뇌의 한계

일반적으러 50, 60 FPS

ex) 1920108060*3 = 373.248 MB/S 초당 373

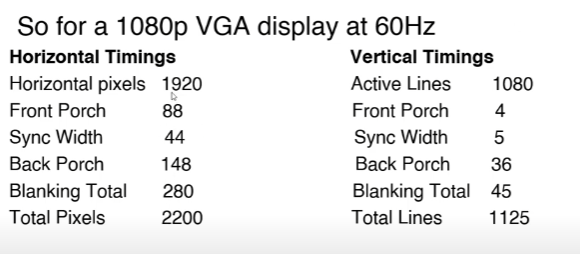

Synchronization

vsync 수직 동기화

기본적으로 시작되는 위치를 디스플레이에게 알려주는 것

1080개의 ----------------------- 이러한 줄이 있는 것, 수평선

hsync 수평 동기화

타이밍 요구 사항

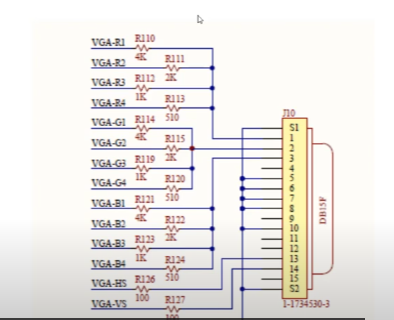

회로

VGA schematic

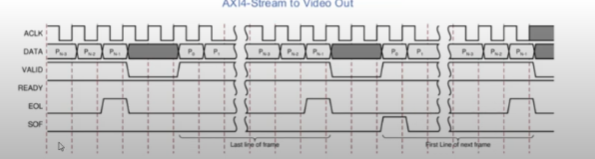

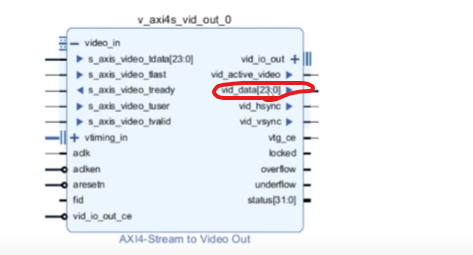

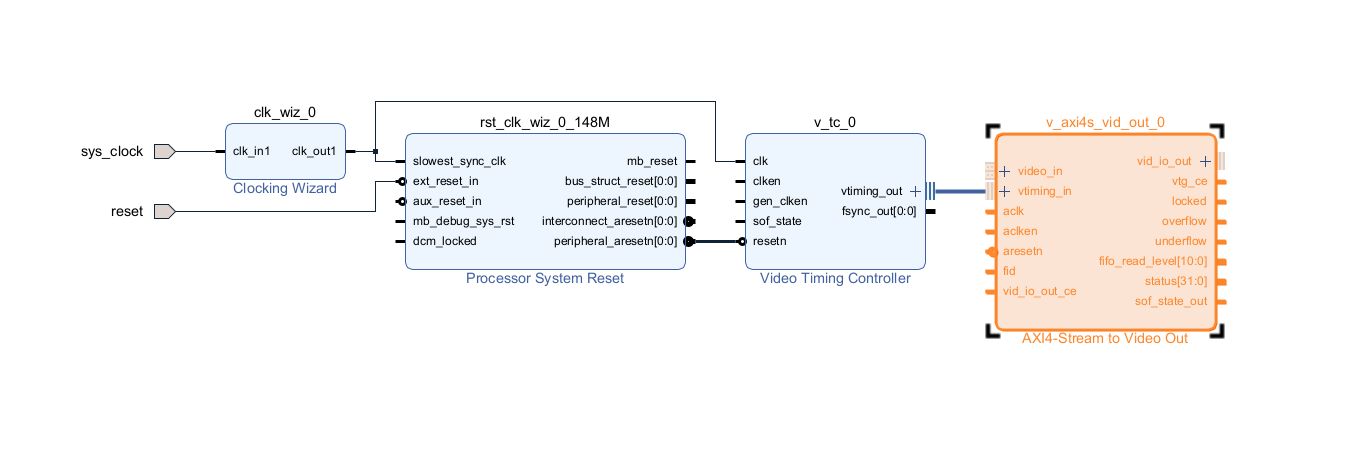

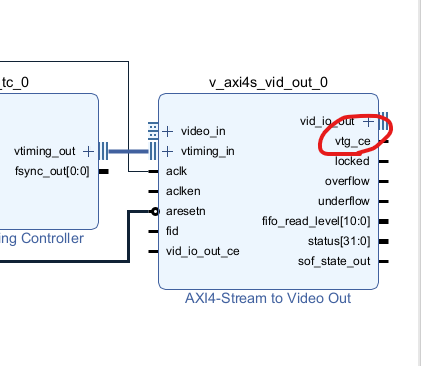

axi4-stream Video Out

비디호 신호를 받아서 Synchronize 해줌.

왼쪽의 Slave 부분에 Video 신호를 받아줄 예정.

타이밍을 받아와야하고, 수직동기화 작업이 필요함.

AXI의 Ready/Valid 특성이 이용됨.

Tuset : SOF 신호와 매핑됨. 프레임의 시작을 알리는 신호..?

EOL sig: 프레임의 끝을 알리는 신호 , end of line , 1clk을 높게 만들어 줘야 함.

모든 Line 신호를 보낸 후에 EOL signal이 높게 올라가야 함.

비디오 신호를 보낼 때 해야 할 일은 , 첫 번째 신호를 보낼 때 중요한게 SOF

IP에 수평동기화, 수직 동기화에 대한 정보가 필요함.

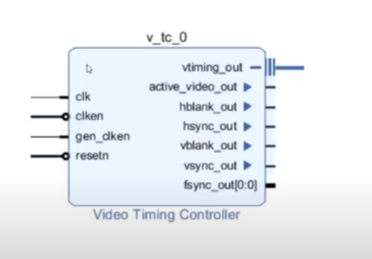

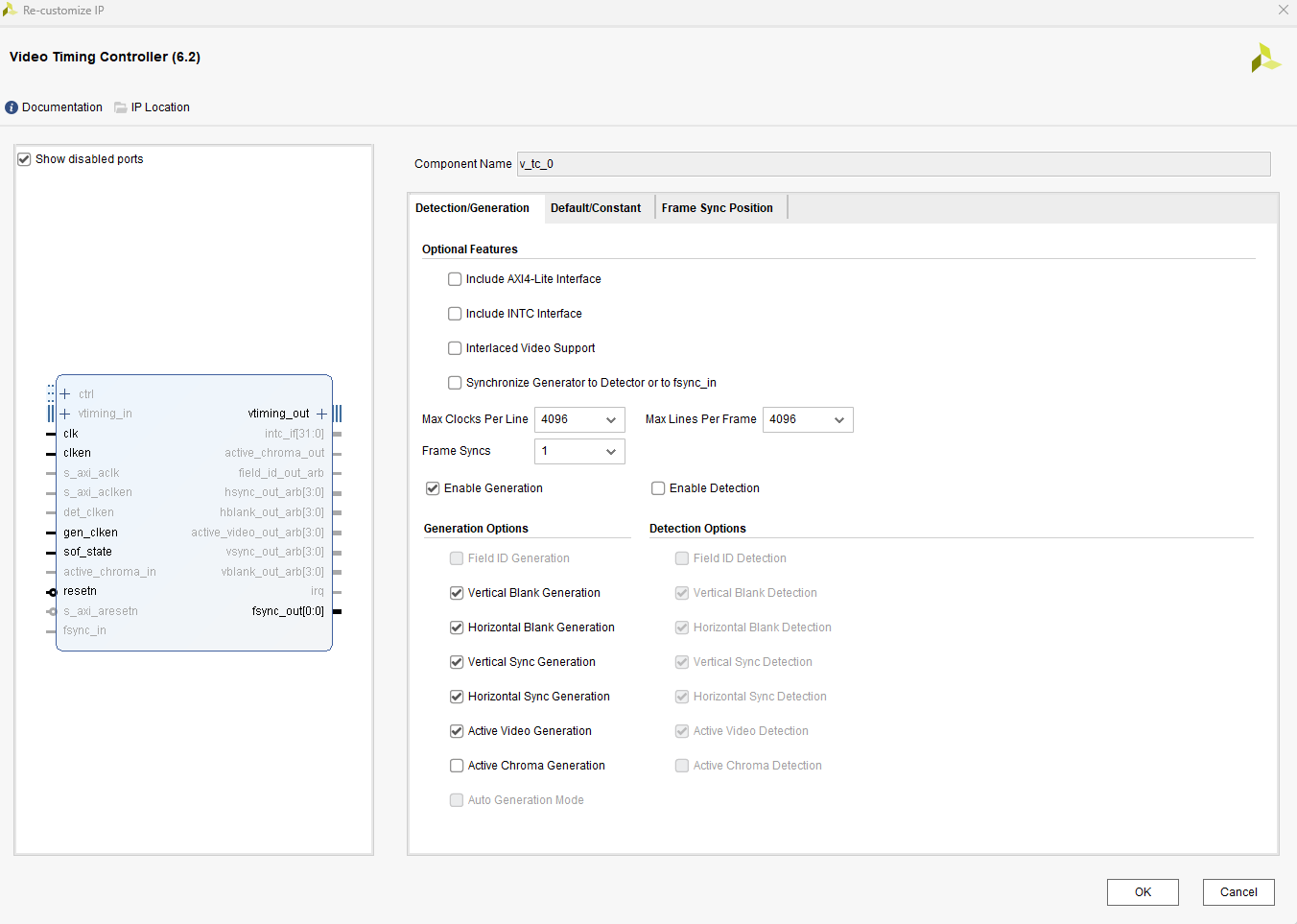

Video Timing Controler

IP에 수평동기화, 수직 동기화 정보만들기

clk, rst 필요함.

IP의 오른쪽에 Vsync, hsync를 보내줌.

video data가 여기서 나감

색상 채널당 24비트 RGB 나눠서 8비트씩

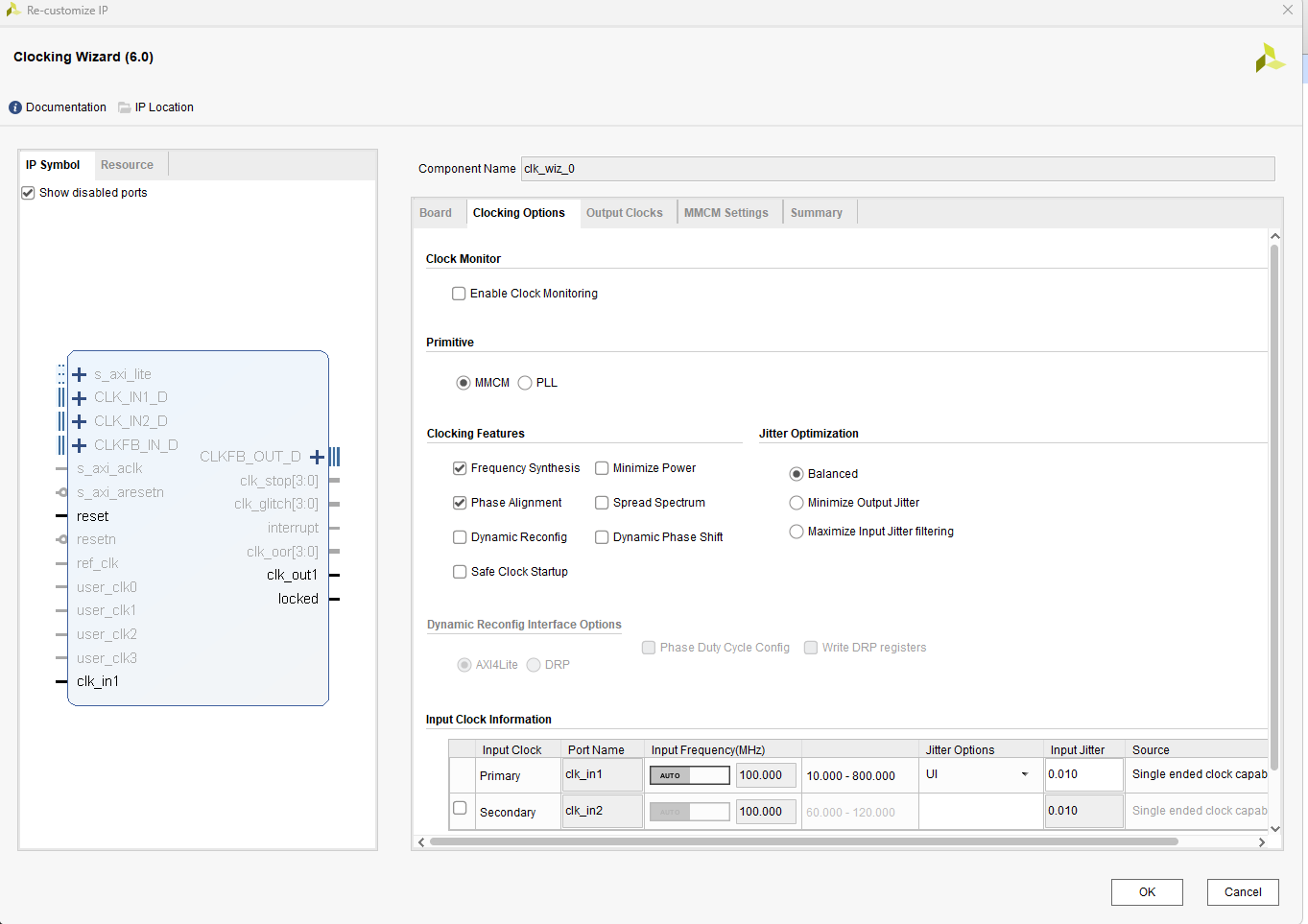

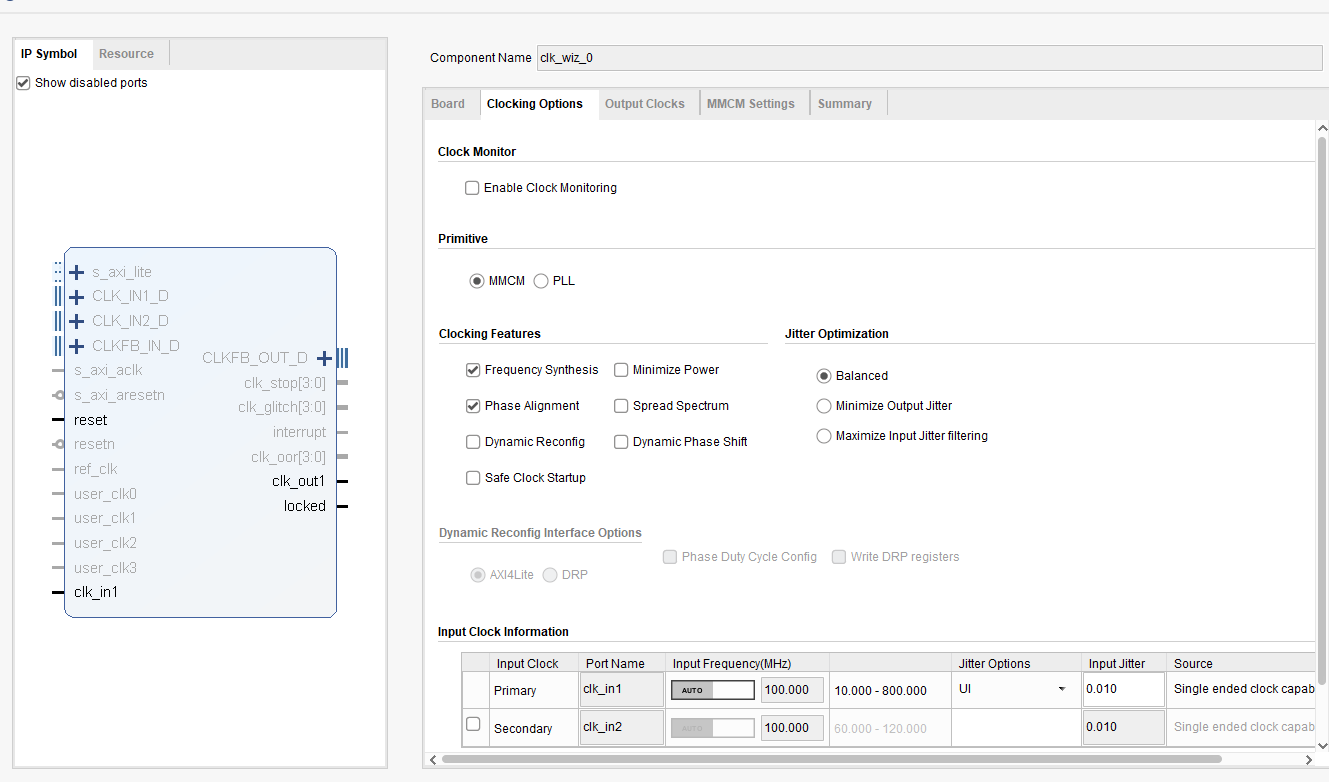

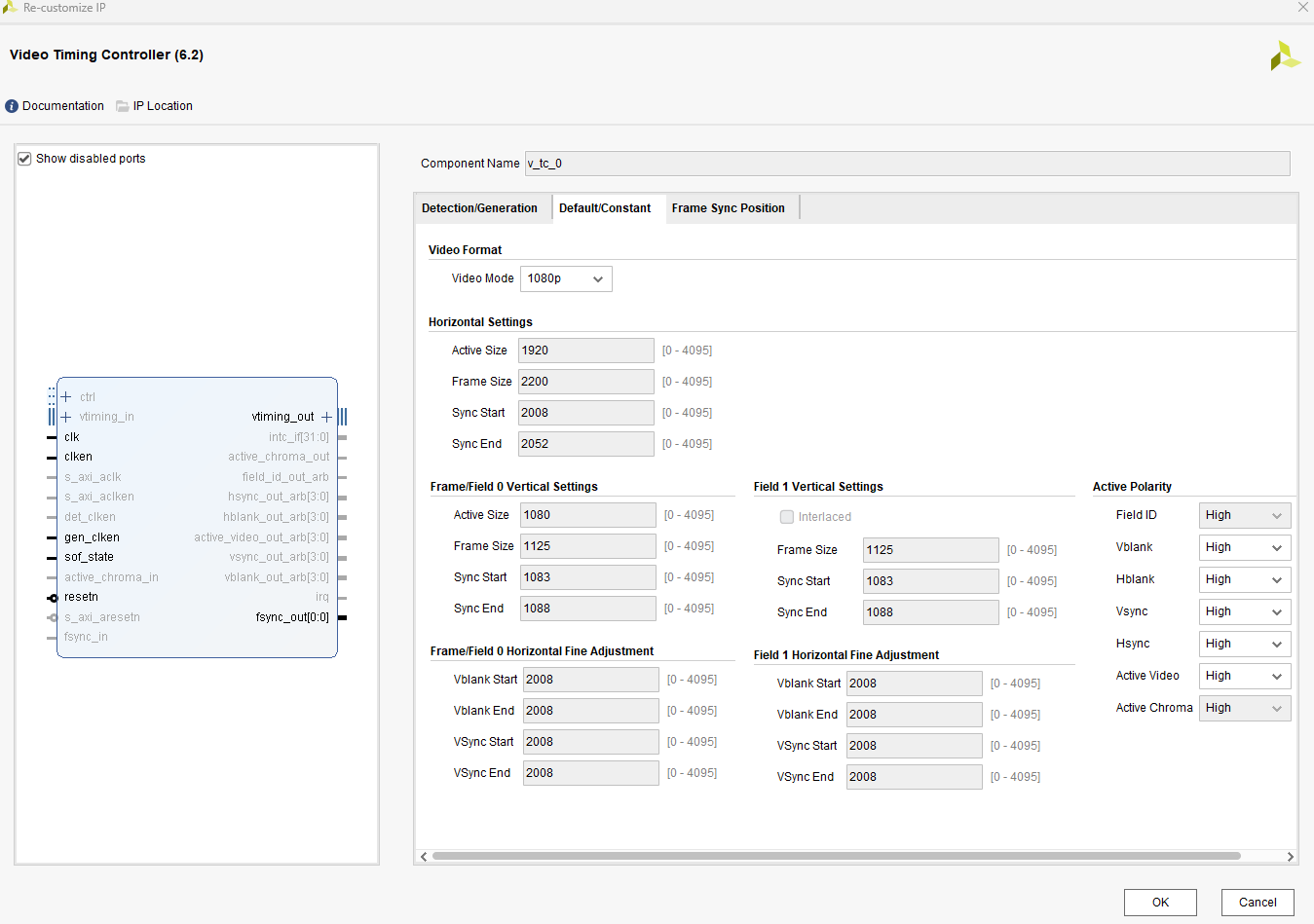

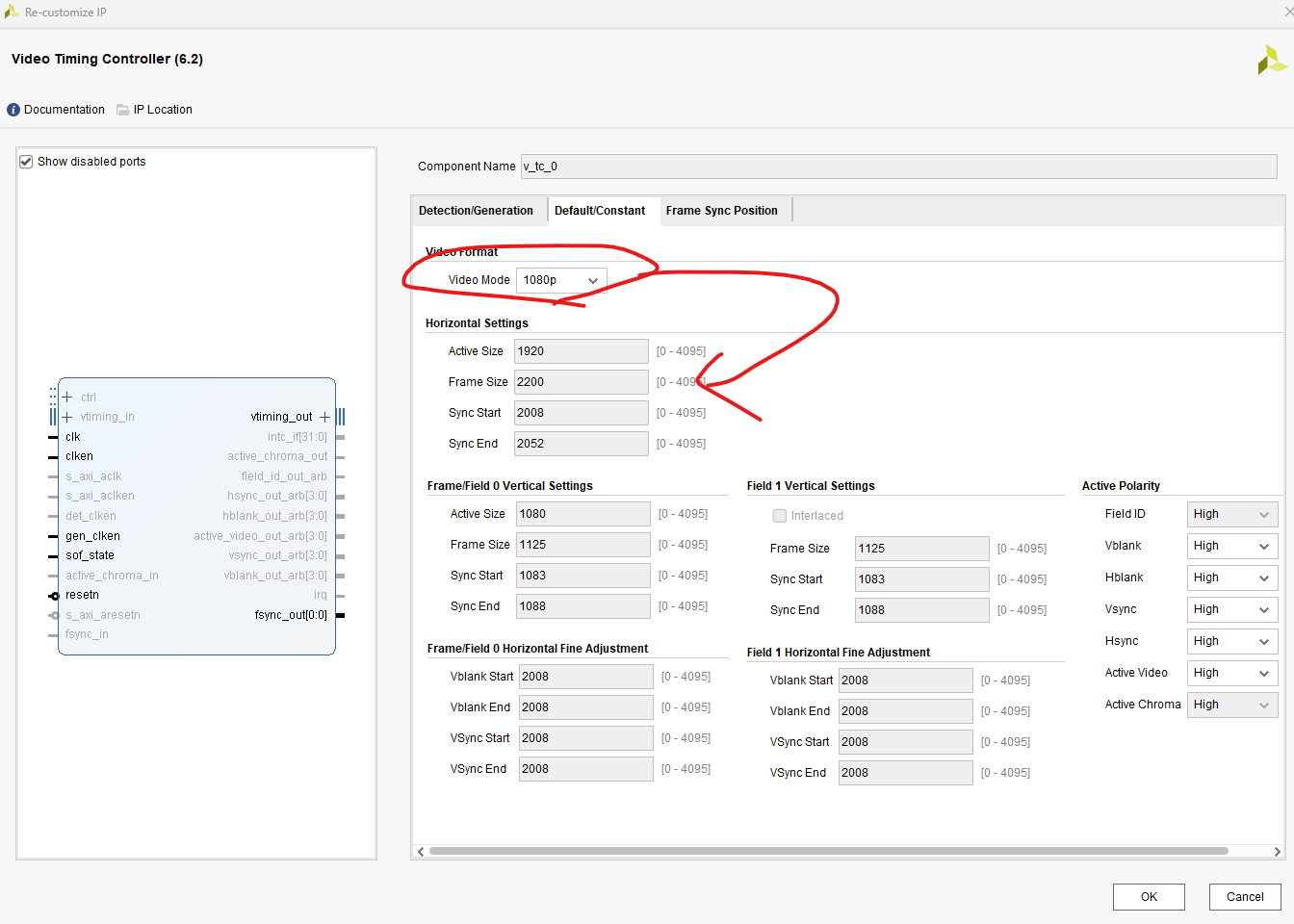

VGA 1920*1080 148.5 Mhz

y9 pin에서 100MHz를 필요로 그것을 받아주는 간단한 IP 시스템

100Mhz를 148.5 Mhz로 바꿔줄 예정

PLL 사용 or MMCM?

MCMM이 Jitter측면에서 괜찮음.

Video timing controller

이 ip는 동기화 신호를 생성하고,

IP test를 위해 만들어진 HW

Video Timing Controller에서 받은 timing_out으로 video Timing을 받고 AXI4 - stream이 이를 결합한다.

vtg_ce : Video Timing 생성기, clk 활성화를 의미한다.

Video Timing Controller의 gen_clken과 연결되야 함.

Video Timing Controller의 중지, 시작을 하고 싶은 상황에서 사용함.