SSD 아키텍쳐

NAND 플래시 메모리

현재 대부분의 SSD는 NAND 플래시 메모리를 채택하고 있다. 비휘발성 메모리로 쓰기/지우기가 NOR 플래시 메모리보다 빠르다.

-

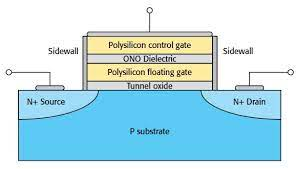

Write 동작: controal gate에 강한 전압을 인가하면 P-substrate의 전자가 floating gate로 이동함.

floating gate에 전자가 존재 -> 0으로 인식 (Threshold Voltage가 증가하여 channel 형성이 어려워짐)

floating gate에 전자가 존재하지 않음 -> 1로 인식 -

Erase 동작 : Write와 반대로 P-substrate에 전압을 가하여 floating gate에 갇힌 전자를 다시 P-substrate로 이동시킴.

-

Read 동작 :

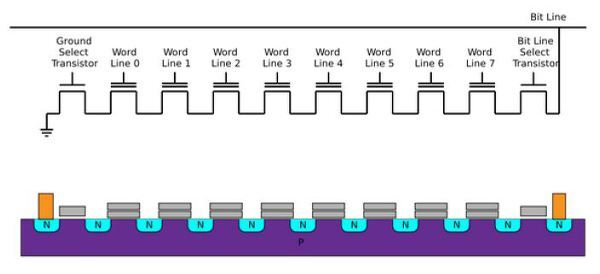

Cell을 직렬로 연결하고 하나의 Cell의 제외한 모든 Cell에 Vth(Threshold Voltage)를 인가하여 순차적으로 데이터 저장 여부를 판단

-- FG (floating gate)에 전자가 존재

: 0V를 인가해도 Channel 형성 X

Bit Line의 전류가 잘 흐르지 않는다 -> '0'-- FG에 전자가 미존재

; Vth < 0이므로 0V를 인가하면 Channel 형성

Bit Line의 전류가 잘 흐른다 -> '1'

-

Wearing-off (수명 제한)

: Cell에 쓰기/지우기 과정을 반복하며 트랜지스터 내부에 전자가 갇힘. 일정 수준을 초과하면 해당 Cell은 사용 불가능 -

cell당 bit수 확장

: floating gate에 갇힌 전자량을 계산하여 Threshold Voltage을 이용해서 현재 기술로는 1개 Cell당 최대 8비트까지 구분할 수 있다.Multi level로 갈수록 공정 난이도가 증가하지만, 1개 셀에 여러 bit를 구현할 수 있어서 원가경쟁력을 높일 수 있다.

Single level의 경우는 일반적으로 오류가 적어서 높은 신뢰성을 요구하는 항공기 및 자동차 분야에 사용된다.

- Page : 읽고 쓸 수 있는 최소 메모리 단위

- Block : Page가 모여서 Block을 구성하는데 NAND 플래시 메모리는 소자 특성상 Erase 작업이 Block 단위로만 수행된다.

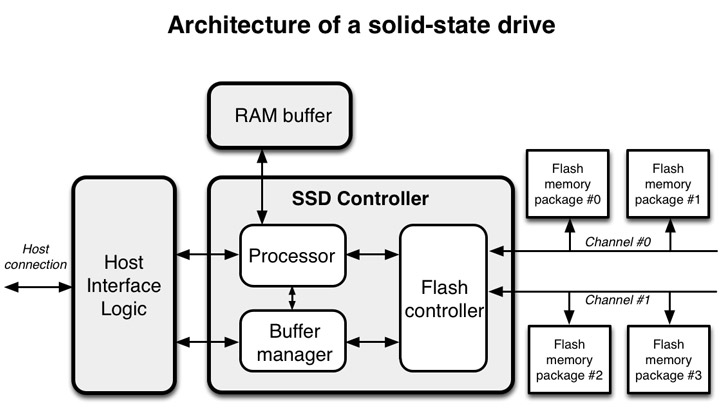

SSD 구성

- Host Interface Logic : SSD로 사용자 요청을 I/F

- Processor : 사용자 명령을 해석하여 Flash controller로 전달

- RAM buffer : 메모리의 logical mapping 정보를 저장하거나 Cache로 활용

- Flash controller : flash memory의 cell에 정보를 어떻게 처리(읽기/쓰기/지우기)할 것인지 판단