Cache Mapping 구조

CPU에서 데이터에 접근할 때, 먼저 Cache에 존재하는지 확인하고 원하는 데이터가 있다면 Main Memory에 직접 접근하는 것보다 빠르게 접근할 수 있다.

- cache hit : cache에 원하는 데이터가 존재

- cache miss : cache에 원하는 데이터가 존재하지 않아 main memory에 직접 접근

Main memory의 데이터를 cache에 mapping 시키는 방법은 대표적으로 3가지가 존재한다.

Direct Mapped Cache

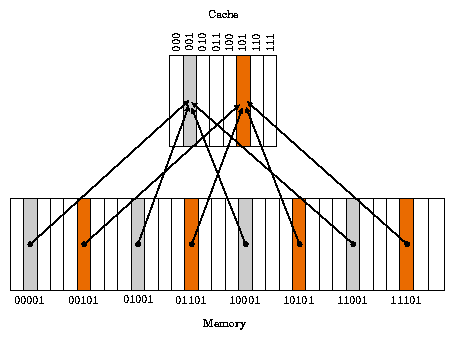

Cache와 Main memory가 1:N으로 Mapping된 구조

Cache의 각 Line에 들어갈 수 있는 데이터 주소를 직접 지정해놓은 형태로 tag와 index를 통해 miss/hit 판단 가능

- Index Field: Cache의 위치로 위 그림에서 000~111에 해당. CPU에서 cache 접근 시, 가장 먼저 확인

- Tag Field : 특정 Cache Line과 Mapping된 Main momory의 주소에 대한 정보.

위 그림에서는 Cache (001)에 00 + 001 / 01 + 001 / 10 + 001 / 11 + 001 이 Mapping 되어있다.

001 -> index를 의미

00/01/10/11 -> Tag를 의미

CPU에서 00001 주소의 데이터를 찾는다고 가정하면

1. 0001 index의 cache를 확인

2. 비어있으면 miss, 데이터가 존재하면 tag (00)을 확인

3. tag와 접근 주소가 일치하면 hit, 아니면 miss

- 장점 : 구조가 단순하고 값이 싸다, 메모리 접근 시간이 빠르다.

- 단점 : Cache Miss 확률이 높고 계속 안쓰이는 주소가 존재하면 cache 활용이 비효율적이다.

-> 만약 00001 과 01001 주소를 번갈아가며 접근한다면 cache miss가 지속적으로 발생함.

Fully Associative Cache

Cache의 Line 위치에 구분없이 데이터를 저장할 수 있다.

따라서 Tag Field만을 이용하여 cache miss/hit를 판단한다.

- 단점 :

Index Field가 존재하지 않는다.

-> Cache에서 메모리 주소를 검색할 때 모든 Line을 검사해야 한다.

-> 메모리 접근 속도가 매우 떨어진다. - 장점 :

Cache 메모리 위치에 상관없이 저장할 수 있기 때문에 Cache Miss 확률이 낮아진다.

-> 저장 과정이 간단하다.

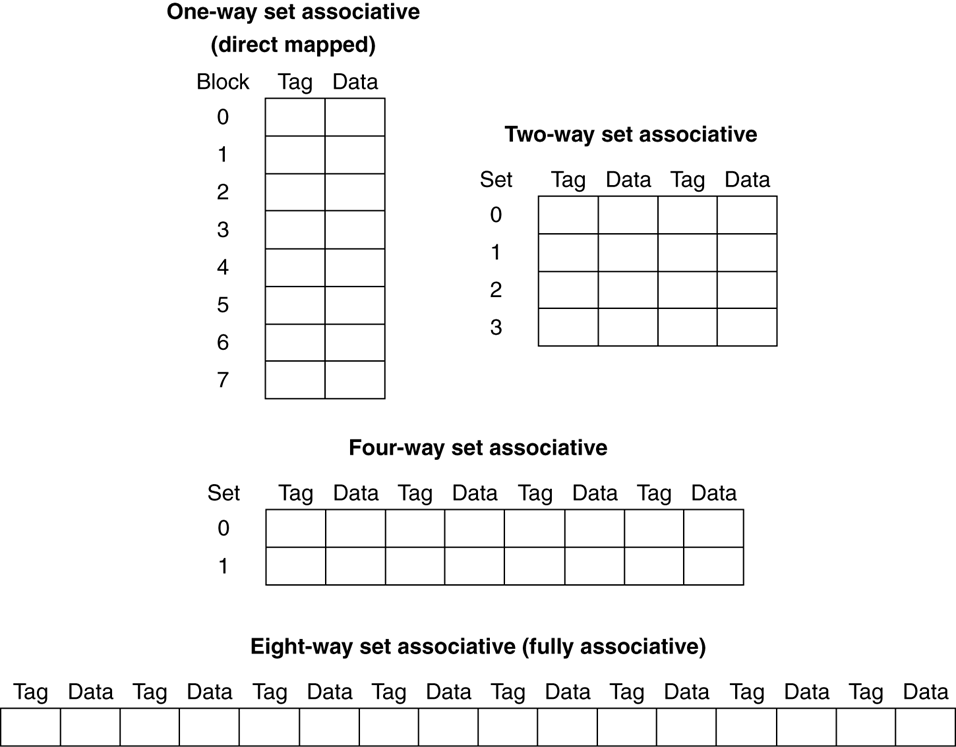

Set Associative Cache

Direct Mapped Cache + Fully Associative Cache 구조

- SET : Direct mapped 구조의 index에 해당

특정 set으로 접근하고, 하나의 set 안에서는 Associative 구조와 같이 순차적으로 Tag를 탐색하여 메모리에 접근하는 방식.

- N-Way 방식 : 여기서 n은 1개의 set 안에 들어갈 수 있는 tag의 갯수를 의미한다.

따라서 1-Way는 1 set 당 1 tag 이므로 direct mapped 방식과 같다.

- Direct mapped 구조와 Associative 구조를 적절히 섞은 형태로 현대의 CPU 설계 방식에서는 해당 구조를 채택하고 있다.