5 Staged Pipelined MIPS Emulator

I started this project to improve my problem-defining logic. In developing commercial apps, I felt the need for logic to clearly define complex requirements, which is why I developed Emulator and tried to refine MIPS features such as pipelining and hazard handling into specific logic and test code.

Abstract

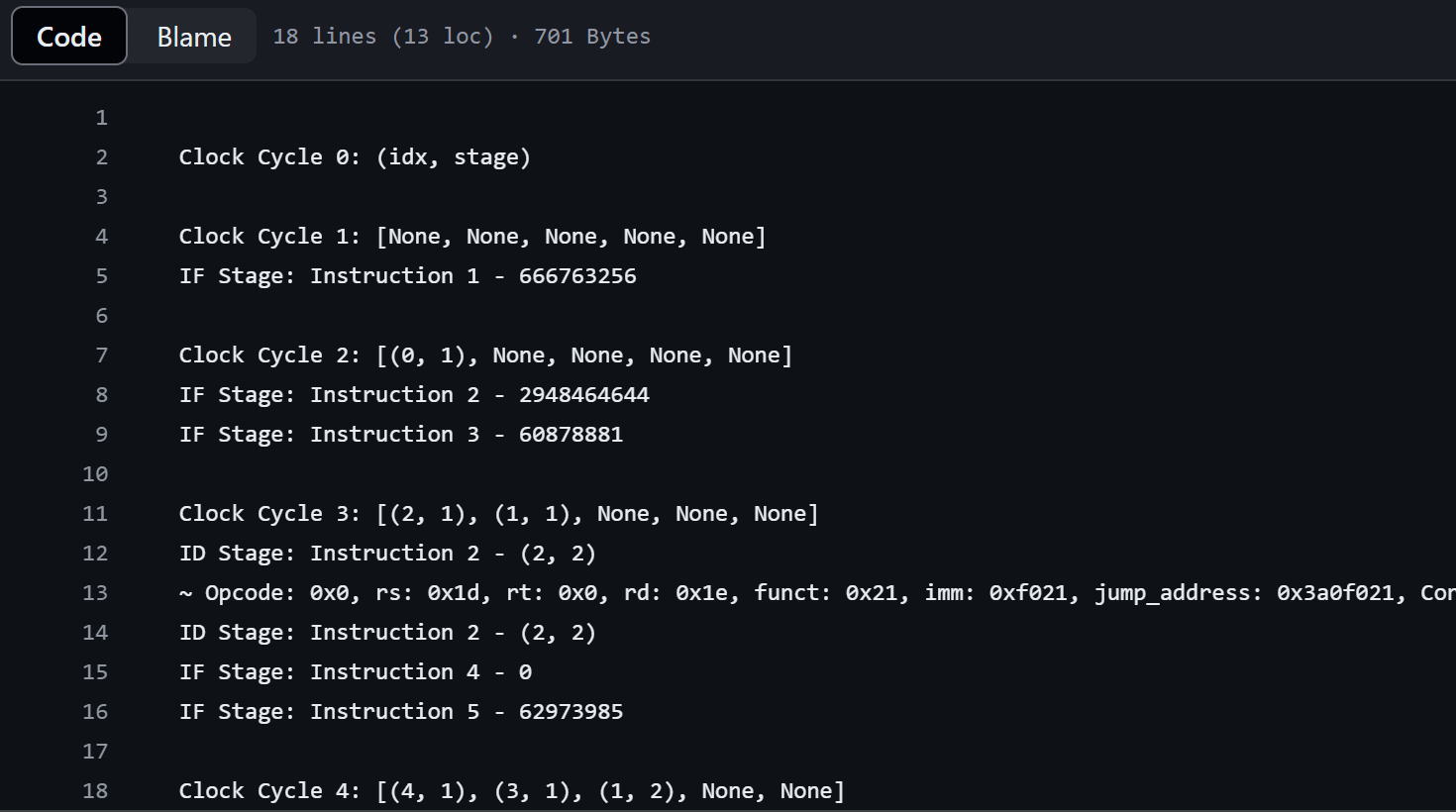

This project involves the development of a five-stage pipelined MIPS emulator using Python, drawing insights and references from QEMU. The emulator implements core features of a pipelined architecture, addressing challenges such as maintaining stage independence, handling data and control hazards, and optimizing performance through techniques like scoreboarding and data forwarding. By comparing specific implementations with reference code, this project demonstrates the nuances of pipeline execution and hazard management, providing a detailed examination of each stage's functionality and the strategies employed to enhance the emulator's efficiency and accuracy.

- Test Codes

This test code is for modularization of each features. You can run single file and get result. - Structures

- test

- hazard

- control

- branch prediction

- dynamic

- BTB_LTB_2_Bit_Counter.py

- static

- static_performances.py

- minimize control dependency

- predicate_combining.py

- predicated_execution.py

- data

- forwarding

- data_forwarding.py

- scoreborading

- simple_scoreboarding.py

- simple_scoreboarding_cons.py

- advanced_scoreboarding.py

- datecting

- stall_conditions

- pipelined

-sample_pipelined.py