Hazard

1. Control Hazard

- Current instruction's IF stage is dependent on previous instruction's WB stage.

2. Data Hazard

- (RAW) Current instruction's EX stage is dependent on previous instructions’ EX, MM, WB.

- (WAR, WAW) Occur due to non-uniform execution time of each stages.

- If current instruction's EX is dependent to previous instruction's EX, is WAR.

- If dependent to WB, is WAW.

I think WAW, WAR Hazard's aspect is different from RAW. Output dependency is caused by execution time, unlike input dependency, which is a problem caused by the overlap of pipelines itself.

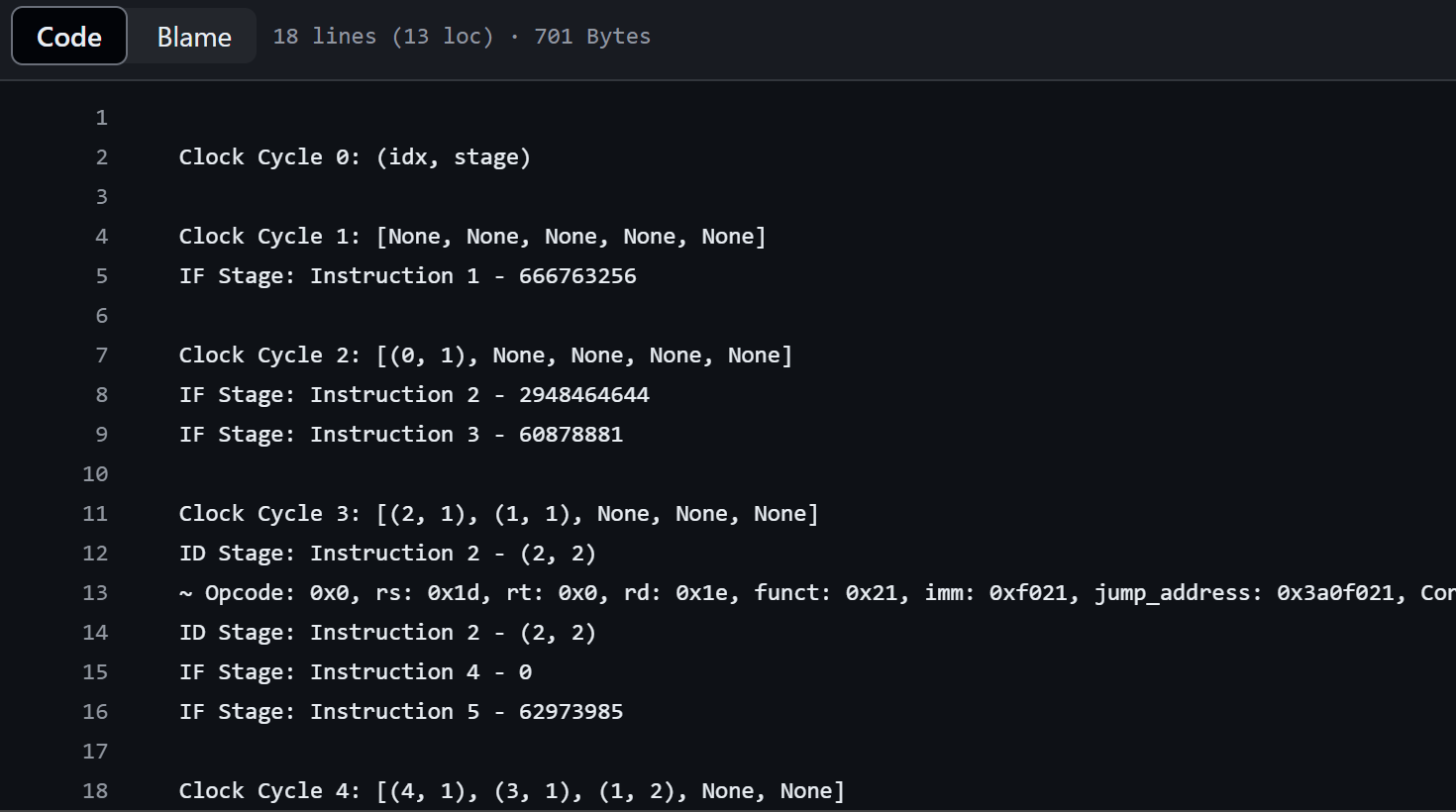

Control Hazards occur when the pipeline makes incorrect assumptions about control flow, especially with branch instructions. In MIPS pipelines, branch decisions typically occur during the execution (EX) stage, which can lead to delays if the branch outcome isn't determined early enough. To mitigate this issue, Pipeline Stalling, Branch Prediction, Delayed Branching can employed.

Data Hazards arise when instructions with data dependencies are executed in a manner that disrupts the pipeline sequence. There are three main types: RAW, WAR, WAW.

To mitigate these hazards, MIPS processors employ techniques like data forwarding (bypassing), where data is transferred directly between pipeline stages to resolve dependencies without stalling the pipeline unnecessarily. Additionally, pipeline stalling is used to ensure instructions are executed in the correct sequence when dependencies cannot be resolved immediately. Compiler optimizations such as code reordering also play a role in minimizing these hazards during program compilation, contributing to improved pipeline efficiency and performance.