기억장치 특징

기억장치 시스템을 설계하기 위해서는 용량과 액세스 속도를 고려해야한다.

전송 단위는 CPU가 한번의 기억장치 액세스에 의하여 읽거나 쓸 수 있는 비트의 수이다. 주기억장치는 단어 단위이고, 보조저장장치는 블록 단위이다.

주소지정 단위는 주소가 지정된 각 기억 장소 당 저장되는 데이터 길이로 바이트나 단어 단위이다.

기억장치 액세스

CPU가 어떤 정보를 기억장치에 쓰거나 기억장치로부터 읽는 동작이다.

- 액세스 시간 : 주소와 쓰기/읽기 신호가 도착한 순간부터 데이터 액세스가 완료되는 순간까지의 시간

- 기억장치 사이클 시간 : 액세스 시간 + 데이터 복원 시간

- 데이터 전송률 : 기억장치로부터 초당 액세스 되는 비트 수 (=(1/액세스시간)x(한번에 읽혀지는 데이터 비트수))

기억장치 액세스 유형

- 순차적 액세스 : 저장된 정보를 처음부터 순서대로 액세스

- 직접 액세스 : 액세스할 위치 근처로 직접 이동 후, 순차적 검색을 통해 최종 위치에 도달

- 임의 액세스 : 주소에 의해 직접 기억 장소를 찾아 액세스하고, 어떤 기억 장소든 액세스 시간 동일

- 연관 액세스 : 저장된 내용의 특정 비트들을 비교하여, 일치하는 내용을 액세스

기억장치 유형

- 기억장치의 제조 재료에 따른 유형

- 반도체 기억장치 : 반도체 물질인 실리콘 칩을 사용 (RAM, ROM)

- 자기-표면 기억장치 : 자화 물질로 코팅된 표면에 정보를 저장 (디스크)

- 데이터를 저장하는 성질에 따른 유형

- 휘발성 기억장치 : 전원 공급이 중단되면 내용이 지워짐 (RAM)

- 비휘발성 기억장치 : 전원 공급과 관계없는 영구 저장됨 (ROM, 디스크)

- 삭제불가능 기억장치 : 내용 변경이 불가능 (ROM)

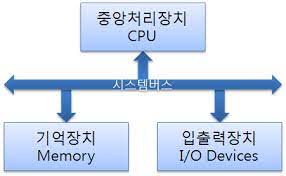

계층적 기억장치시스템

기억장치들은 속도, 용량 및 가격 측면에서 매우 다양하고 적절한 성능, 용량 및 가격의 기억장치 구성이 필요하다. 그리고 계층적 기억장치시스템은 성능 대 가격비가 훌륭하다.

액세스 속도가 높아질수록 비트당 가격은 높아지고, 용량이 커질수록 액세스 시간은 길어지고 비트당 가격은 낮아진다.

2단계 계층적 기억장치

계층적 기억장치시스템은 첫번째 계층 기억장치와 두번째 계층 기억장치로 구성된다.

첫번째 계층 기억장치는 속도는 빠르고 가격도 높다.

두번째 계층 기억장치는 속도는 느리지만 가격은 낮다.

2단계 계층적 기억장치는 원하는 데이터가 첫번째 계층 기억장치에 있다면 즉시 액세스하고, 없다면 두번째 계층의 기억장치로부터 데이터를 읽어서 첫번째 기억장치에 적재한 후 사용되는 원리를 가진다.

이는 첫번째 계층 기억장치에 데이터가 있을 확률에 따라 평균 액세스 시간이 변화한다.

지역성의 원리

지역성은 기억장치의 액세스가 몇몇 특정 영역에 집중되는 현상이다.

짧은 시간을 기준으로 보면, 프로세서가 기억장치의 한정된 몇몇 위치들을 집중적으로 액세스하면서 작업을 수행한다.

때문에 첫번째 계층의 기억장치에 대한 액세스 횟수가 두번째 계층의 기억장치에 대한 액세스보다 훨씬 더 많다.

이처럼 지역성의 원리가 적용되는 경우, 평균 기억장치 액세스 시간이 단축된다.

기억장치 계층

위 그림처럼 상위 층으로 갈수록 비트당 가격이 높아지고 용량은 감소한다. 액세스 시간을 짧아지고 CPU에 의한 액세스 빈도는 높아진다.

-

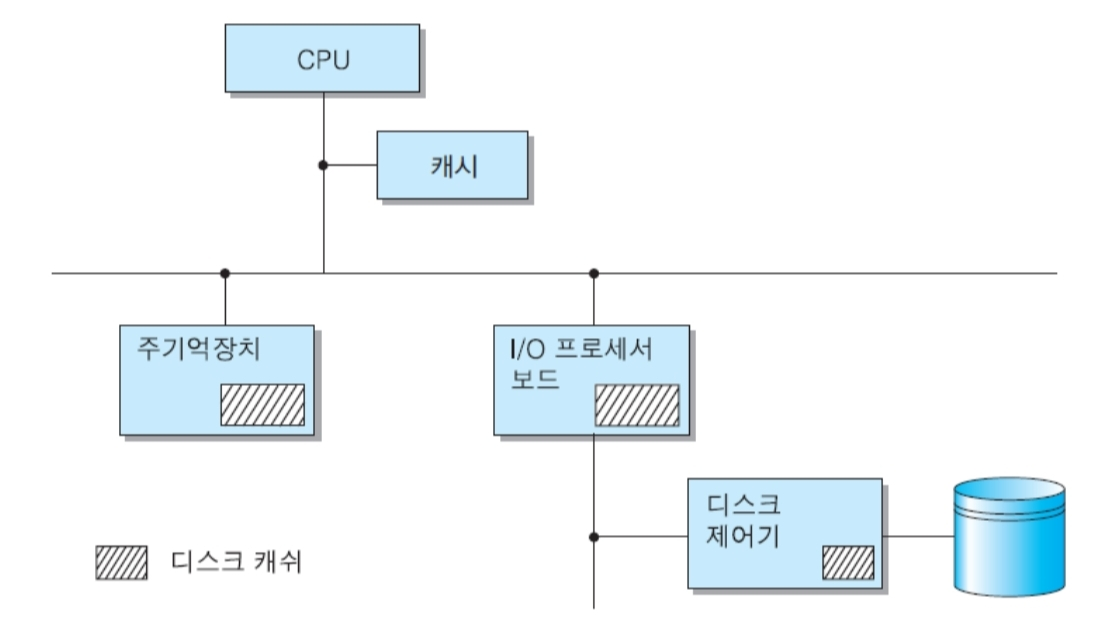

캐시 메모리 : 주기억장치의 액세스 속도가 CPU에 비해 매우 느리기 때문에 주기억장치로부터 데이터를 읽어오는 동안에 CPU가 오랫동안 기다려야하므로, 성능 보완을 위해 CPU와 주기억장치 사이에 설치하는 고속의 반도체 기억장치

-

디스크 캐시 : 디스크와 주기억장치의 액세스 속도 차이를 줄이기 위하여 그 사이에 설치하는 반도체 기억장치로 주기억장치로부터 디스크로 읽혀나갈 정보들을 일시적으로 저장하는 버퍼 역할을 함

반도체 기억장치

RAM

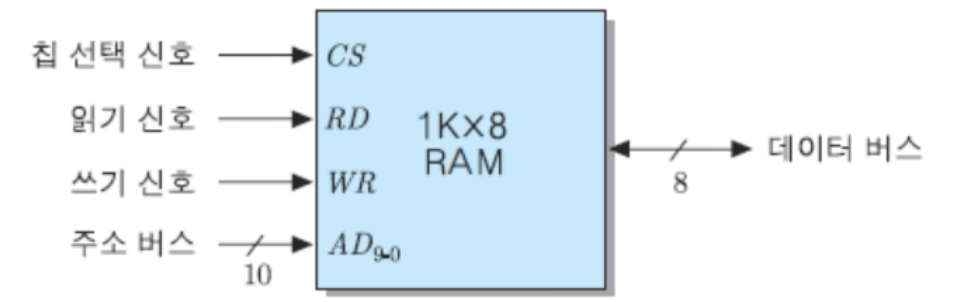

RAM은 임의 액세스 방식으로 반도체 직접회로 기억장치이다. 데이터 읽기와 쓰기 모두 가능하고 휘발성 메모리이다.

위 그림은 1K x 8 RAM 칩의 블록선도이다.

RD 신호가 주어지면 읽기 동작을하고, WR 신호가 주어지면 쓰기 동작을 한다.

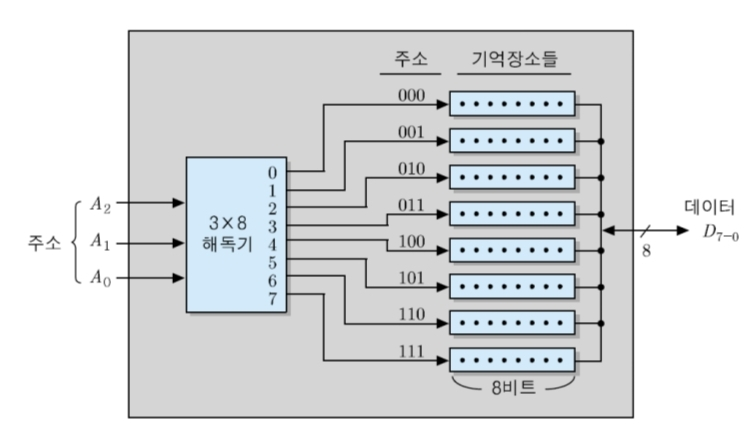

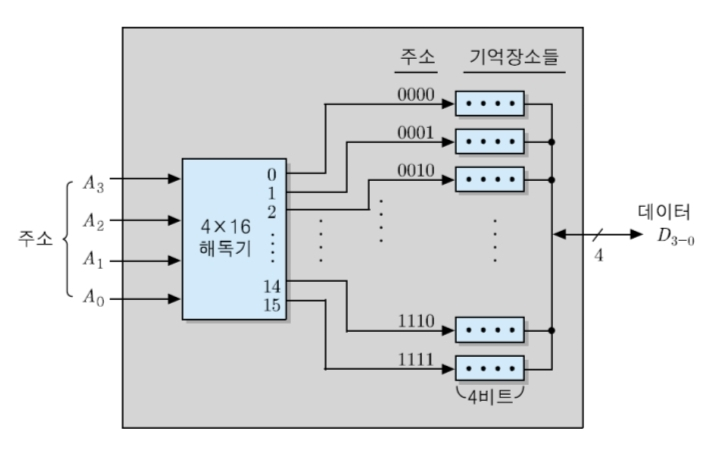

RAM 내부조직

8x8비트의 램은 8비트로 이루어진 8개의 기억장소로 구성되어 있다. 데이터 입출력 선의 수는 8개이고 주소선은 3개이다.

마찬가지로 16x4비트의 램은 4비트로 이루어진 16개의 기억장소들로 구성되어있다. 데이터의 입출력 선의 수는 4개이고 주소선은 4개이다.

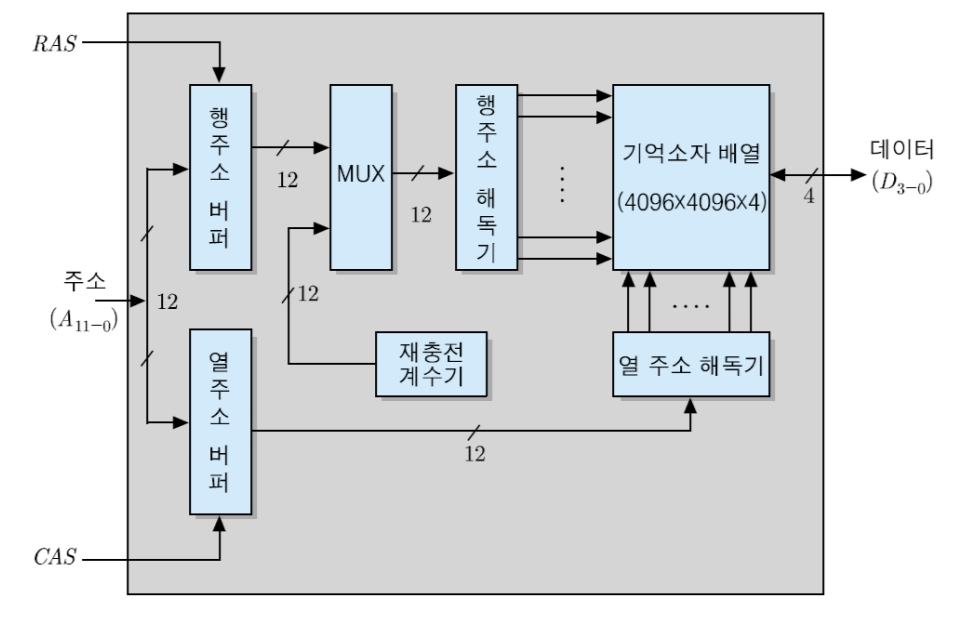

16M x 4비트의 램은 기억 소자들이 4096(행)x4096(열)x4비트의 형태로 배열되어 있다. 각 기억장소는 4개의 데이터 비트를 저장하고 주소선은 24개를 필요로 하는데 RAS(Row Address Strobe)신호와 CAS(Column Address Strobe)신호를 이용하여 실제 입력되는 주소 선은 12개만 되도록한다.

제조 기술에 따른 RAM 분류

- DRAM

- 캐패시터(capacitor)에 전하를 충전하는 방식으로 데이터를 저장하는 기억 소자들로 구성

- 데이터의 저장 상태를 유지하기 위해서 주기적인 재충전 필요

- 집적밀도가 높으며, 같은 용량의 SRAM보다 가격이 저렴

- 용량이 큰 주기억장치로 사용

DRAM은 위 그림과 같이 읽기 동작을한다.

- SRAM

- 기억소자로서 플립 플롭 이용

- 전력 공급 되는 동안에는 재충전 없이 데이터 유지 가능

- 집적밀도가 낮음

- DRAM보다 빨라 높은 속도가 필요한캐시 기억장치로 사용

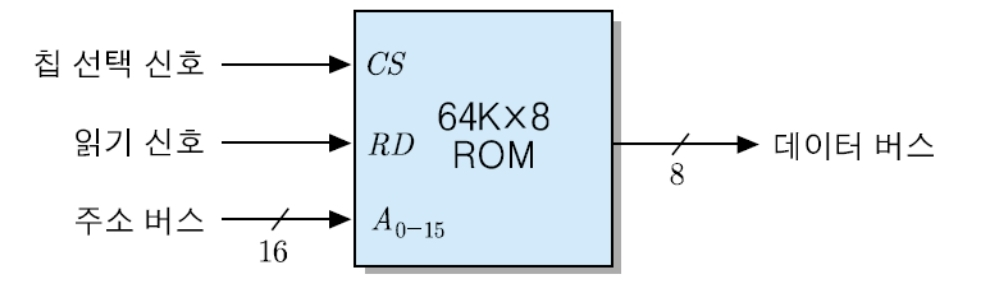

ROM

읽는 것만 가능한 (Read Only Memory) 영구 저장이 가능한 반도체 기억장치이다.

ROM은 아래와 같은 내용을 저장한다.

- 시스템 초기화 및 진단 프로그램 (BIOS)

- 빈번히 사용되는 함수들을 위한 서브루틴들

- 제어 유니트의 마이크로프로그램

ROM 종류

-

PROM(Programmable ROM) : 사용자가 한 번 쓰는 것이 가능한 ROM

-

EPROM(Erasable Programmable ROM) : 자외선을 이용하여 내용을 지울 수 있는 ROM으로 여러번 쓰는 것이 가능한 ROM

-

EEPROM(Electrically Erasable PROM) : 전기적으로 내용을 지울 수 있는 ROM으로 데이터 갱신 횟수가 제한적임 (수만번)

-

플래쉬 메모리(Flash Memory)

- 페이지 단위로 읽기/쓰기 가능 (NAND형)

- 블록 단위 삭제 (NAND형)

- EEPROM에 비해 삭제 시간 빠르고 집적 밀도 높음

- 삭제 횟수 제한적

- 하드 디스크를 대체하는 SSD의 구성요소

기억장치 모듈의 설계

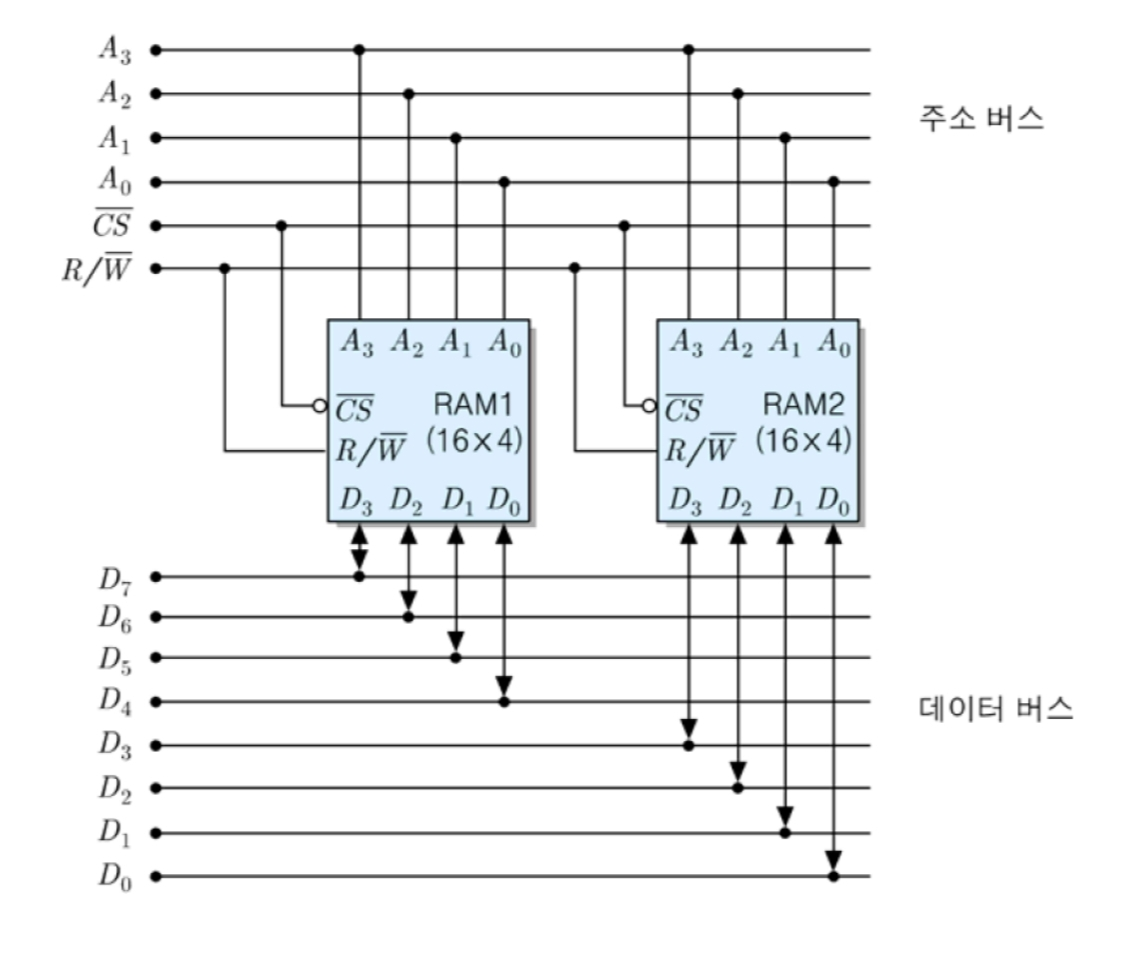

기억장치 칩의 데이터 I/O 비트 수가 단어의 길이보다 적은 경우에는 여러 개의 칩들을 병렬로 접속하여 기억장치 모듈을 구성한다.

N비트의 단어길이와 B비트의 I/O 비트 수라면 N/B개의 칩들을 병렬 접속한다.

필요한 기억장소 수가 각 기억장치 칩의 기억장소 수보다 많은 경우에는 여러 개의 칩들을 직렬로 접속하여 기억장치 모듈을 구성한다.

기억장치 모듈 조직

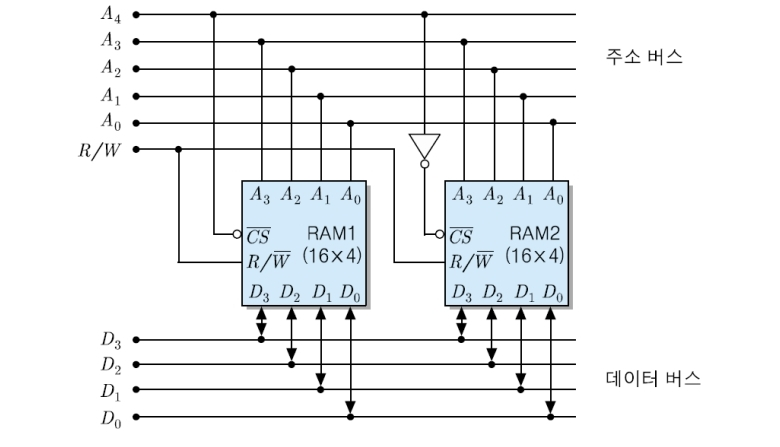

16x4비트 RAM칩들을 이용한 16x8비트의 기억장치 모듈은 아래와 같다.

4개의 주소 선과 16개의 기억소자로 이루어진 RAM 2개가 병렬로 연결되어있다.

16x4비트 RAM칩들을 이용한 32x4비트 기억장치 모듈은 아래와 같다.

4개의 주소 선과 16개의 기억소자로 이루어진 RAM 2개가 직렬로 연결되어있다.