논리 회로

조합 회로

조합회로는 n개의 입력을 받아 m개의 출력을 내는 함수와 같은 역할을 하는 회로이다. 출력값은 입력값의 영향만 받기 때문에 입력에 대한 출력이 동일하다.

-> n에 5가 들어오면 언제나 출력은 10이 나온다.

순차 회로

순차회로는 입력을 받은 후 저장 값을 참고하여 출력을 내는 회로이다. 저장 값에 따라 출력이 달라지므로 입력에 대한 출력이 동일하다고 말할 수 없다.

ex) 저금통에 100원을 넣으면 총합은? -> 기존의 금액 + 100이므로 출력이 달라진다.

회로 분석

회로도로부터 이 회로가 어떤 기능을 수행하는지를 밝혀내는 것을 회로 분석이라고 한다. 회로는 진리표와 논리 식으로 나타낼 수 있다. 또한 논리 식이 있으면 회로를 그릴 수 있다. 추가로 논리 식의 규칙들과 K-map을 알고 있으면 간략화가 가능하다.

모든 입력에 대해서 모든 출력을 말할 수 있으면 회로 분석을 했다고 말할 수 있다.

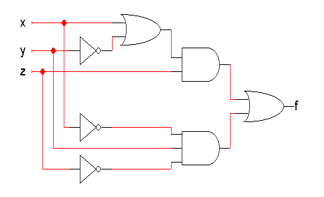

이런 회로가 있다고 가정하자.

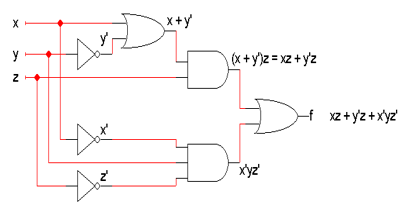

식으로 나타내기

회로의 AND와 OR연산을 식으로 간단하게 나타낼 수 있다. 또한 논리 식의 성질과 규칙들을 활용해서 간략화시킬 수 있다.

이 과정을 통하면

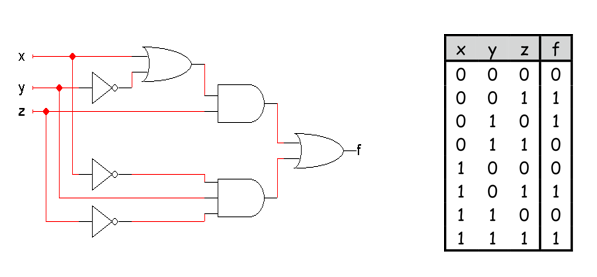

진리표로 나타내기

입력의 의 출력에 대한 진리표를 만들어서 나타낼수도 있다. 이 과정은 간단하지만 시간이 오래 걸릴 수 있다. 또한 n이 커질수록 걸리는 시간이 기하급수적으로 늘어난다.

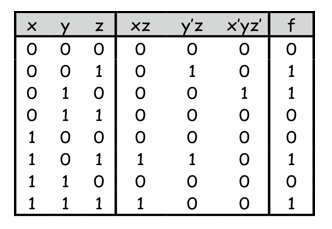

식을 가지고 진리표로 나타내기

내가 만약 회로에 대한 논리 식을 가지고 있다면 진리표를 쉽게 나타낼 수 있다.

- 일단 회로를 SOP(Sum of Product)나 POS(Product of Sum) 형태로 나타낸다. 이렇게 하는 이유는 진리표를 작성한뒤 출력에서 AND나 OR연산만 하면 되기 때문에 간단해진다.

- 각각의 식에 해당하는 진리표를 작성한다.

- SOP면 OR연산을, POS면 AND연산을 수행한다.

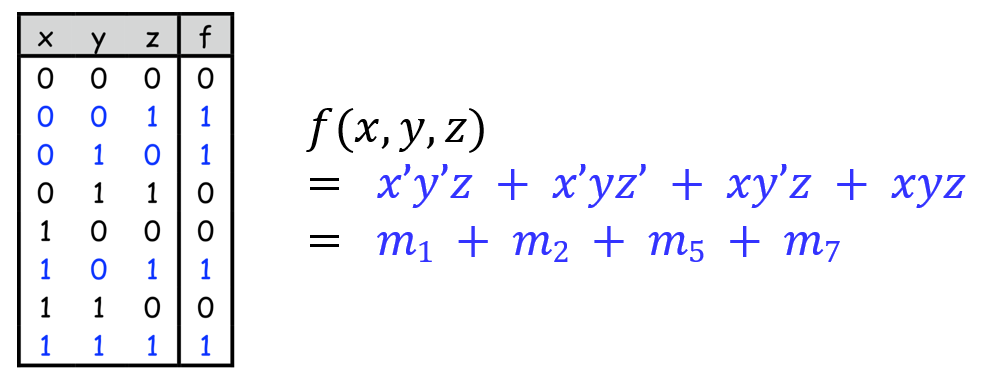

진리표를 가지고 식으로 나타내기

내가 만약 회로에 대한 진리표를 가지고 있다면 식을 쉽게 나타낼 수 있다.

- 진리표의 각 minterm을 확인한다.

- minterm들을 SOP의 형태로 나타낸다.

- K-map같은 간략화 과정을 거친다.