verilog code:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0] a_1 = a[15:0];

wire [15:0] b_1 = b[15:0];

wire [15:0] a_2 = a[31:16];

wire [15:0] b_2 = b[31:16];

wire c_in = 1'b0;

wire [15:0] sum_1;

wire [15:0] sum_2;

wire cout_to_cin;

wire cout;

add16 add16_1(a_1,b_1,c_in,sum_1,cout_to_cin);

add16 add16_2(a_2,b_2,cout_to_cin,sum_2,cout);

assign sum = {sum_2[15:0],sum_1[15:0]};

endmoduleResult:

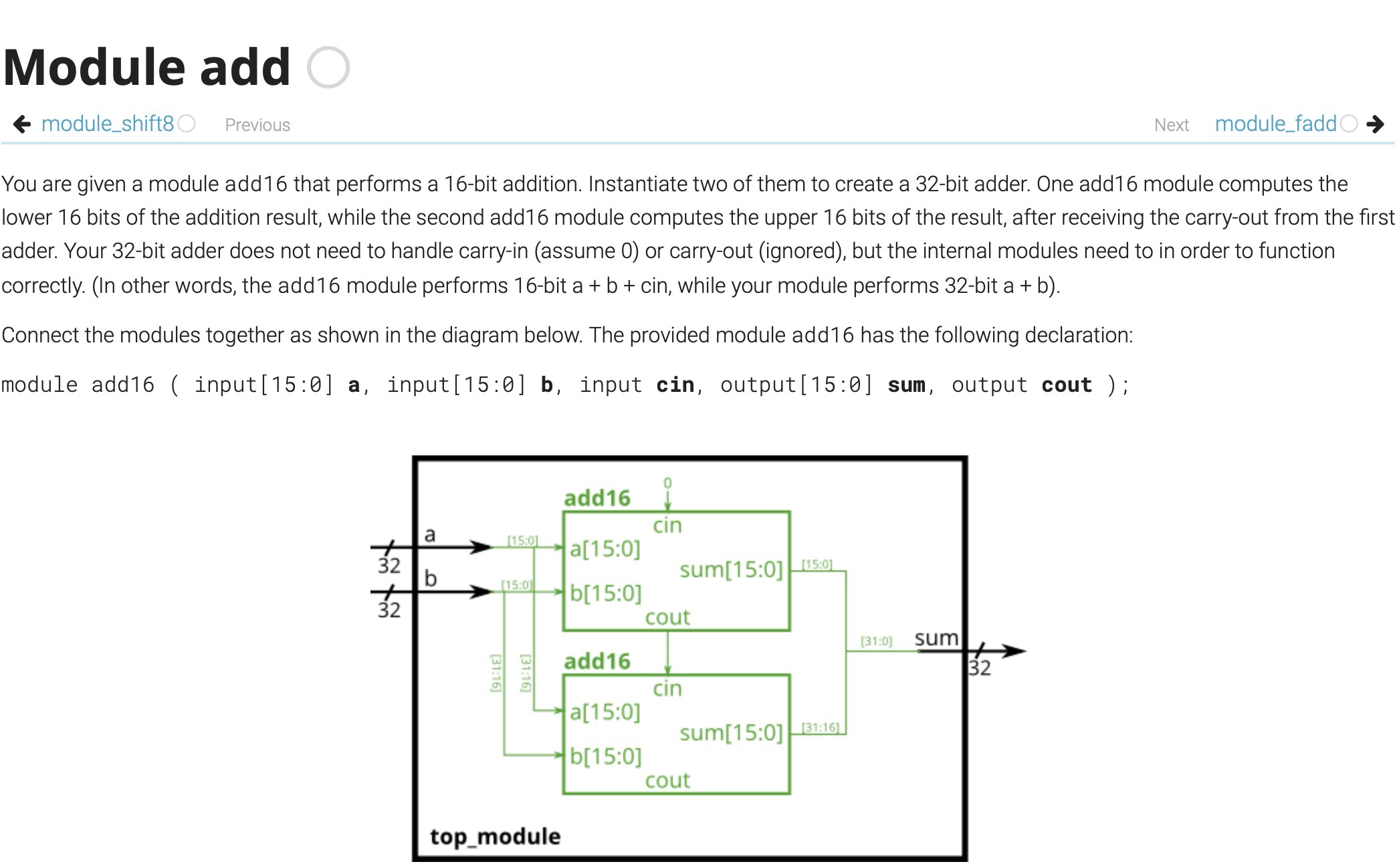

32bit input a,b 를 받아서 각각 16bit로 분할.

각각 16bit adder module로 들어감.

연산된 결과를 concatenate 해서 output으로 나감.

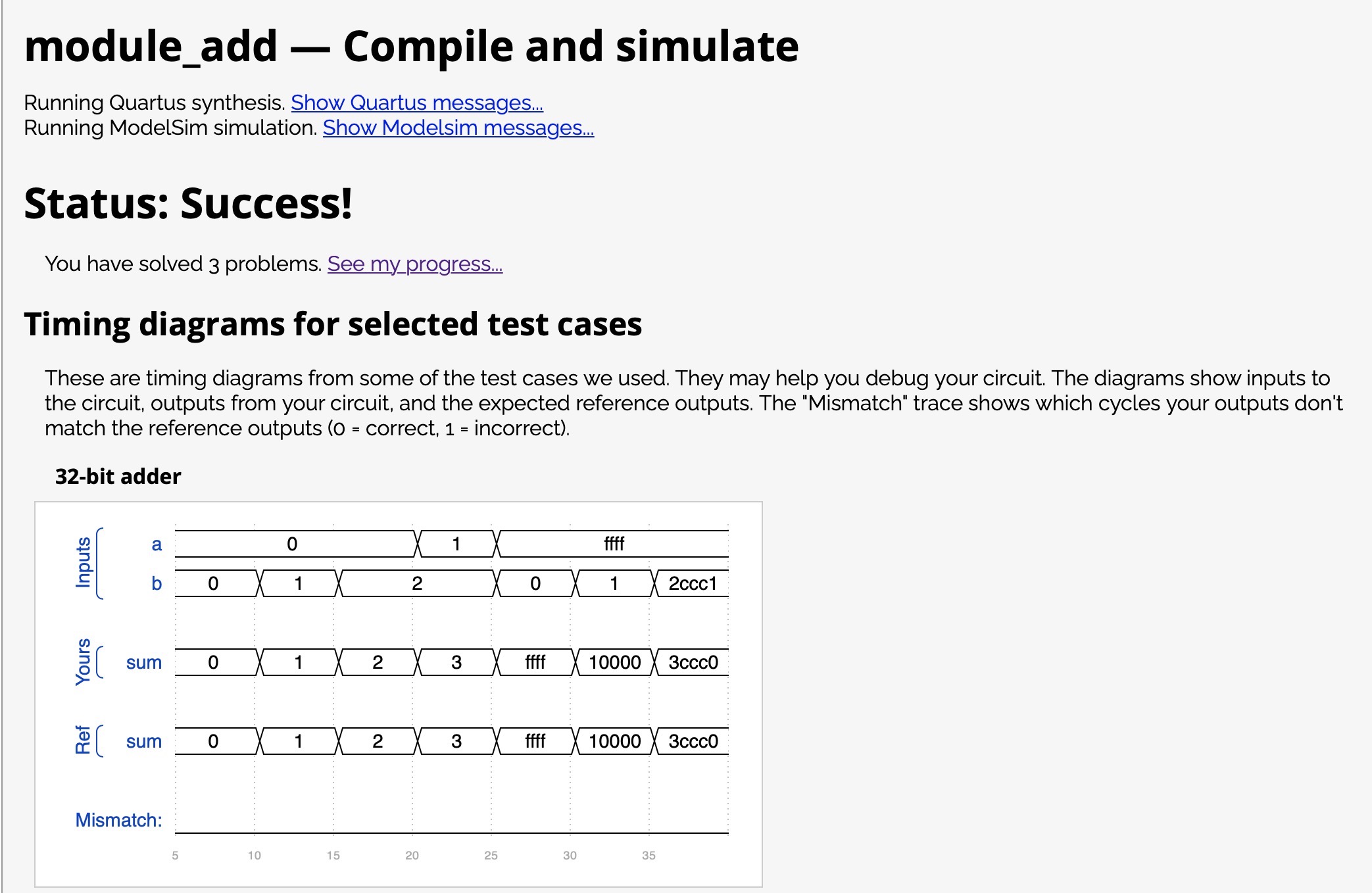

- wire 선언시 꼭 벡터화 확인하기

- 모듈 인터페이스에 wire 꽂을 때 그냥 wire 이름만 넣어줘도 됨.

- concat 할때도 필요한 vector을 명시해주어야됨. MSB->LSB 순도 잊지 말기.