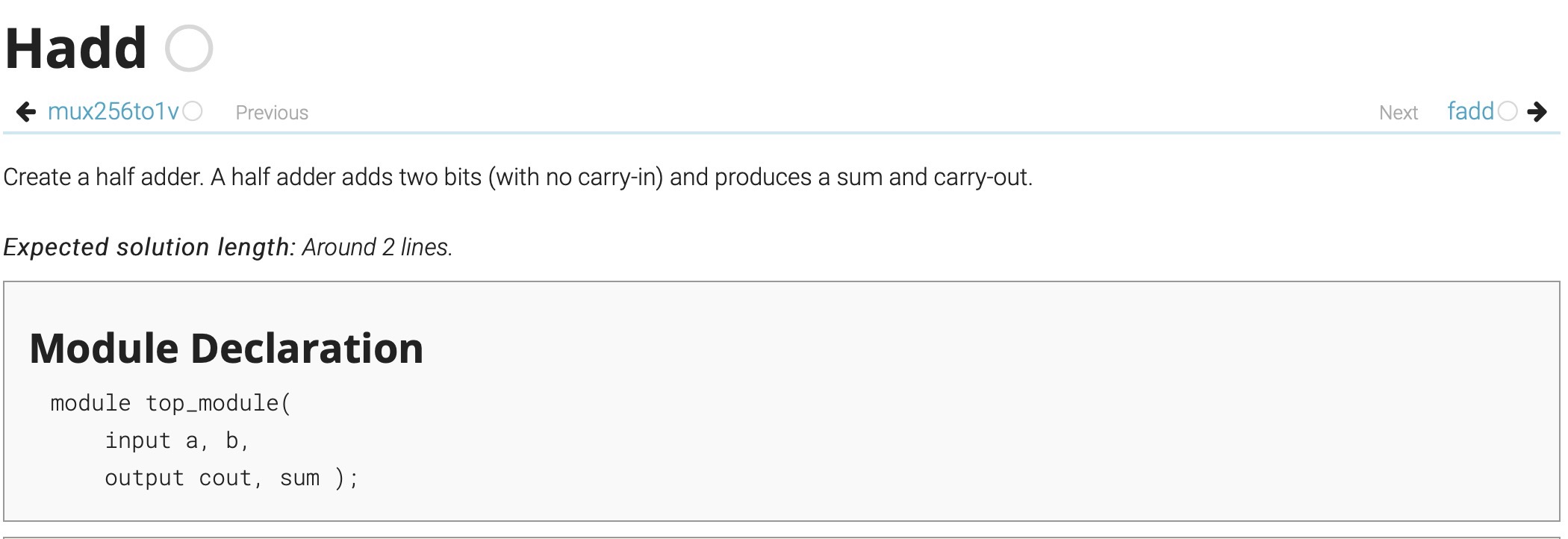

verilog code:

module top_module(

input a, b,

output cout, sum );

and(cout,a,b);

xor(sum,a,b);

endmoduleresult:

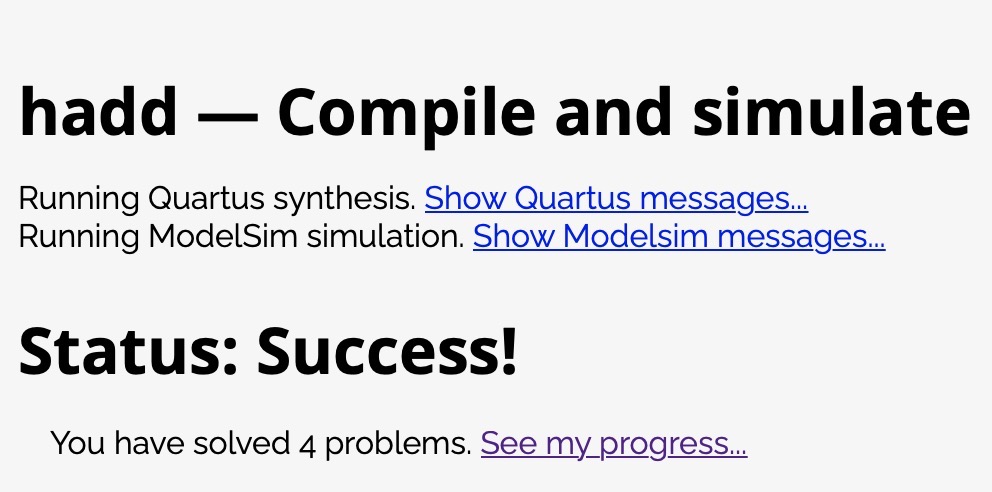

half adder 의 gate level modeling 을 해봤다.

DC로 합성했을때 라이브러리를 통해서 나온 결과물만 봐왔지, 직접 gate level modeling을 해본것은 처음이다.

어디선가 설명글을 봤는데,

1. 간단한 회로

2. 꼭 이런 gate 구성으로 나와줘야한다

할때 gate level modeling을 쓴다고 본것같다.

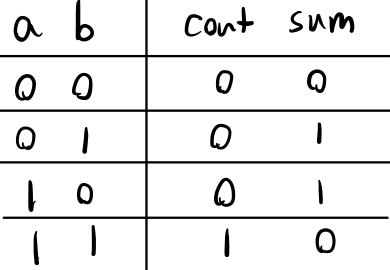

간단히 Truth table을 만들어서 cout은 and, sum을 xor 로 나와야한다는걸 도출했다.

gate level modeling을 할때 유의할점:

1. gate의 인자는 output,input 순으로 들어간다. (ex: and(cout,a,b))

2. input, output 은 default가 wire이므로 그냥 인자에 넣어도 된다.